物理综合的设计流程研究 2.3.4读入RTL硬件描述语言 读入你要综合的RTL HDL文件 ◆读入Verilog文件:read_verilog filename ◆读入VHDL文件: read vhdl filename 2.3.5建立普通网表 ◆独立于工艺的网表文件必须在读入RTL文件后建立 ◆建立普通网表的命令是: do build generic 或者dobu(简写形式) 建立普通网表的图形界面如图2.4所示: 10四 回☒ Fie Edt Mev Comnancs Fegerts Wirdow Hep 日¥hsQ中白4hgPa4rees cacence Set Target Te:hnolgy. Modles Var Laad DCL Rules HDL Td Corstrants Schematic Listib 日4dDa4Rue Nor-☒尚X图美1I▣ 图67V 2(o) i6et Chedc Netlist oduep2pnua21是In 图113 Ches Tiing (o) 3na0t01g3n21.67'(Pe-700. ashell[6]> 图2.4建立普通网表 ◆do build generic命令 ◇产生Control Data Flow Graphs:控制数据流图表(CDFGs) ◇进行很好程度的优化 ◇进行资源分配 ◇对所有在源文件中定义的模块产生分级的网表。(使用ATL单元和ACL功能块) 2.3.6设定约束 ◆对Ambit综合软件,约束定义了芯片的外界。 ◆对于时序电路,你必须定义一个时钟。 ◆当输入到来和需要输出时定义。 ◆定义输入和输出的强度和负载。 2.3.7设置当前模块和顶层时序模块 ◆使用这个命令,相对于当前模块约束被置于设计对象上: set_current_module mod_name 10

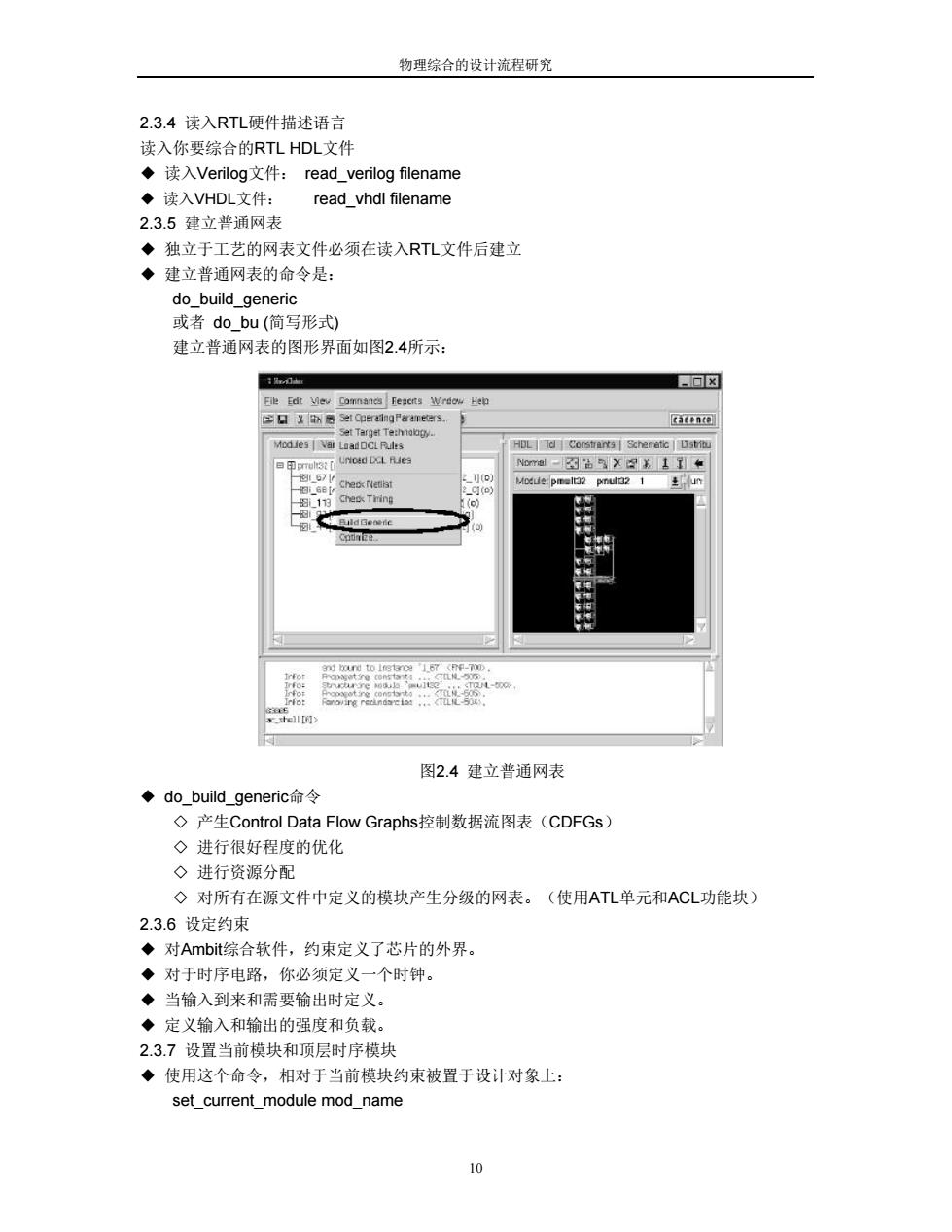

物理综合的设计流程研究 2.3.4 读入RTL硬件描述语言 读入你要综合的RTL HDL文件 ◆ 读入Verilog文件: read_verilog filename ◆ 读入VHDL文件: read_vhdl filename 2.3.5 建立普通网表 ◆ 独立于工艺的网表文件必须在读入RTL文件后建立 ◆ 建立普通网表的命令是: do_build_generic 或者 do_bu (简写形式) 建立普通网表的图形界面如图2.4所示: 图2.4 建立普通网表 ◆ do_build_generic命令 ◇ 产生Control Data Flow Graphs控制数据流图表(CDFGs) ◇ 进行很好程度的优化 ◇ 进行资源分配 ◇ 对所有在源文件中定义的模块产生分级的网表。(使用ATL单元和ACL功能块) 2.3.6 设定约束 ◆ 对Ambit综合软件,约束定义了芯片的外界。 ◆ 对于时序电路,你必须定义一个时钟。 ◆ 当输入到来和需要输出时定义。 ◆ 定义输入和输出的强度和负载。 2.3.7 设置当前模块和顶层时序模块 ◆ 使用这个命令,相对于当前模块约束被置于设计对象上: set_current_module mod_name 10

物理综合的设计流程研究 设置当前模块的图形界面如图2.5所示: s日☒ t量tMe6 arc tepats yurde 深▣闲巴K国AB回P NErLIn Vutns Dtieel OL Tal Co性|ahe Click mouse @二D日号s4 right button 71281 a 0cn9净c sDen1M到 图 图2.5设置当前模块 ◆顶层时序模块用来识别顶层用作时序的模块。所有时序约束通过这个命令在其模型里申请: set_top_timing_module mod_name 2.3.8定义时钟 两个步骤 ◆首先要定义一个理想的时钟 set_clock IDEAL CLOCK-period 20.0-wave (0 10} ◆然后你必须使一个时钟端口和你的理想时钟联合起来 set_clock_arrival_time-clock IDEAL CLOCK \-rise 0-fall 10 clk 2.3.9设置数据到达和需要的时间 ◆使用这个命令来设置数据到达时间: set data arrival time 0.0-clock lideal_clock [find-port-noclock-input*] 设置数据到达时间的图形界面如图2.6所示: 1.Select the ideal clock El Ec yrv Crm中i用ts ndav th 场日x地X品泰口新 r可 HDL TE Correrares s 口P02阅 L的A只3D四 2.Specify the time nt imad DD0000D D0000D DD0000D C00000 1 11 5-19 图2.6设置数据到达时间 11

物理综合的设计流程研究 设置当前模块的图形界面如图2.5所示: 图2.5 设置当前模块 ◆ 顶层时序模块用来识别顶层用作时序的模块。所有时序约束通过这个命令在其模型里申请: set_top_timing_module mod_name 2.3.8 定义时钟 两个步骤 ◆ 首先要定义一个理想的时钟 set_clock IDEAL_CLOCK –period 20.0 –wave {0 10} ◆ 然后你必须使一个时钟端口和你的理想时钟联合起来 set_clock_arrival_time –clock IDEAL_CLOCK \–rise 0 –fall 10 clk 2.3.9 设置数据到达和需要的时间 ◆ 使用这个命令来设置数据到达时间: set_data_arrival_time 0.0 –clock \ideal_clock [find –port –noclock –input *] 设置数据到达时间的图形界面如图2.6所示: 图2.6 设置数据到达时间 11