研究生学阮论文写作方法 子科技大臀 撰写摘要时的注意事项 冬使用标准术语,尽量不用非通用缩写名词; “摘要”(以及最后的“结论”)内容对评审专家快速把握全文 研究内容及成果贡献等具有重要意义,是专家写评阅意见是重要 参考。因此在撰写摘要时应对研究成果的创新性和价值做出准确 的自我评价,注意实事求是,不可过度夸大。 摘要应该在正文完成后撰写,并需要反复修改,逐字逐句琢磨。 硕士研究生学位论文摘要控制在1页以内,博士研究生学位论文 摘要控制在2页以内。 17

电子科技大学 17 3 研究生学位论文写作方法 撰写摘要时的注意事项 使用标准术语,尽量不用非通用缩写名词; “摘要”(以及最后的“结论”)内容对评审专家快速把握全文 研究内容及成果贡献等具有重要意义,是专家写评阅意见是重要 参考。因此在撰写摘要时应对研究成果的创新性和价值做出准确 的自我评价,注意实事求是,不可过度夸大。 摘要应该在正文完成后撰写,并需要反复修改,逐字逐句琢磨。 硕士研究生学位论文摘要控制在1页以内,博士研究生学位论文 摘要控制在2页以内

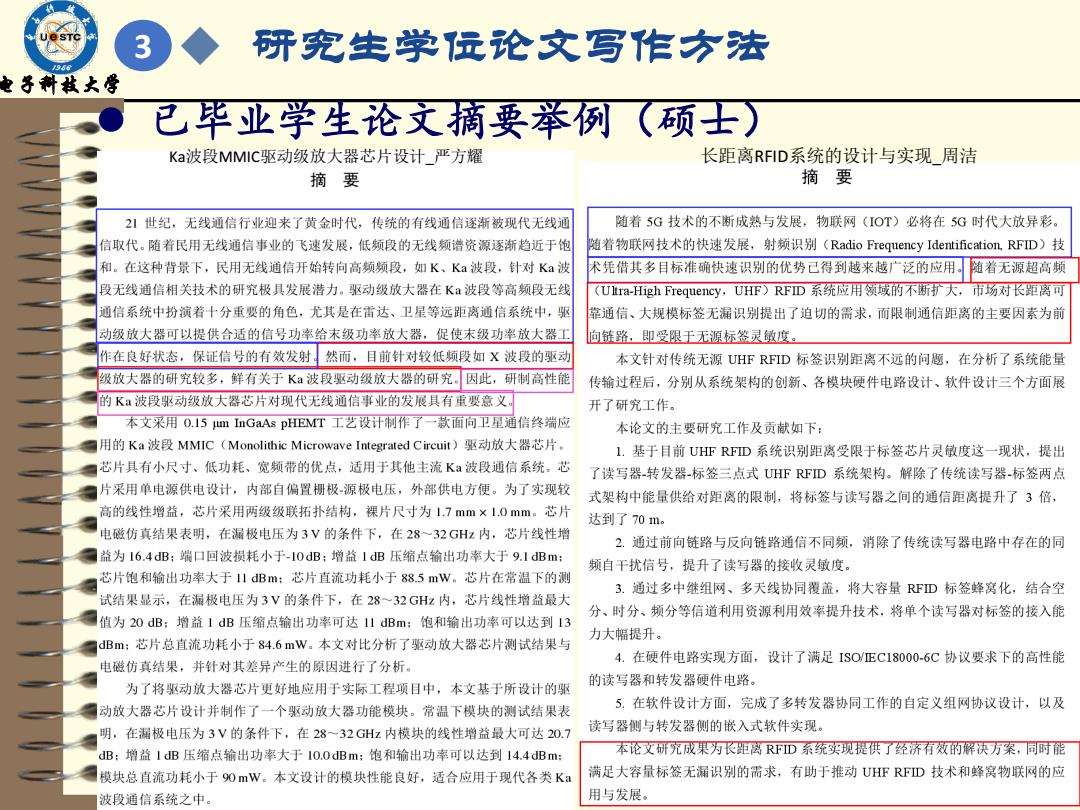

研竞生学阮论文写作方法 子斜技大骨 已毕业学生论文摘要举例 (硕士) Ka波段MMIC驱动级放大器芯片设计严方耀 长距离RFID系统的设计与实现周洁 摘要 摘要 21世纪,无线通信行业迎来了黄金时代, 传统的有线通信逐渐被现代无线通 随着5G技术的不断成熟与发展,物联网(IOT) 必将在5G时代大放异彩。 信取代。随着民用无线通信事业的飞速发展,低频段的无线频谱资源逐渐趋近于饱 随着物联网技术的快速发展,射频识别(Radio Frequency Identification.RFID)技 和。在这种背景下,民用无线通信开始转向高频频段,如K、Ka波段,针对Ka波 术凭借其多目标准确快速识别的优势己得到越来越广泛的应用。 随着无源超高频 段无线通信相关技术的研究极具发展潜力。驱动级放大器在K波段等高频段无线 (Ura-High Frequency.,UHF)RFD系统应用领域的不断扩大, 市场对长距离可 通信系统中扮演着十分重要的角色,尤其是在雷达、卫星等远距离通信系统中,驱 靠通信、大规模标签无漏识别提出了迫切的需求,而限制通信距离的主要因素为前 动级放大器可以提供合适的信号功率给末级功率放大器,促使末级功率放大器工 向铣路,即受限于无源标签灵敏度。 作在良好状态,保证信号的有效发射然而,目前针对较低频段如X波段的驱动 本文针对传统无源UHF RFID标签识别距离不远的问题,在分析了系统能量 级放大器的研究较多,鲜有关于K:波段驱动级放大器的研究。因此,研制高性能 传输过程后,分别从系统架构的创新、各模块硬件电路设计、软件设计三个方面展 的Ka波段驱动级放大器芯片对现代无线通信事业的发展具有重要意义。 开了研究工作 本文采用O.15 m InGaAs pHEMT工艺设计俐作了一款面向卫星通信终端应 本论文的主要研究工作及贡献如下: 用的Ka波段MMIC(Monolithic Microwave Integrated Circuit)驱动放大器芯片, 1.基于目前UHF RFID系统识别距离受限于标签芯片灵敏度这一现状,提出 芯片具有小尺寸、低功耗、宽频带的优点,适用于其他主流Ka波段通信系统。芯 了读写器转发器-标签三点式UHF RFID系统架构。解除了传统读写器-标签两点 片采用单电源供电设计,内部自偏置栅极源极电压,外部供电方便。为了实现较 式架构中能量供给对距离的限制,将标签与读写器之间的通信距离提升了3倍, 高的线性增益,芯片采用两级级联拓扑结构,裸片尺寸为1.7mm×1.0mm。芯片 达到了70m。 电磁仿真结果表明,在漏极电压为3V的条件下,在28~32GHz内,芯片线性增 2.通过前向链路与反向链路通信不同频,消除了传统读写器电路中存在的同 益为16.4dB:端口回波损耗小于-10dB:增益1dB压缩点输出功率大于9.1dBm: 频自干扰信号,提升了读写器的接收灵敏度。 芯片饱和输出功率大于11dBm:芯片直流功耗小于88.5mw。芯片在常温下的测 3.通过多中继组网、多天线协同覆盖,将大容量RFD标签蜂窝化,结合空 试结果显示,在漏极电压为3V的条件下,在28~32GHz内,芯片线性增益最大 分、时分、频分等信道利用资源利用效案提升技术,将单个读写器对标签的接入能 值为20dB:增益1dB压缩点输出功率可达11dBm:饱和输出功率可以达到13 力大幅提升。 dBm:芯片总直流功耗小于84.6mw。本文对比分析了驱动放大器芯片测试结果与 4.在硬件电路实现方面,设计了满足ISO/正C18000-6C协议要求下的高性能 电磁仿真结果,并针对其差异产生的原因进行了分析。 为了将驱动放大器芯片更好地应用于实际工程项目中,本文基于所设计的驱 的读写器和转发器硬件电路。 动放大器芯片设计并制作了一个驱动放大器功能模块。常温下模块的测试结果表 5.在软件设计方面,完成了多转发器协同工作的自定义组网协议设计,以及 明,在漏极电压为3V的条件下,在28~32GHz内模块的线性增益最大可达20.7 读写器侧与转发器侧的嵌入式软件实现。 dB:增益1dB压缩点输出功率大于10.0dBm:饱和输出功率可以达到14.4dBm: 本论文研究成果为长距离RFD系统实现提供了经济有效的解决万案,同时能 模块总直流功耗小于90mW。本文设计的模块性能良好,适合应用于现代各类K 满足大容量标签无漏识别的需求,有助于推动UHF RFID技术和蜂窝物联网的应 波段通信系统之中。 用与发展

电子科技大学 18 3 研究生学位论文写作方法 已毕业学生论文摘要举例(硕士) Ka波段MMIC驱动级放大器芯片设计_严方耀 长距离RFID系统的设计与实现_周洁

研竞生学阮论文写作方法 子科技大臀 已华业学生论文摘要举例硕士) 面向5G移动通信的天线技术研究及设计方小川 摘要 随着通信技术的不断发展,第五代移动通信技术(5G)的商用已经近在眼前。 3介绍了一种可用于5G移动通信阵列天线的去耦合方法,并以上述加载有金 作为移动通信中最为重要的功能组件,面向5G通信应用的手机天线与基站天线的 属背板的小型化天线为基础,组成面向5G移动通信应用的2×4阵列,研究了该 技术研究与设计成为近年来的热点。纵观国内外5G天线的研究现状,以及大规模 阵列在采用去耦合技术前后的不同阵列性能结果:该天线的测试结果显示,其工 MIMO阵列(Massive MIMO)技术的相关要求,面向5G移动通信的天线应具有 作带宽达到了2.05-3.5GHz,总增益大于12dBi。 高增益、小型化、宽频段及高隔离度等技术特征,以满足5G通信的高传输速率、 本文所设计的天线及阵列,在带宽上实现了覆盖了5G中频段及WiFi/WiMax 波束智能赋形、波束能量聚集等功能。根据国家工信部的最新规定,5G移动通信 的中频段被划定在3.3GHz-3.5GHz及4.8GHz-5.0GHz:在5G预商用的初始阶段, 频段,在增益上实现了单天线大于4dBi,阵列增益大于12dBi,且阵列天线隔离 4G移动通信以及Wi-Fi,WMAX等目前广泛应用的移动通信方式不会立即退出市 度大于15dB的性能,符合5G移动通信中频段的天线设计要求,且对于现有的常 场,因此研究一款可以同时兼容5G频段及现存常用通信频段(Wi-Fi/WMAX)的 用无线通信频段具有良好的兼容性。本文对于面向5G移动通信的天线所进行的 宽带天线及阵列具有十分重要的意义。 基于以上应用需求,本文提出并设计了 系列研究和设计,在考虑到天线需要具有良好的Massive MIMO波束赋形所需的高 款可以同时支持5G微波频段及Wi-Fi/WiMAX频段,工作在2.4-3.5GHz的小型化 增益,高隔离度的特征的同时,也考虑到了5G通信及现有通信之间必不可少的过 单极子天线及其阵列,并针对5G通信对于天线及阵列的技术要求对本文设计天线 渡,因此,具有十分重要的价值和意义。 的性能进行了深入研究与讨论。 本论文主要的研究工作及创新贡献如下: 1.介绍了应用于5G通信的天线相关背景、关键技术、指标要求;结合单极子 天线及共面波导天线的基础理论,设计了一款可覆盖5G中频段及WFi/WiMax频 段的平面单极子天线,对该天线的仿真及测试结果进行分析,并研究了加载金属 背板对该天线相关性能的影响:最后经测试,该天线的带宽达到了2.4-3.5GHz,增 益大于ldBi。 2针对上述共面波导(CPw)馈电平面单极子天线尺寸偏大等不足,提出了天 线小型化的具体实现方法,详细分步骤地研究单极子天线小型化设计过程及其对 天线性能的影响:给出了工作在相同频段的,采用同样馈电方式(CPW)馈电的 小型化平面单极子天线的仿真及测试结果,测试结果显示,工作带宽为 2.35-3.55GHz,增益达到了1dBi:并研究了小型化之后的天线加载金属背板对于该 19 天线相关性能的影响

电子科技大学 19 3 研究生学位论文写作方法 已毕业学生论文摘要举例(硕士) 面向5G移动通信的天线技术研究及设计_方小川

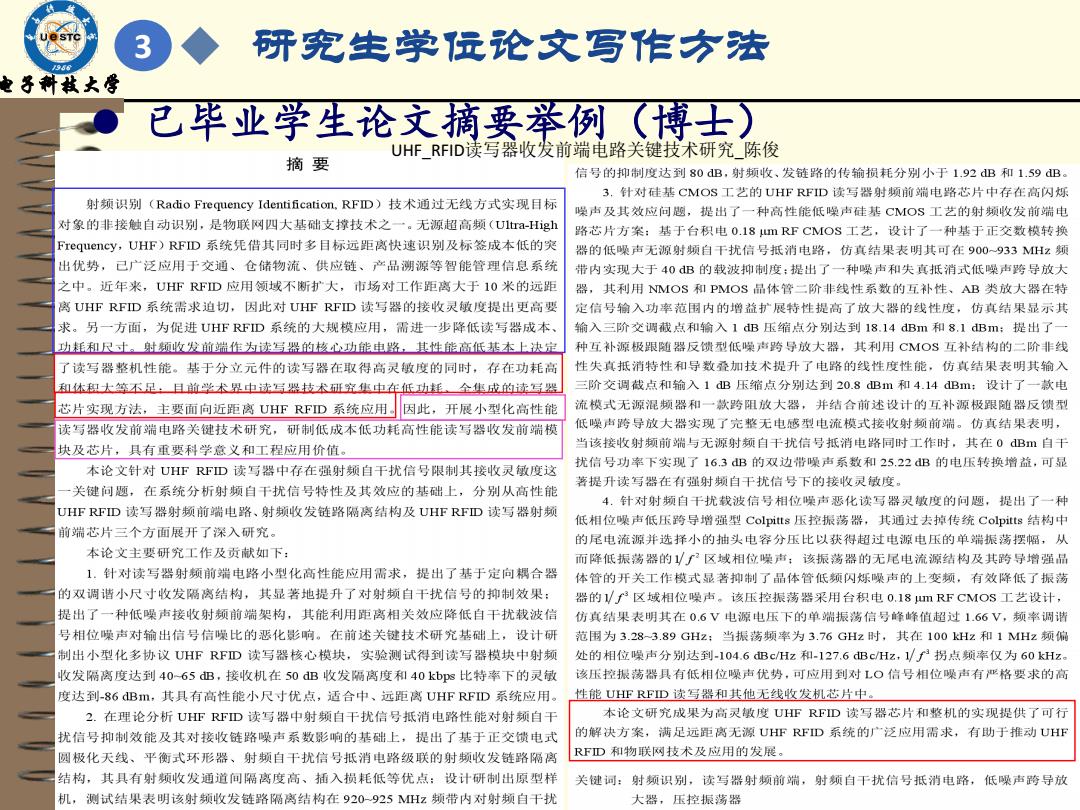

研究生学阮论文写作方法 子大骨 已毕业学生论文摘要举例(博士) UHF_RFID读写器收发前端电路关键技术研究_陈俊 摘要 信号的抑制度达到80dB,射频收、发链路的传输损耗分别小于1.92dB和1.59dB。 3,针对硅基CMOS工艺的UHF RFID读写器射频前端电路芯片中存在高闪烁 射频识别(Radio Frequency Identification,RFD)技术通过无线方式实现日标 噪声及其效应问题,提出了一种高性能低噪声硅基CMOS工艺的射频收发前端电 对象的非接触自动识别,是物联网四大基础支撑技术之一。无源超高频(U1r-Hgh 路芯片方案:基于台积电0.18 m RF CMOS工艺,设计了一种基于正交数模转换 Frequency,UHF)RFID系统凭借其同时多目标远距离快速识别及标签成本低的突 器的低噪声无源射频自干扰信号抵消电路,仿真结果表明其可在900~933MHz频 出优势,己广泛应用于交通、仓储物流、供应链、产品溯源等智能管理信息系统 带内实现大于40B的载波抑制度:提出了一种噪声和失真抵消式低噪声跨导放大 之中。近年来,UHF RFID应用领域不断扩大,市场对工作距离大于10米的远距 器, 其利用NMOS和PMOS品体管二阶非线性系数的互补性、AB类放大器在特 离UHF RFID系统需求迫切,因此对UH亚RFD读写器的接收灵敏度提出更高要 定信号输入功率范围内的增益扩展特性提高了放大器的线性度,仿真结果显示其 求。另一方面,为促进UHF RFID系统的大规模应用,需进一步降低读写器成本 输入三阶交调截点和输入1dB压缩点分别达到18.14dBm和8.1dBm:提出了 功耗和尺士。射频收发前端作为读写器的核心功能电路,其性能高低基本上决定 种互补源极跟随器反馈型低噪声跨导放大器,其利用CMOS互补结构的二阶非线 了读写器整机性能。基于分立元件的读写器在取得高灵敏度的同时,存在功耗高 性失真抵消特性和导数叠加技术提升了电路的线性度性能,仿真结果表明其输入 和休积大等不足,且前学术界中渍写器技术研究集中车低功耗、全华成的读写器 三阶交调截点和输入1dB压缩点分别达到20.8dBm和4.14dBm:设计了一款电 芯片实现方法,主要面向近距离UHF RFID系统应用 因此,开展小型化高性能 流模式无源混频器和一款跨阻放大器,并结合前述设计的互补源极跟随器反馈型 读写器收发前端电路关键技术研究,研制低成本低功耗高性能读写器收发前端模 低噪声跨导放大器实现了完整无电感型电流模式接收射频前端。仿真结果表明, 块及芯片,具有重要科学意义和工程应用价值 当该接收射频前端与无源射频自干扰信号抵消电路同时工作时,其在0dBm自干 本论文针对UHF RFID读写器中存在强射频自干扰信号限制其接收灵敏度这 扰信号功率下实现了16.3dB的双边带噪声系数和25.22B的电压转换增益,可显 著提升读写器在有强射频自干扰信号下的接收灵敏度。 关键问题,在系统分析射频自干扰信号特性及其效应的基础上,分别从高性能 4.针对射频自干扰载波信号相位噪声恶化读写器灵敏度的问题,提出了一种 UHF RFID读写器射频前端电路、射频收发链路隔离结构及UHF RFID读写器射频 低相位噪声低压跨导增强型Colpitts压控振荡器,其通过去掉传统Colpitts结构中 前端芯片三个方面展开了深入研究。 的尾电流源并选择小的抽头电容分压比以获得超过电源电压的单端振荡摆幅,从 本论文主要研究工作及贡献如下: 而降低振荡器的/?区域相位噪声:该振荡器的无尾电流源结构及其跨导增强品 1. 针对读写器射频前端电路小型化高性能应用需求,提出了基于定向耦合器 体管的开关工作模式显著抑制了品体管低频闪烁噪声的上变频,有效降低了振荡 的双调谐小尺寸收发隔离结构,其显著地提升了对射频自干扰信号的抑制效果: 器的/f区域相位噪声。该压控振荡器采用台积电0.18 m RF CMOS工艺设计, 提出了一种低噪声接收射颍前端架构,其能利用距离相关效应降低自干扰载波信 仿真结果表明其在0.6V电源电压下的单端振荡信号峰峰值超过1.66V,频率调谐 号相位噪声对输出信号信噪比的恶化影响。在前述关键技术研究基础上,设计研 范围为3.28-3.89GH2:当振荡频率为3.76GHz时,其在100kHz和1MHz频偏 制出小型化多协议UHF RFID读写器核心模块,实验测试得到读写器模块中射频 处的相位噪声分别达到-104.6dBc/Hz和-127.6dBc/Hz,1/f3拐点频率仅为60kHz。 收发隔离度达到4065dB,接收机在50dB收发隔离度和40kbps比特率下的灵敏 该压控根荡器具有低相位噪声优势,可应用到对LO信号相位噪声有严格要求的高 度达到-86dBm,其具有高性能小尺寸优点,适合中、远距离UHF RFID系统应用。 性能UHF RFID读写器和其他无线收发机芯片中 2. 在理论分析UHF RFID读写器中射频自干扰信号抵消电路性能对射频自干 本论文研究成果为高灵敏度UH亚RFD读写器芯片和整机的实现提供了可行 扰信号抑制效能及其对接收链路噪声系数影响的基础上,提出了基于正交馈电式 的解决方案,满足远距离无源UHF RFID系统的广泛应用需求,有助于推动UHF 圆极化天线、平衡式环形器、射频自干扰信号抵消电路级联的射频收发链路隔离 RFD和物联网技术及应用的发展。 结构,其具有射频收发通道间隔离度高、插入损耗低等优点:设计研制出原型样 关建词:射频识别,读写器射顷前端,射频自干扰信号抵消电路, 低噪声跨导放 机, 测试结果表明该射频收发链路隔离结构在920-925MHz频带内对射频自干扰 大器,压控振荡器

电子科技大学 20 3 研究生学位论文写作方法 已毕业学生论文摘要举例(博士) UHF_RFID读写器收发前端电路关键技术研究_陈俊

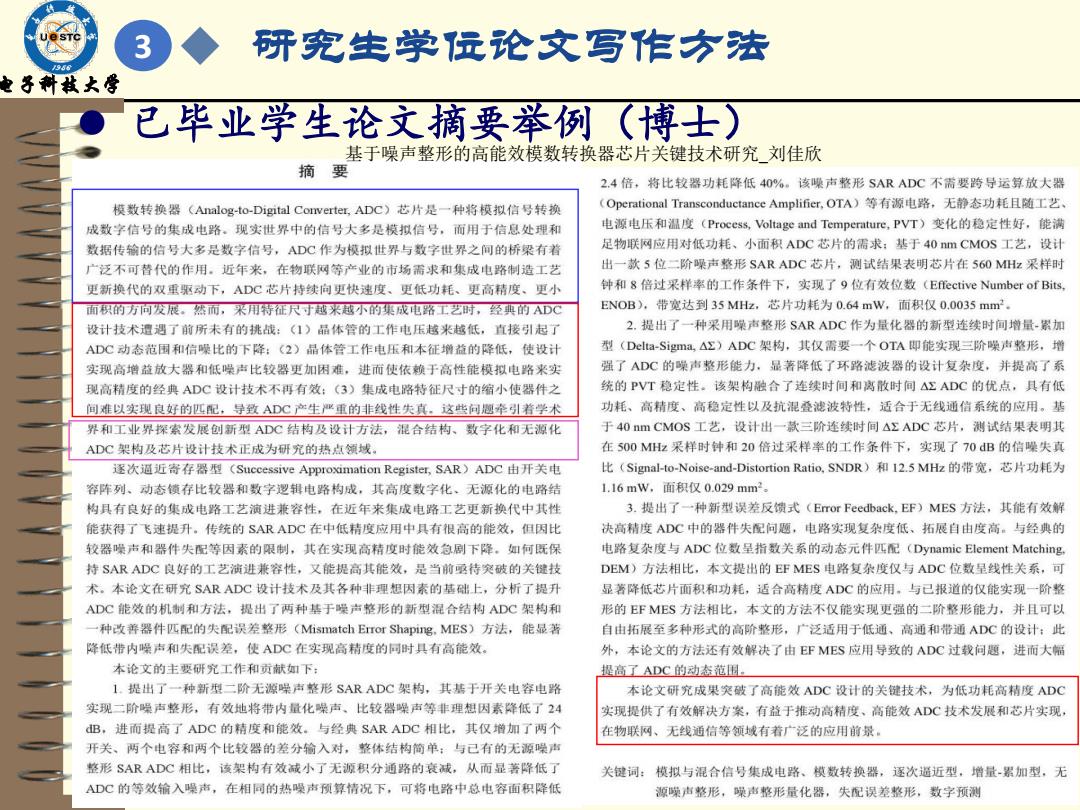

研究生学阮论文写作方法 子技大 已毕业学生论文摘要举例(博士) 基于噪声整形的高能效模数转换器芯片关键技术研究刘佳欣 摘 要 2.4倍,将比较器功耗降低40%。该噪声整形SAR ADC不需要跨导运算放大器 模数转换器(Analog-to-Digital Converter,ADC)芯片是一种将模拟信号转换 (Operational Transconductance Amplifier,.OTA)等有源电路,无静态功耗且随工艺 成数字信号的集成电路。现实世界中的信号大多是模拟信号,而用于信息处理和 电源电压和温度(Process,Voltage and Temperature,PVT)变化的稳定性好,能满 数据传输的信号大多是数字信号,ADC作为模拟世界与数字世界之间的桥梁有着 足物联网应用对低功耗、小面积ADC芯片的需求:基于40 m CMOS工艺,设计 广泛不可替代的作用。近年来,在物联网等产业的市场需求和集成电路制造工艺 出一款5位二阶噪声整形SAR ADC芯片,测试结果表明芯片在560MHz采样时 更新换代的双重驱动下,ADC芯片持续向更快速度、更低功耗、更高精度、更小 钟和8倍过采样率的工作条件下,实现了9位有效位数(Effective Number of Bits, 面积的方问发展。然而,米用特征尺时越米越小的集成电路工艺时,经典的ADC ENOB),带宽达到35MHz,芯片功耗为0.64mW,面积仅0.0035mm2 设计技术遭遇了前所未有的挑战:(1)品体管的工作电压越来越低,直接引起了 2.提出了一种采用噪声整形SAR ADC作为量化器的新型连续时间增量~累加 ADC动态范围和信噪比的下降:(2)品体管工作电压和本征增益的降低,使设计 型(Dela-Sigma,△2)ADC架构,其仅需要一个OTA即能实现三阶噪声整形,增 实现高增益放大器和低噪声比较器更加困难,进而使依赖于高性能模拟电路来实 强了ADC的噪声整形能力,显著降低了环路滤波器的设计复杂度,并提高了系 现高精度的经典ADC设计技术不再有效:(3)集成电路特征尺寸的缩小使器件之 统的PVT稳定性。该架构脸合了连续时间和离散时间△ΣADC的优点,具有低 间难以实现良好的匹配,导致ADC产生严重的非线性失真.这些问题牵引着学术 功耗、高精度、高稳定性以及抗混叠滤波特性,适合于无线通信系统的应用。基 界和工业界探索发展创新型ADC结构及设计方法,混合结构、数字化和无源化 于40 nm CMOS工艺,设计出一款三阶连续时间△ΣADC芯片,测试结果表明其 ADC架构及芯片设计技术正成为研究的热点领域。 在500MHz采样时钟和20倍过采样率的工作条件下,实现了70B的信噪失真 逐次通近寄存器型(Successive Approximation Register,SAR)ADC由开关电 比(Signal-to-Noise-and-Distortion Ratio,.SNDR)和I2.5MHz的带宽,芯片功耗为 容阵列、动态锁存比较器和数字逻辑电路构成,其高度数字化、无源化的电路结 1.16mW,面积仅0.029mm2。 构具有良好的集成电路工艺演进兼容性,在近年来集成电路工艺更新换代中其性 3.提出了一种新型误差反馈式(Error Feedback,EF)MES方法,其能有效解 能获得了飞速提升。传统的SAR ADC在中低精度应用中具有很高的能效,但因比 决高精度ADC中的器件失配问题,电路实现复杂度低、拓展自由度高。与经典的 较器噪声和器件失配等因素的限制,其在实现高精度时能效急剧下降。如何既保 电路复杂度与ADC位数呈指数关系的动态元件匹配(Dynamic Element Matching. 持SAR ADC良好的工艺演进兼容性,又能提高其能效,是当前亟待突破的关键技 DEM)方法相比,本文提出的EF MES电路复杂度仅与ADC位数呈线性关系,可 术。本论文在研究SAR ADC设计技术及其各种非理想因素的基础上,分析了提升 显著降低芯片面积和功耗,适合高精度ADC的应用。与已报道的仅能实现一阶整 ADC能效的机制和方法,提出了两种基于噪声整形的新型混合结构ADC架构和 形的EF MES方法相比,本文的方法不仅能实现更强的二阶整形能力,并且可以 种改善器件匹配的失配误差整形(Mismatch Error Shaping,MES)方法,能显著 自由拓展至多种形式的高阶整形,广泛适用于低通、高通和带通ADC的设计:此 降低带内噪声和失配误差,使ADC在实现高精度的同时具有高能效。 外,本论文的方法还有效解决了由EF MES应用导致的ADC过载间题,进而大幅 本论文的主要研究工作和贡献如下: 提高了ADC的动态范围 1.提出了一种新型二阶无源噪声整形SAR ADC架构,其基于开关电容电路 本论文研究成果突破了高能效ADC设计的关键技术,为低功耗高精度ADC 实现二阶噪声整形,有效地将带内量化噪声、比较器噪声等非理想因素降低了24 实现提供了有效解决方案,有益于推动高精度、高能效ADC技术发展和芯片实现, dB,进而提高了ADC的精度和能效。与经典SAR ADC相比,其仅增加了两个 在物联网、无线通信等领域有着广泛的应用前景。 开关、两个电容和两个比较器的差分输入对,整体结构简单:与已有的无源噪声 整形SAR ADC相比,该架构有效减小了无源积分通路的衰减,从而显著降低了 关键词:模拟与混合信号集成电路、模数转换器,逐次逼适近型,增量-累加型,无 ADC的等效输入噪声,在相同的热噪声预算情况下,可将电路中总电容面积降低 源噪声整形,噪声整形量化器,失配误差整形,数字预测

电子科技大学 21 3 研究生学位论文写作方法 已毕业学生论文摘要举例(博士) 基于噪声整形的高能效模数转换器芯片关键技术研究_刘佳欣