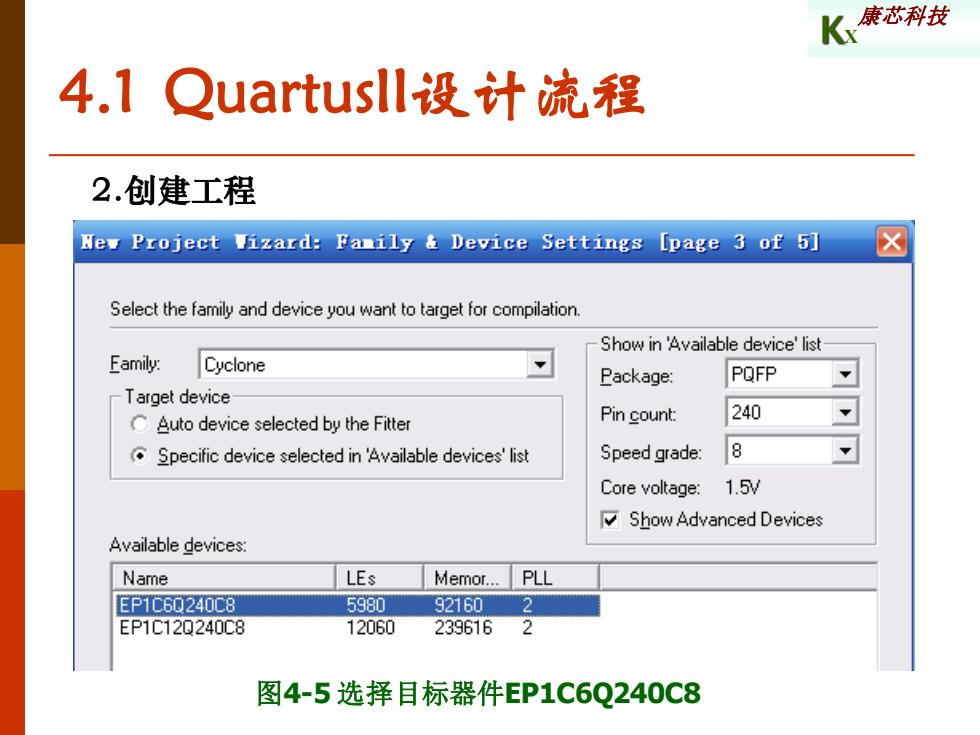

K康芯科技 4.1 Quartusll-设计流程 2.创建工程 Nev Project Wizard:Family Device Settings [page 3 of 5] Select the family and device you want to target for compilation. Show in Available device'list Eamily: Cyclone Package: POFP -Target device CAuto device selected by the Fitter Pin count: 240 Specific device selected in 'Available devices'list Speed grade: 8 Core voltage: 1.5/ Show Advanced Devices Available devices: Name LEs Memor.PLL EP1C60240C8 5980 92160 2 EP1C120240C8 12060 239616 2 图4-5选择目标器件EP1C6Q240C8

KX 康芯科技 4.1 QuartusII设计流程 2.创建工程 图4-5 选择目标器件EP1C6Q240C8

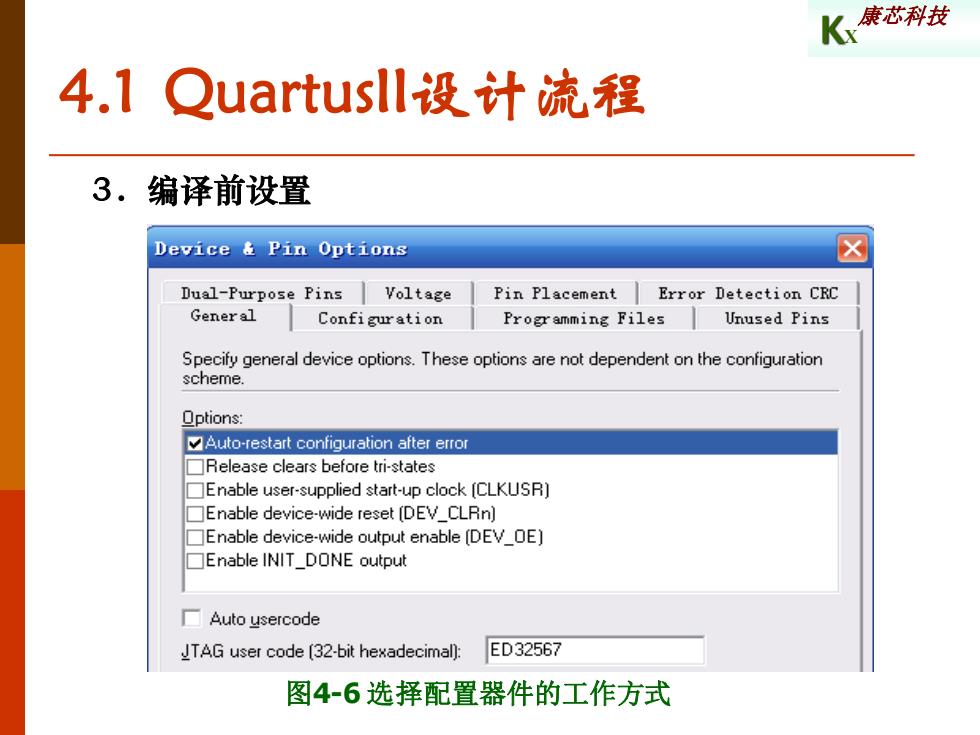

K能芯科技 4.1 Quartusll-设计流程 3.编译前设置 Device Pin Options Dual-Purpose Pins Voltage Pin Placement Error Detection CRC General Configuration Programming Files Unused Pins Specify general device options.These options are not dependent on the configuration scheme. ☐ptions: Auto-restart configuration after error Release clears before tri-states Enable user-supplied start-up clock [CLKUSR] Enable device-wide reset (DEV_CLRn) Enable device-wide output enable (DEV_OE) Enable INIT_DONE output □Auto usercode JTAG user code (32-bit hexadecimal): ED32567 图4-6选择配置器件的工作方式

KX 康芯科技 4.1 QuartusII设计流程 3.编译前设置 图4-6 选择配置器件的工作方式

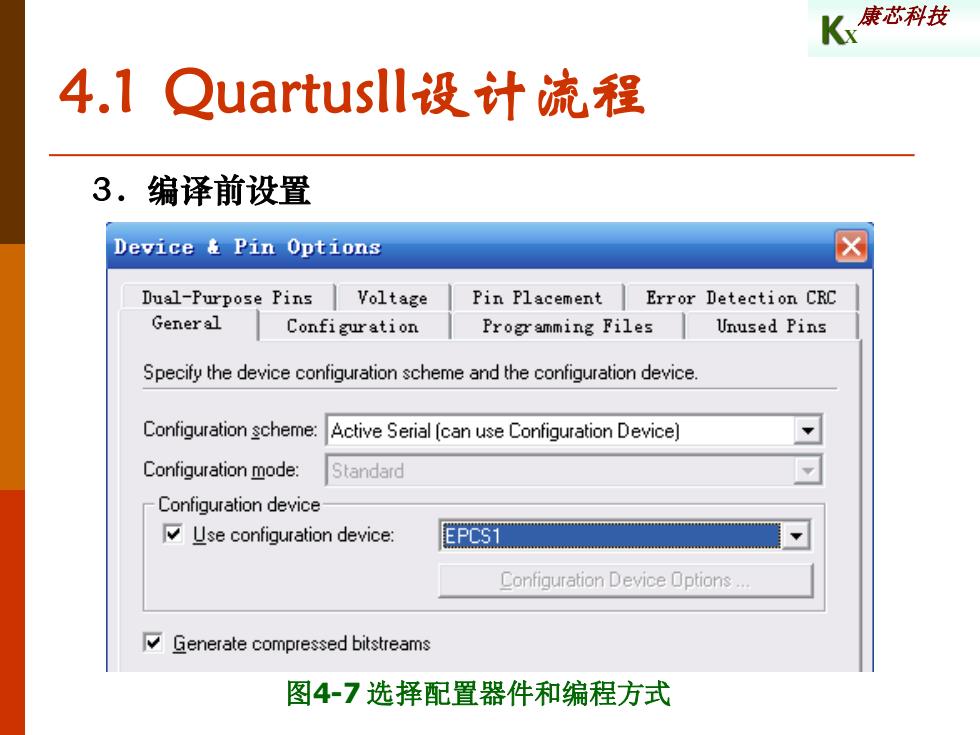

K康芯科技 4.1 Quartusll-设计流程 3.编译前设置 Device Pin Options Dual-Purpose Pins Voltage Pin Placement Error Detection CRC General Configuration Programming Files Unused Pins Specify the device configuration scheme and the configuration device. Configuration scheme:Active Serial (can use Configuration Device] Configuration mode: Standard Configuration device Use configuration device: EPCS1 Configuration Device Options Generate compressed bitstreams 图4-7选择配置器件和编程方式

KX 康芯科技 4.1 QuartusII设计流程 3.编译前设置 图4-7 选择配置器件和编程方式

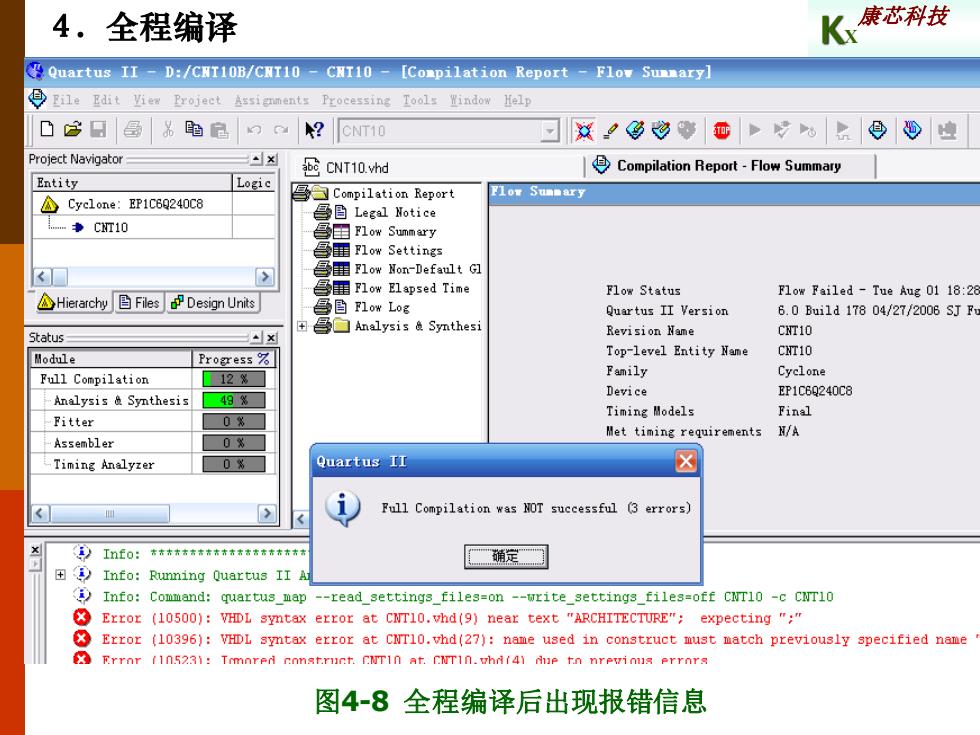

4.全程编译 K康恋科技 Quartus II -D:/CNT10B/CNT10 -CNT10 [Compilation Report Flow Sumsary] ⑨1 e Edit Viee Projeet Assignments Processing Tools Window Help ·它日曼%陷色 2CNT10 效’g必等>6⑨少迎 Project Navigator b CNT10.vhd Compilation Report-Flow Summary Entity Logic Cyelone:EP1C6Q240C8 Compilation Report Flow Summary 鸟凸Legal Notice -◆C2T10 鸟里1 ow Summary low Settings 日 用Flow Non-Default G 里1ow1 apsed Time Flow Status Flow Failed -Tue Aug 01 18:28 △Hierarchy目FilesDesign Units 哥目1 Ow Log Quartus II Version 6.0Bui1d17804/27/2006SJFy 田☐Analysis&Synthesi Status ✉x Revision Name CNT10 周ole Top-level Entity Name CNT10 Full Compilation Family 12% Cyclone Analysis Synthesis Device EP1C6Q240C8 49% Final Fitter 0% Timing Models Met timing requirements N/A -Assembler 0% Timing Analyzer 0% Quartus II 函 Full Compilation was NOT successful (3 errors) Inf0:木木木本方吉者市木*方方者吉本本木本者古 确定门 Info:Running Quartus II Info:Command:quartus_map -read_settings_files=on -vrite_settings_files=off CNT10-c CNT10 Ertor (10500):VHDL syntax error at CNT10.vhd(9)near text "ARCHITECTURE";expecting "; Error (10396):VHDL syntax error at CNT10.vhd(27):name used in construct must match previously specified name Error (105231:Tmored construct.CNTI0 at.CNTI0.vhd/41 due to nrevious errors 图4-8全程编译后出现报错信息

KX 康芯科技 图4-8 全程编译后出现报错信息 4.全程编译

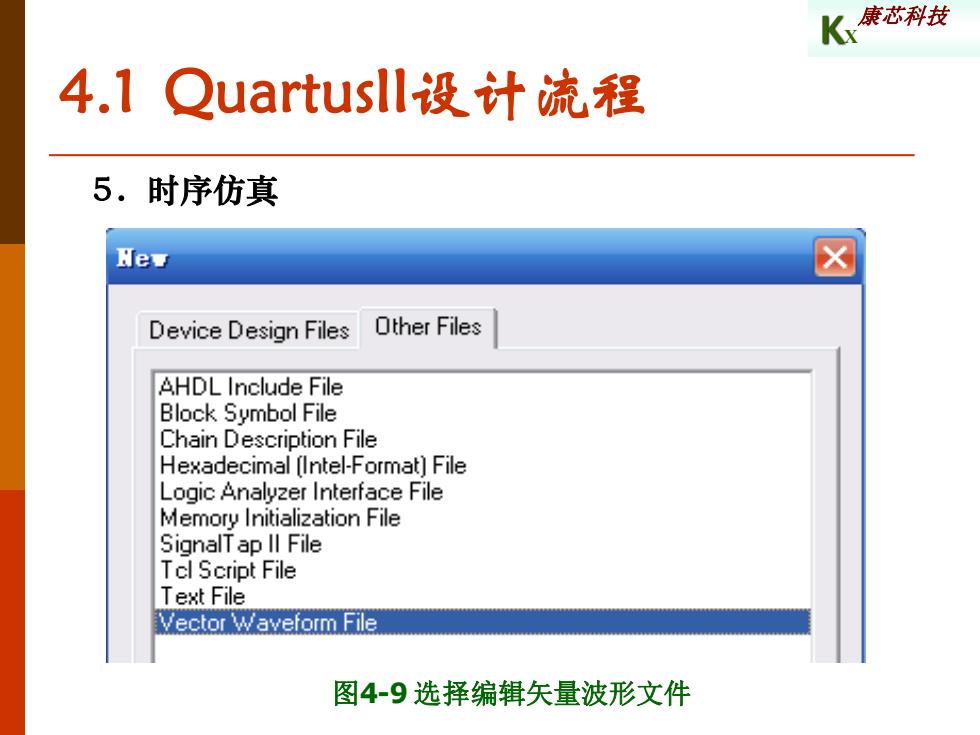

K康芯科技 4.1 Quartusll-设计流程 5.时序仿真 Nev ☒ Device Design Files Other Files AHDL Include File Block Symbol File Chain Description File Hexadecimal (Intel-Format]File Logic Analyzer Interface File Memory Initialization File SignalT ap ll File Tcl Script File Text File Vector Waveform File 图4-9选择编辑矢量波形文件

KX 康芯科技 4.1 QuartusII设计流程 图4-9 选择编辑矢量波形文件 5.时序仿真