以下是PRGRAMDAC程序的VHDL源代码,用以对FPGA编程 控制RAMDAC工作的,模块Port定义部分如下: library IEEE; use IEEE.std logic 1164.all: use IEEE.std logic unsigned.all; entity prgramdacver2 is port clk:in STD LOGIC; 时钟 rstn:in STD LOGIC; -低有效异步重置 start:in STD LOGIC: …开始信号 done:out STD LOGIC; 表明程序完成 WRn:out STD LOGIC: -RAMDAC写选通线(低有效) RDn:out STD LOGIC; -RAMDAC读选通线(低有效) RS:inout STD LOGIC VECTOR(2 downto 0); -RAMDAC记录选通线 data:inout STD LOGIC VECTOR(7 downto 0) -RAMDAC双向数据线 end prgramdacver2; 关于功能描叙的代码相当长而且十分的复杂,故这里未提供 这些源代码。以下是对这个模块的行为级仿真的波形图(图2.4): Nane Value 40015016d0 7001800 900,1000,100 1200,1300400,15001600 nr ck ar tstn 0 arstart ar done WRn arRDn 1 王MRS 王r data A1 (图2.4) ◆2.4 VGACORE程序解析 这个程序是FPGA用来产生VGA显示的同步信号及其它控制 信号。这些对于显示的控制,也就是分辨率和刷新率。缺省的显 示设置是分辨率:800*600,刷新率:72Hz。而通过这个程序可 以很方便的改变这些设置。改变它们也就意味着改变了系统时钟 频率,而缺省频率是50MHz。 这一程序的Pot定义如下(功能描叙部分的源代码省去未给 出): library IEEE; use IEEE.std logic_1164.all; 课题名称:数字视频编码器子模块的设计与优化 -6- PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

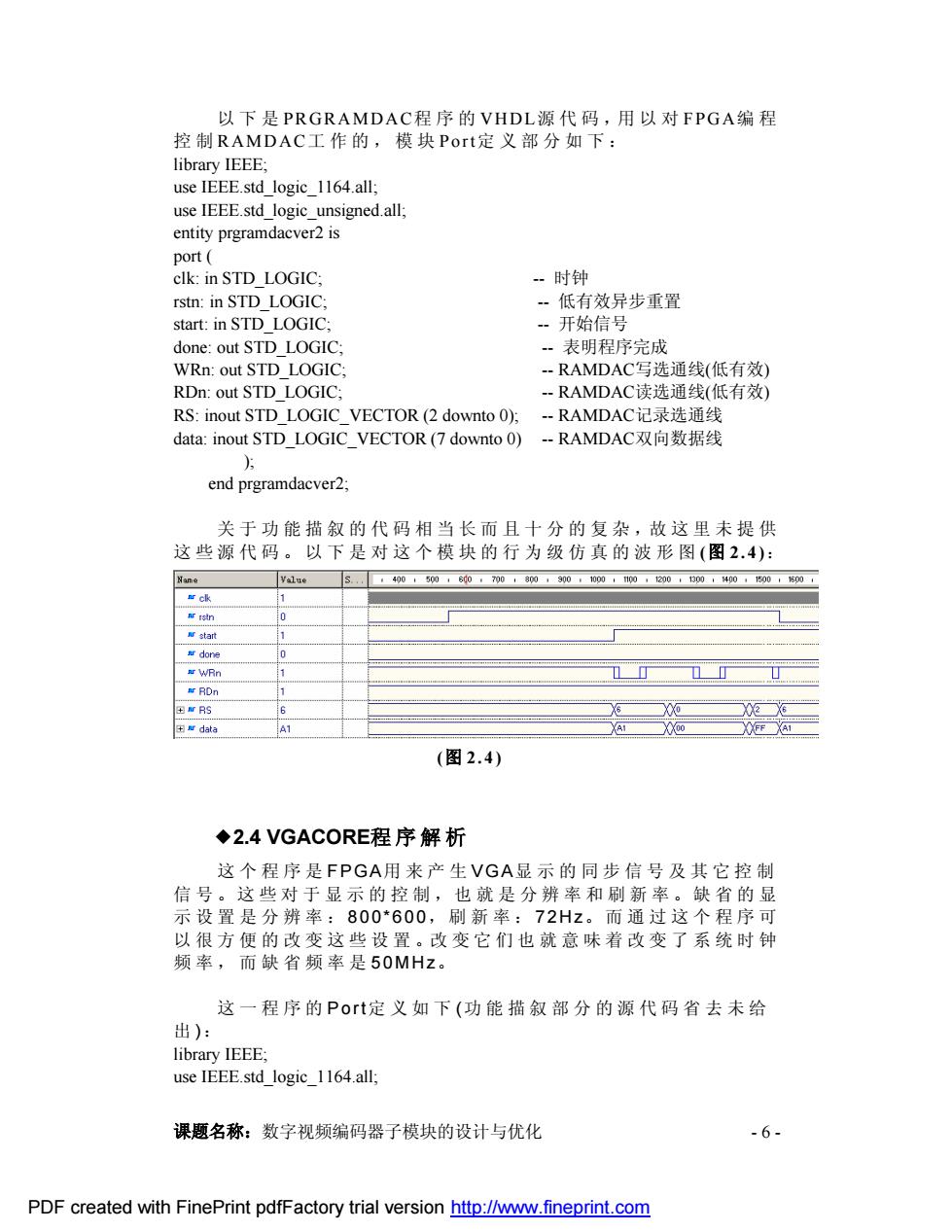

课题名称:数字视频编码器子模块的设计与优化 - 6 - 以下是 PRGRAMDA C程 序 的 VHDL源 代 码 ,用 以 对 FPG A编 程 控 制 RAM DAC工 作 的 , 模 块 Por t定 义 部 分 如 下 : library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity prgramdacver2 is port ( clk: in STD_LOGIC; -- 时钟 rstn: in STD_LOGIC; -- 低有效异步重置 start: in STD_LOGIC; -- 开始信号 done: out STD_LOGIC; -- 表明程序完成 WRn: out STD_LOGIC; -- RAMDAC写选通线(低有效) RDn: out STD_LOGIC; -- RAMDAC读选通线(低有效) RS: inout STD_LOGIC_VECTOR (2 downto 0); -- RAMDAC记录选通线 data: inout STD_LOGIC_VECTOR (7 downto 0) -- RAMDAC双向数据线 ); end prgramdacver2; 关 于 功 能 描 叙 的 代 码 相 当 长 而 且 十 分 的 复 杂 ,故 这 里 未 提 供 这 些 源 代 码 。 以 下 是 对 这 个 模 块 的 行 为 级 仿 真 的 波 形 图 (图 2.4): (图 2.4) ¿2.4 VGACORE程 序解析 这 个 程 序 是 FPGA用 来 产 生 VGA显 示 的 同 步 信 号 及 其 它 控 制 信 号 。这 些 对 于 显 示 的 控 制 ,也 就 是 分 辨 率 和 刷 新 率 。缺 省 的 显 示 设 置 是 分 辨 率 : 800*600, 刷 新 率 : 72Hz。 而 通 过 这 个 程 序 可 以 很 方 便 的 改 变 这 些 设 置 。改 变 它 们 也 就 意 味 着 改 变 了 系 统 时 钟 频 率 , 而 缺 省 频 率 是 50MHz。 这 一 程 序 的 Port定 义 如 下 (功 能 描 叙 部 分 的 源 代 码 省 去 未 给 出 ): library IEEE; use IEEE.std_logic_1164.all; PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

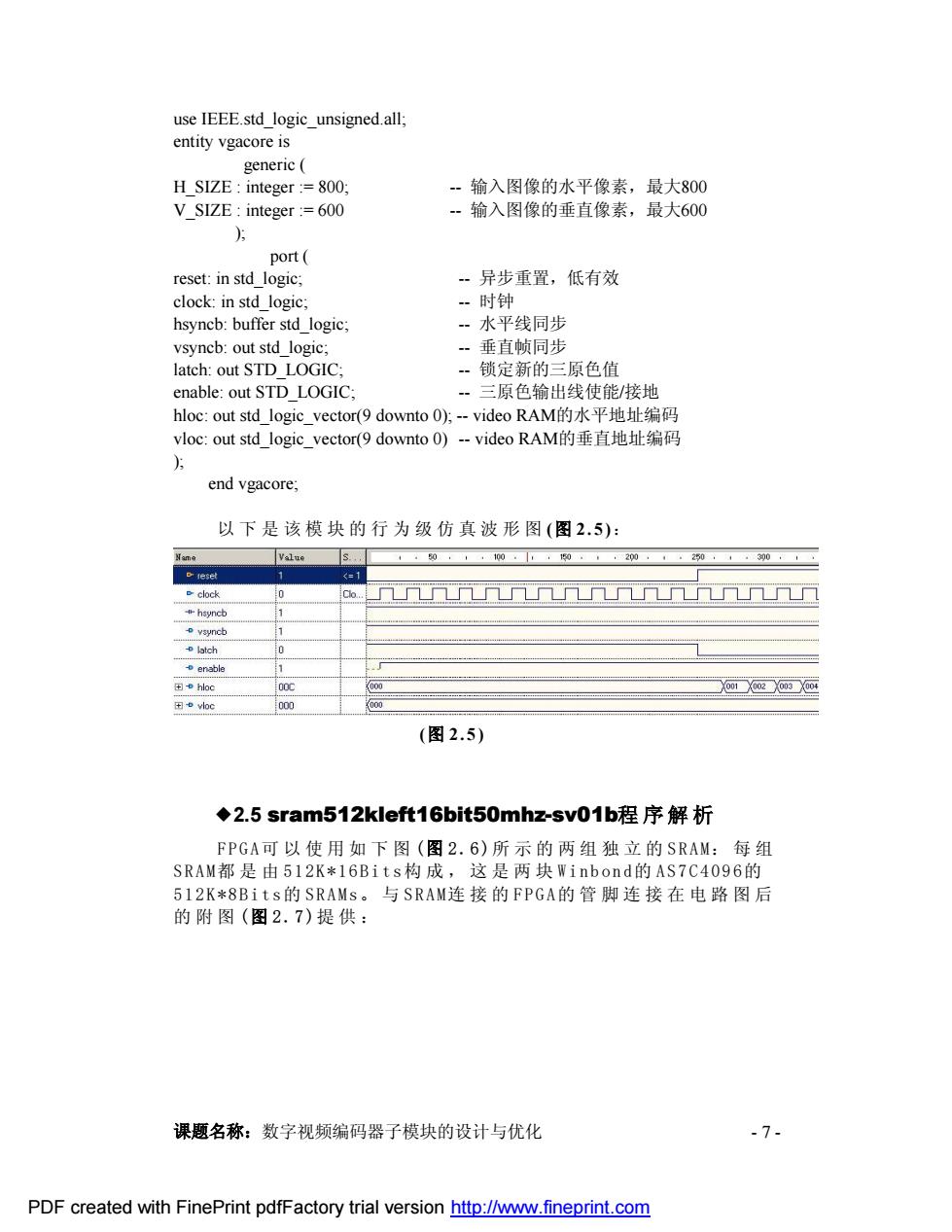

use IEEE.std logic unsigned.all; entity vgacore is generic H SIZE:integer:=800; -输入图像的水平像素,最大800 V SIZE:integer:=600 -输入图像的垂直像素,最大600 方 port reset:in std logic; -异步重置,低有效 clock:in std logic; …时钟 hsyncb:buffer std logic; …水平线同步 vsyncb:out std logic; …垂直帧同步 latch:out STD LOGIC; 锁定新的三原色值 enable:out STD LOGIC: -三原色输出线使能/接地 hloc:out std logic_vector(9 downto 0);-video RAM的水平地址编码 vloc:out std logic_vector((9 downto 0)-video RAM的垂直地址编码 end vgacore; 以下是该模块的行为级仿真波形图(图2.5): 50 100. 200 250 300· leset 1 <=1 clock 0 09 1 vsyncb 1 latch 0 enable 田hloc O0C 000 0o10o20m30o4 田vloc 000 (图2.5) ◆2.5sram512 kleft16bit50mhz-sv01b程序解析 FPGA可以使用如下图(图2.6)所示的两组独立的SRAM:每组 SRAM都是由512K*16Bits构成,这是两块Winbond的AS7C4096的 512K*8Bits的SRAMs。与SRAM连接的FPGA的管脚连接在电路图后 的附图(图2.7)提供: 课题名称:数字视频编码器子模块的设计与优化 .7 PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 7 - use IEEE.std_logic_unsigned.all; entity vgacore is generic ( H_SIZE : integer := 800; -- 输入图像的水平像素,最大800 V_SIZE : integer := 600 -- 输入图像的垂直像素,最大600 ); port ( reset: in std_logic; -- 异步重置,低有效 clock: in std_logic; -- 时钟 hsyncb: buffer std_logic; -- 水平线同步 vsyncb: out std_logic; -- 垂直帧同步 latch: out STD_LOGIC; -- 锁定新的三原色值 enable: out STD_LOGIC; -- 三原色输出线使能/接地 hloc: out std_logic_vector(9 downto 0); -- video RAM的水平地址编码 vloc: out std_logic_vector(9 downto 0) -- video RAM的垂直地址编码 ); end vgacore; 以 下 是 该 模 块 的 行 为 级 仿 真 波 形 图 (图 2.5): (图 2.5) ¿2.5 sram512kleft16bit50mhz-sv01b程 序 解 析 FPGA可 以 使 用 如 下 图 (图 2 . 6 )所 示 的 两 组 独 立 的 SR A M: 每 组 SRAM都 是 由 5 1 2K * 16Bits构 成 , 这 是 两 块 Wi nb on d的 A S7C4 09 6的 512K *8Bi t s的 SR A M s。 与 S RA M连 接 的 FP G A的 管 脚 连 接 在 电 路 图 后 的 附 图 (图 2 . 7 )提供: PDF created with FinePrint pdfFactory trial version http://www.fineprint.com