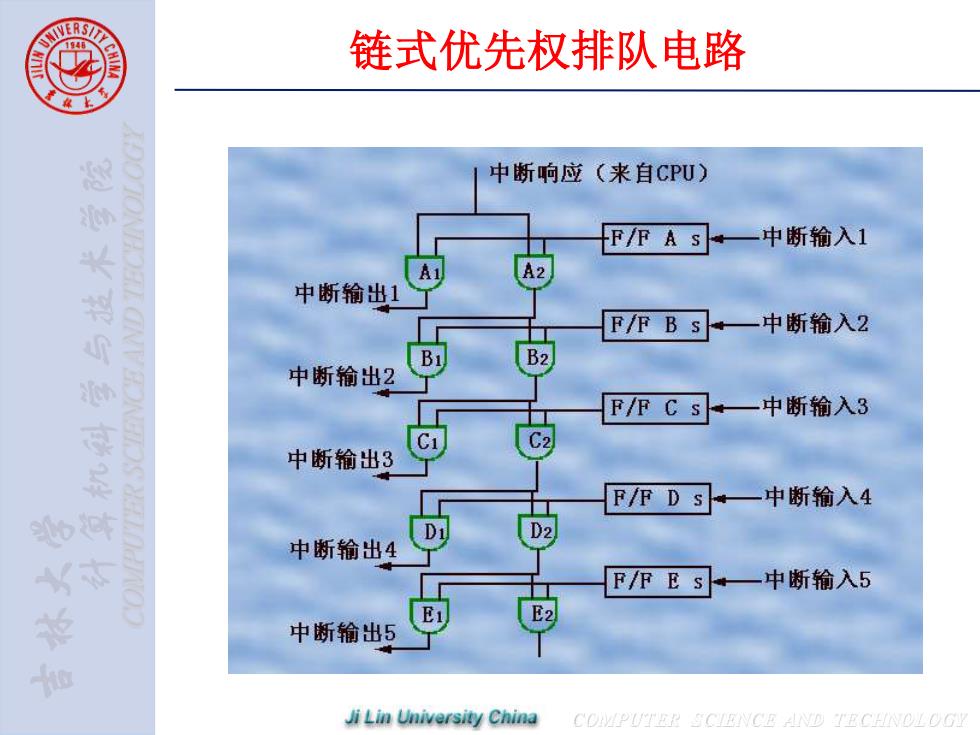

链式优先权排队电路 中断响应(来自CPU) -F/F A s 中断输入1 A1 A2 中断输出1 FPBS·一中断输入2 中断输出2 B2 F/F Cs 。一中断输入3 C2 中断输出3 F/F D s 。一中断输入4 Di 中断输出4 D2 F/F E s 中断输入5 E2 中断输出5 Ji Lin University China COMPUTER SCIENCE山NY厘CHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 链式优先权排队电路

7.4中断控制器8259A 8259A是中断管理芯片 8259A的主要功能为: 1.具有8级优先权控制,通过芯片级联可扩展至64级优先 权控制 2.每一级中断均可通过编程屏蔽或允许 3.在中断响应周期可提供相应的中断类型号 4.有多种工作方式,可通过编程选择 5.可与CPU直接连接,不需外加硬件电路 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 7.4 中断控制器8259A • 8259A是中断管理芯片 • 8259A的主要功能为: 1.具有8级优先权控制,通过芯片级联可扩展至64级优先 权控制 2.每一级中断均可通过编程屏蔽或允许 3.在中断响应周期可提供相应的中断类型号 4.有多种工作方式,可通过编程选择 5.可与CPU直接连接,不需外加硬件电路

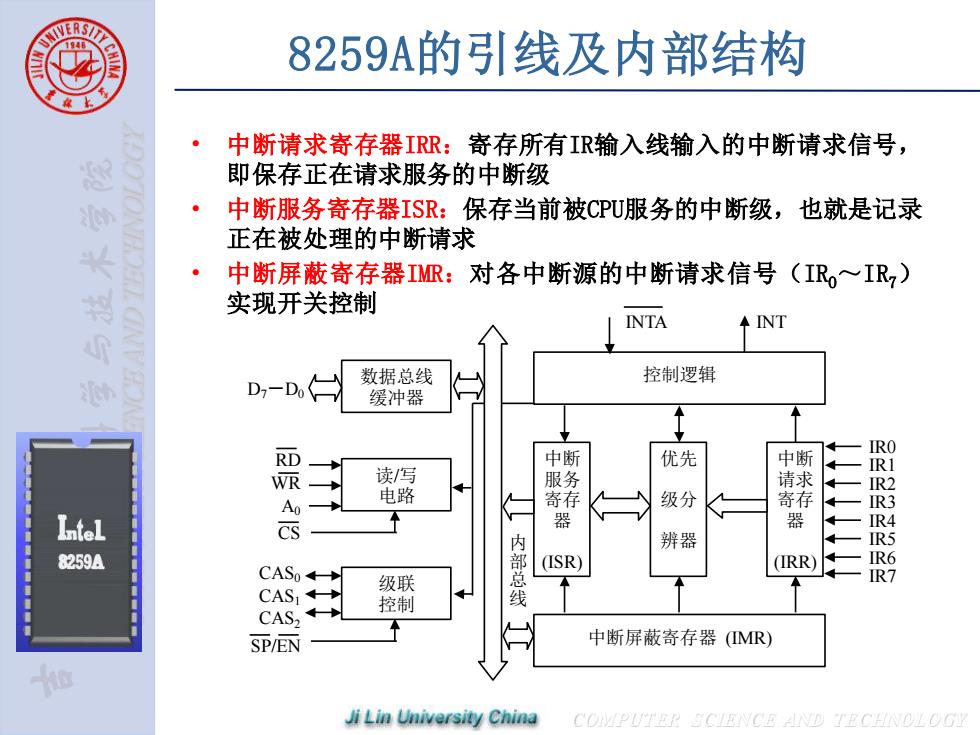

CHINA 8259A的引线及内部结构 中断请求寄存器IRR:寄存所有IR输入线输入的中断请求信号, 即保存正在请求服务的中断级 中断服务寄存器ISR:保存当前被CPU服务的中断级,也就是记录 正在被处理的中断请求 中断屏蔽寄存器IMR:对各中断源的中断请求信号(IR。~IR,) 实现开关控制 INTA ◆NT 数据总线 控制逻辑 D-D0 缓冲器 RD 中 优先 中断 W丽 读/写 服务 请求 电路 级分 寄存 Intel 器 辨器 8259A CAS0←+ (ISR) (IRR) 级联 CAS1← 内部总线 控制 CAS2 SP/EN 中断屏蔽寄存器MR) Ji Lin University China COMPUTEP SCIRNCE AND T里CHO是OGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8259A的引线及内部结构 • 中断请求寄存器IRR:寄存所有IR输入线输入的中断请求信号, 即保存正在请求服务的中断级 • 中断服务寄存器ISR:保存当前被CPU服务的中断级,也就是记录 正在被处理的中断请求 • 中断屏蔽寄存器IMR:对各中断源的中断请求信号(IRO~IR7) 实现开关控制 图 2.4.1 8259A 内部结构 内 部 总 线 INTA INT D7-D0 数据总线 缓冲器 读/写 电路 级联 控制 控制逻辑 中断 服务 寄存 器 (ISR) 优先 级分 辨器 中断 请求 寄存 器 (IRR) 中断屏蔽寄存器 (IMR) RD WR A0 CS CAS0 CAS1 CAS2 SP/EN IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

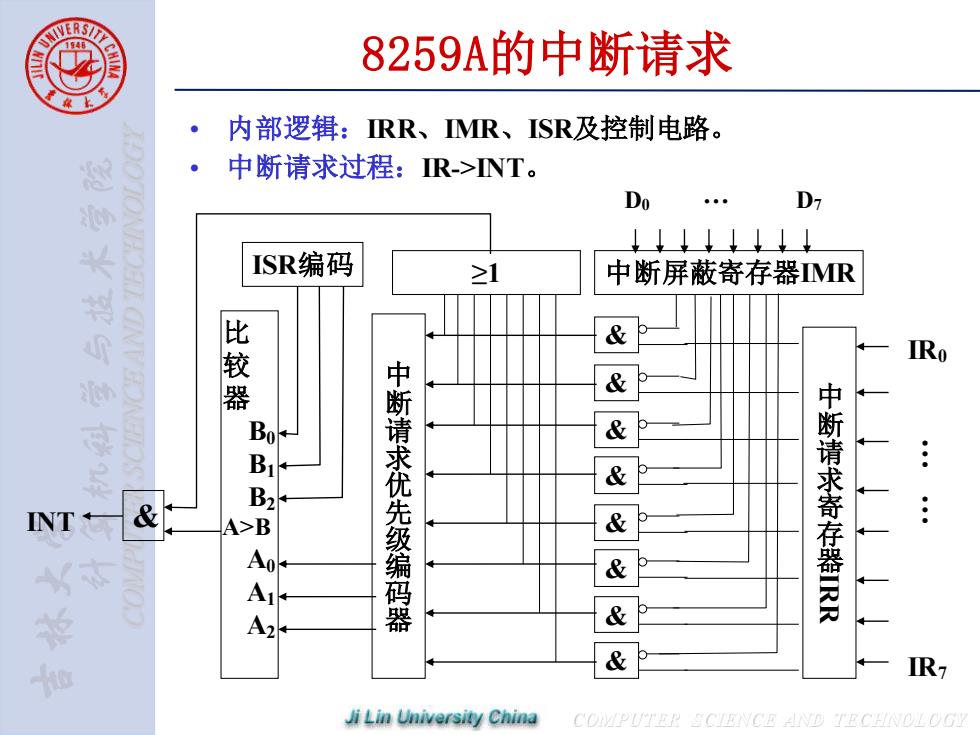

8259A的中断请求 上 内部逻辑:RR、MR、ISR及控制电路。 中断请求过程:R>NT。 Do D7 ↓↓↓↓↓↓↓4 ISR编码 ≥1 中断屏蔽寄存器MR 比较器 IRo 中断请求优先级编码器 & & & 中断请求寄存器天 IR Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8259A的中断请求 • 内部逻辑:IRR、IMR、ISR及控制电路。 • 中断请求过程:IR->INT。 INT & ISR编码 中 断 请 求 优 先 级 编 码 器 中 断 请 求 寄 存 器IRR IR0 IR7 … … & & & & & & & & 中断屏蔽寄存器IMR D0 … D7 ≥1 比 较 器 B0 B1 B2 A>B A0 A1 A2

8259A的工作过程 ● (1)某一条或几条中断请求线(IR,~IR7)有中断申请, 变为高电平,使中断请求寄存器IRR的相应位置“1” ● (2)IMR对IRR屏蔽。未被屏蔽的请求信号经优先权电路 判别最高优先级,再经由优先级方式确定没有更高级优先 权的中断,则8259A的INT端输出为“1”,向CPU提出中断 请求 ● (3)CPU响应中断后发出中断响应信号。在中断响应过程 中,CPU要发出两次INTA信号。当8259A收到第一个INTA信 号后,ISR中当前被选中的最高优先级对应的那一位置 “1”,同时IRR中的相应位被清“O”,表示该位上的中断 请求已被CPU所接受 (4)8259A收到第二INTA信号后,驱动数据总线将对应的 中断类型码输出 (5)如果是自动结束中断方式(AE0I),则在第二个 INTA脉冲结束时将ISR中相应置“1”的位复位,否则该位 的“1”将一直保持,直到CPU发出E0I命令为止 Ji Lin University China COMPUTEP SCIRNCE AND T里CHO是OGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8259A的工作过程 • (1)某一条或几条中断请求线(IRO~IR7)有中断申请, 变为高电平,使中断请求寄存器IRR的相应位置“1” • (2)IMR对IRR屏蔽。未被屏蔽的请求信号经优先权电路 判别最高优先级,再经由优先级方式确定没有更高级优先 权的中断,则8259A的INT端输出为“1” ,向CPU提出中断 请求 • (3)CPU响应中断后发出中断响应信号。在中断响应过程 中,CPU要发出两次INTA信号。当8259A收到第一个INTA信 号后,ISR中当前被选中的最高优先级对应的那一位置 “1” ,同时IRR中的相应位被清“0” ,表示该位上的中断 请求已被CPU所接受 • (4)8259A收到第二INTA信号后,驱动数据总线将对应的 中断类型码输出 • (5)如果是自动结束中断方式(AEOI),则在第二个 INTA脉冲结束时将ISR中相应置“1”的位复位,否则该位 的“1”将一直保持,直到CPU发出EOI命令为止