5.1软硬件通信的基本方式 地址译码:BF531异步读操作时序 当控制信号AMS1和读使能信号ARE同时 为低,且地址满足选通条件的时候,把FPGA中 寄存器(或者O端口)的值送到数据总线上, 这样DSP就可以读取寄存器的值

地址译码:BF531异步读操作时序 当控制信号AMS1和读使能信号ARE同时 为低,且地址满足选通条件的时候,把FPGA中 寄存器(或者IO端口)的值送到数据总线上, 这样DSP就可以读取寄存器的值。 5.1 软硬件通信的基本方式

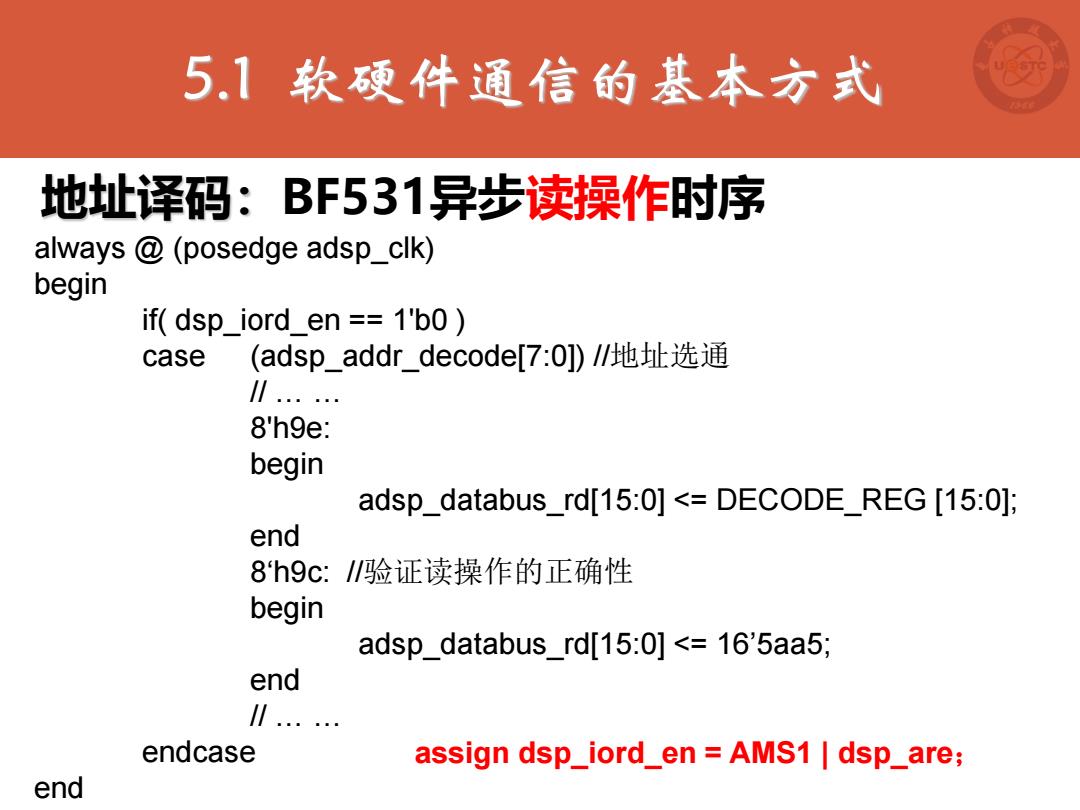

5.1软硬件通信的基本方式 地址译码:BF531异步读操作时序 always @(posedge adsp_clk) begin if(dsp_iord_en =1'bo case (adsp_addr_decode[7:O)地址选通 l.. 8'h9e: begin adsp_databus_rd[15:0]<=DECODE REG [15:0]; end 8h9c: 验证读操作的正确性 begin adsp_databus rd[15:0]<=16'5aa5; end ... endcase assign dsp_iord_en AMS1 dsp_are; end

地址译码:BF531异步读操作时序 5.1 软硬件通信的基本方式 always @ (posedge adsp_clk) begin if( dsp_iord_en == 1'b0 ) case (adsp_addr_decode[7:0]) //地址选通 // … … 8'h9e: begin adsp_databus_rd[15:0] <= DECODE_REG [15:0]; end 8‘h9c: //验证读操作的正确性 begin adsp_databus_rd[15:0] <= 16’5aa5; end // … … endcase end assign dsp_iord_en = AMS1 | dsp_are;