5.1软硬件通信的基本方式 地址译码 从DSP的角度看,当DSP执行写操作指令 时,首先是选通地址AMS1为低电平,地址总 线上准备好目的地址(0x2010009e),同时数 据总线上准备好要送出的数据(0x0055);接 着写使能AWE有效(AWE变为低电平),这个 过程就是DSP处理器把数据0x0055写入到地址 0x2010009e中

地址译码 从DSP的角度看,当DSP执行写操作指令 时,首先是选通地址AMS1为低电平,地址总 线上准备好目的地址(0x2010009e),同时数 据总线上准备好要送出的数据(0x0055);接 着写使能AWE有效(AWE变为低电平),这个 过程就是DSP处理器把数据0x0055写入到地址 0x2010009e中。 5.1 软硬件通信的基本方式

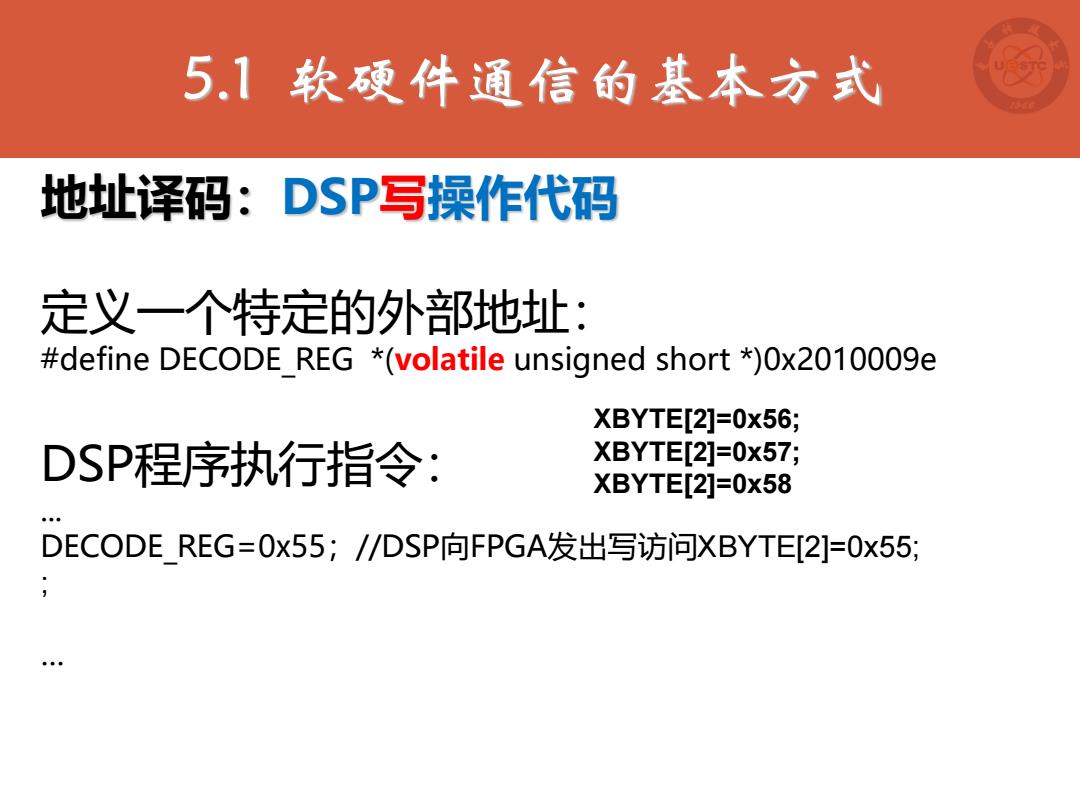

5.1软硬件通信的基本方式 地址译码:DSP写操作代码 定义一个特定的外部地址: #define DECODE REG *(volatile unsigned short *)0x2010009e XBYTE[2]=0x56; DSP程序执行指令: XBYTE[2]=0x57; XBYTE[2]=0x58 DECODE REG=0x55;/DSP向FPGA发出写访问XBYTE2]=0x55;

地址译码:DSP写操作代码 定义一个特定的外部地址: #define DECODE_REG *(volatile unsigned short *)0x2010009e DSP程序执行指令: ... DECODE_REG=0x55;//DSP向FPGA发出写访问XBYTE[2]=0x55; ; … 5.1 软硬件通信的基本方式 XBYTE[2]=0x56; XBYTE[2]=0x57; XBYTE[2]=0x58

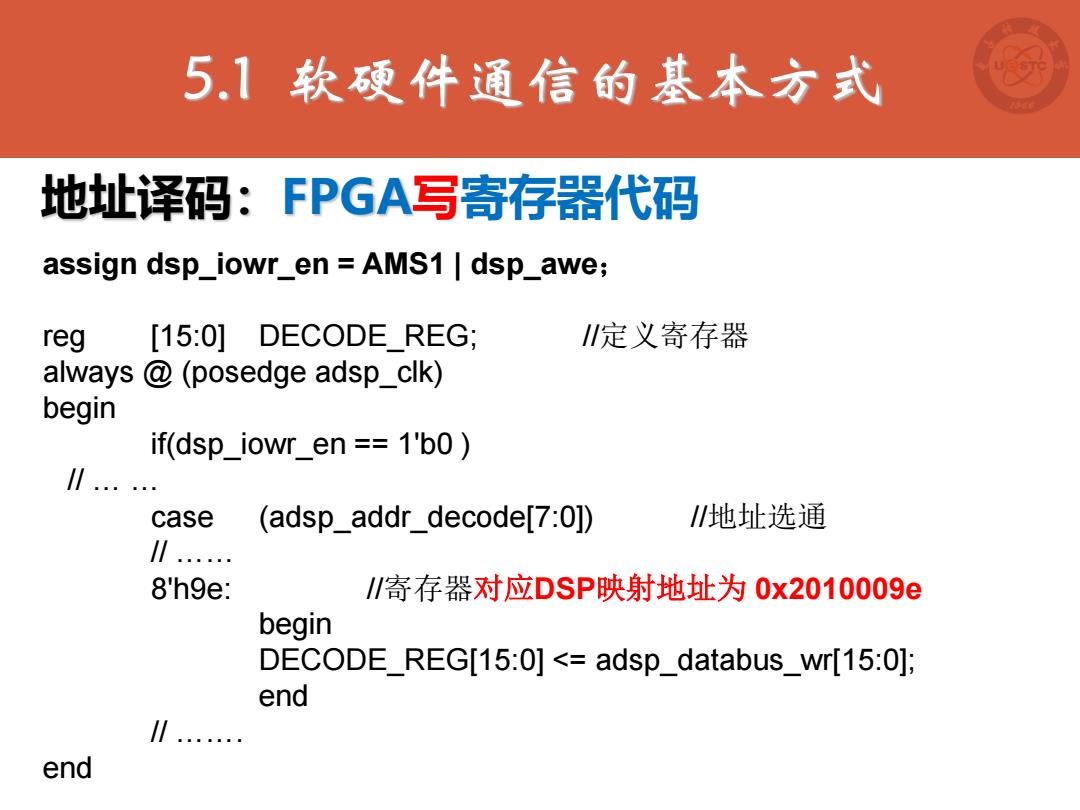

5.1软硬件通信的基本方式 地址译码 从FPGA的角度看,将DPS发出的片选控制 信号AMS1和写使能信号AWE进行逻辑组合 因为二者都是在低电平的时候代表自己被选通 有效,所以采用“或”门逻辑。 FPGA根据地址信号(地址总线)将数据 (数据总线)锁存到一个寄存器。执行该指令 时,相当于向该寄存器写入数据0x0055,这便 是通过地址译码功能实现的DSP处理器进行异 步写操作

地址译码 从FPGA的角度看,将DPS发出的片选控制 信号AMS1和写使能信号AWE进行逻辑组合, 因为二者都是在低电平的时候代表自己被选通 有效,所以采用“或”门逻辑。 FPGA根据地址信号(地址总线)将数据 (数据总线)锁存到一个寄存器。执行该指令 时,相当于向该寄存器写入数据0x0055,这便 是通过地址译码功能实现的DSP处理器进行异 步写操作。 5.1 软硬件通信的基本方式

5.1软硬件通信的基本方式 地址译码:FPGA写寄存器代码 assign dsp_iowr_en AMS1 dsp_awe; reg [15:0]DECODE REG; 定义寄存器 always @(posedge adsp_clk) begin if(dsp_iowr_en =1'bo case (adsp_addr_decode[7:0]) 地址选通 8h9e: /寄存器对应DSP映射地址为0x2010009e begin DECODE_REG[15:0]<adsp_databus_wr[15:0]; end end

地址译码:FPGA写寄存器代码 5.1 软硬件通信的基本方式 reg [15:0] DECODE_REG; //定义寄存器 always @ (posedge adsp_clk) begin if(dsp_iowr_en == 1'b0 ) // … … case (adsp_addr_decode[7:0]) //地址选通 // …… 8'h9e: //寄存器对应DSP映射地址为 0x2010009e begin DECODE_REG[15:0] <= adsp_databus_wr[15:0]; end // ……. end assign dsp_iowr_en = AMS1 | dsp_awe;

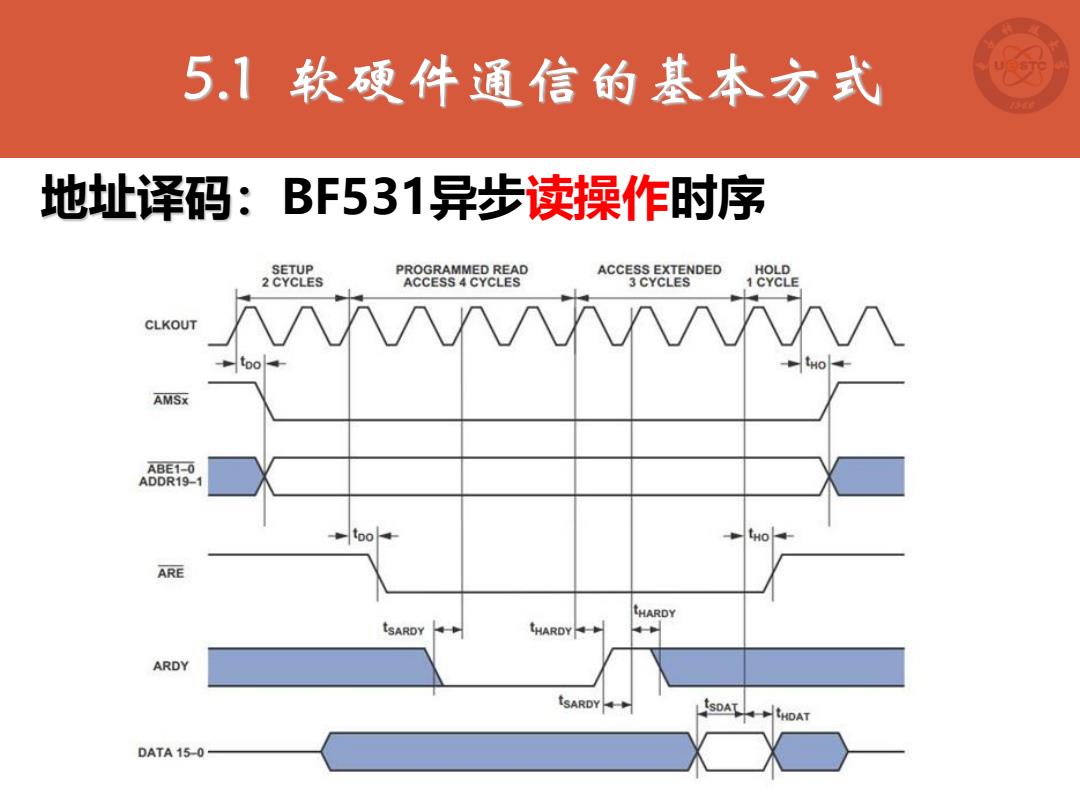

5.1软硬件通信的基本方式 地址译码:BF531异步读操作时序 SETUP PROGRAMMED READ ACCESS EXTENDED HOLD 2 CYCLES ACCESS 4 CYCLES 3 CYCLES 1 CYCLE CLKOUT too AMSx ABE1-0 ADDR19-1 ARE tHARDY tsARDY HARDY ARDY tSARDY DATA 15-0

地址译码:BF531异步读操作时序 5.1 软硬件通信的基本方式