第五章时序逻辑电路 二、集成电JK触发器(7472) 1.逻辑符号 2.特性表 输 入 输出 SD RD CP J K Q+1 注 1J 1K 0 0 X × 不用 不允许 & & R 0 1 X X 1 异步置1 1 0 × 0 异步置0 1 ↓ J1J2J3 CP K1K2 K3RD 保持 1 1 ↓ 0 0 置0 异步复位、置位端 1 1 ↓ 0 1 J=JJ2J3 1 翻转 K=K1·K2·K3

第五章 时序逻辑电路 二、集成电 JK 触发器 (7472) 1. 逻辑符号 Q Q 1J 1K SD J1 J2J3 CP K1 K2 K3RD C1 S & & R – – 异步复位、置位端 1 2 3 J = J J J K K1 K2 K3 = 2. 特性表 保持 置0 置1 翻转 Q n 0 1 Q n 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 不允许 异步置1 异步置0 不用 1 0 0 0 0 1 1 0 Q n+1 SD RD CP J K 注 输 入 输出

第五章时序逻辑电路 三、主要特点 1.主从控制脉冲触发,完善方便; 2.存在一次变化问题,抗干扰能力需提高。 0 一般情况下,要求主从JK触 从 发器在CP=1期间输入信号 1S C11R 的取值应保持不变。 例如: 主 1S C11R XX X X 0 0 0 0 0 0 0 1 1 0 1 0 1 0 1 0 L.1 0 输入变化了2次 X 0 2M只变化1次

第五章 时序逻辑电路 三、 主要特点 1. 主从控制脉冲触发,完善方便; 2. 存在一次变化问题,抗干扰能力需提高。 Q Q 1S C1 1R J CP K S R 1 1S C1 1R & & 从 主 0 1 1 0 0 CP =1期间,只有 J 端能输入, G8 被封锁,不论 K 为何值, R = 0,这将可能引起错误。 例如: CP J K S R QM Q Q 0 1 1 1 0 0 0 1 0 0 1 0 0 1 0 0 0 0 0 1 1 1 0 1 0 1 0 1 0 1 输入变化了 1 0 2 次 QM 只变化1 次 一般情况下,要求主从 JK 触 发器在 CP = 1 期间输入信号 的取值应保持不变

第五章时序逻辑电路 5.2.3.3边沿D触发器 一、 电路组成及符号 二、工作原理 从 Qm+1=S+RQ” SC1 R =D+DQ”=D CP下降沿时刻有效 CP 主 C1 R Sp 画出 CP 曾用符号 异步端

第五章 时序逻辑电路 国标符号 5.2.3.3 边沿 D 触发器 一、电路组成及符号 QM QM CP S R Q Q S C1 R S C1 R 1 1 1 D 从 主 Q Q CP C1 1D D S R SD RD 画出 异步端 二、工作原理 n n Q = S + RQ +1 D DQ D n = + = CP 下降沿时刻有效 曾用符号 国标符号 SD RD SD RD CP S R SD RD

第五章时序逻辑电路 二、集成边沿D触发器 (一)CMOS边沿D触发器CC4013 (双D触发器) 02 92 符号 引出端 2 1312 R 功能 14 1 Vss 特性表 Sp D 65348p0 CP D Rp Sp On+1 注 SD2 D22R0 个 0 0 0 0 同步置0 个 1 0 0 1 同步置1 ↓ × 0 0 On 保持(↓无效) CP上升沿触发 × × 0 1 1 异步置1 × 1 0 0 异步置0 X × 1 不用 不允许

第五章 时序逻辑电路 二、 集成边沿D 触发器 (一) CMOS 边沿 D 触发器 CC4013 (双 D 触发器) 符号 Q Q CP C1 1D D 引出端 功能 Q1 Q1 VDD SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 VSS 6 5 3 4 8 9 11 10 1 2 13 12 14 7 特性表 CP D RD SD Qn+1 注 0 0 0 1 0 0 0 0 0 1 1 0 1 1 0 1 Qn 1 0 不用 同步置0 同步置1 保持(无效) 异步置1 异步置0 不允许 CP 上升沿触发 S R SD RD

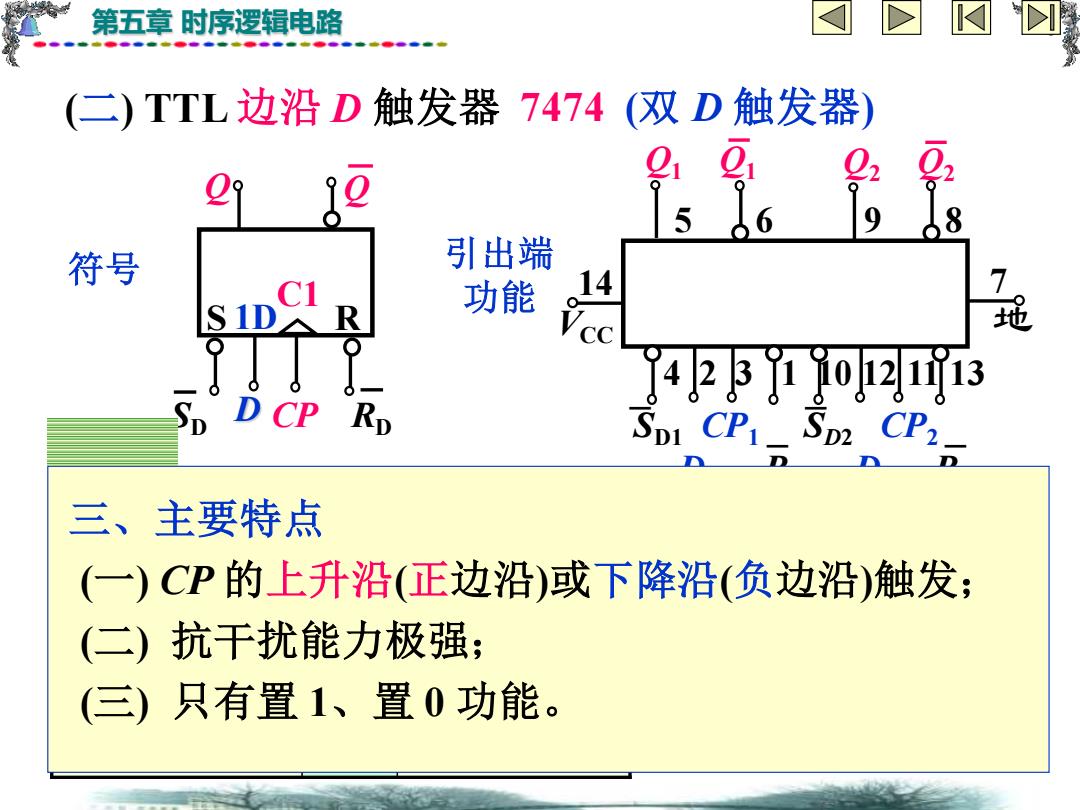

第五章时序逻辑电路 (二)TTL边沿D触发器7474(双D触发器) 0 5 9 8 符号 引出端 C1 功能 14 7 R 地 4231012.113 D CP Rp SDI CP1 三、主要特点 (一)CP的上升沿(正边沿)或下降沿(负边沿)触发: (二)抗干扰能力极强; (三)只有置1、置0功能

第五章 时序逻辑电路 (二) TTL 边沿 D 触发器 7474 (双 D 触发器) 符号 引出端 功能 特性表 CP D RD SD Qn+1 注 0 1 1 1 1 1 1 1 0 1 1 0 1 1 0 1 Qn 0 1 不用 同步置0 同步置1 保持(无效) 异步置0 异步置1 不允许 Q1 Q1 VCC SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 地 4 2 3 1 10 12 11 13 5 6 9 8 14 7 – – – – – – 三、主要特点 (一) CP 的上升沿(正边沿)或下降沿(负边沿)触发; (二) 抗干扰能力极强; (三) 只有置 1、置 0 功能。 Q Q CP C1 1D D S R SD RD