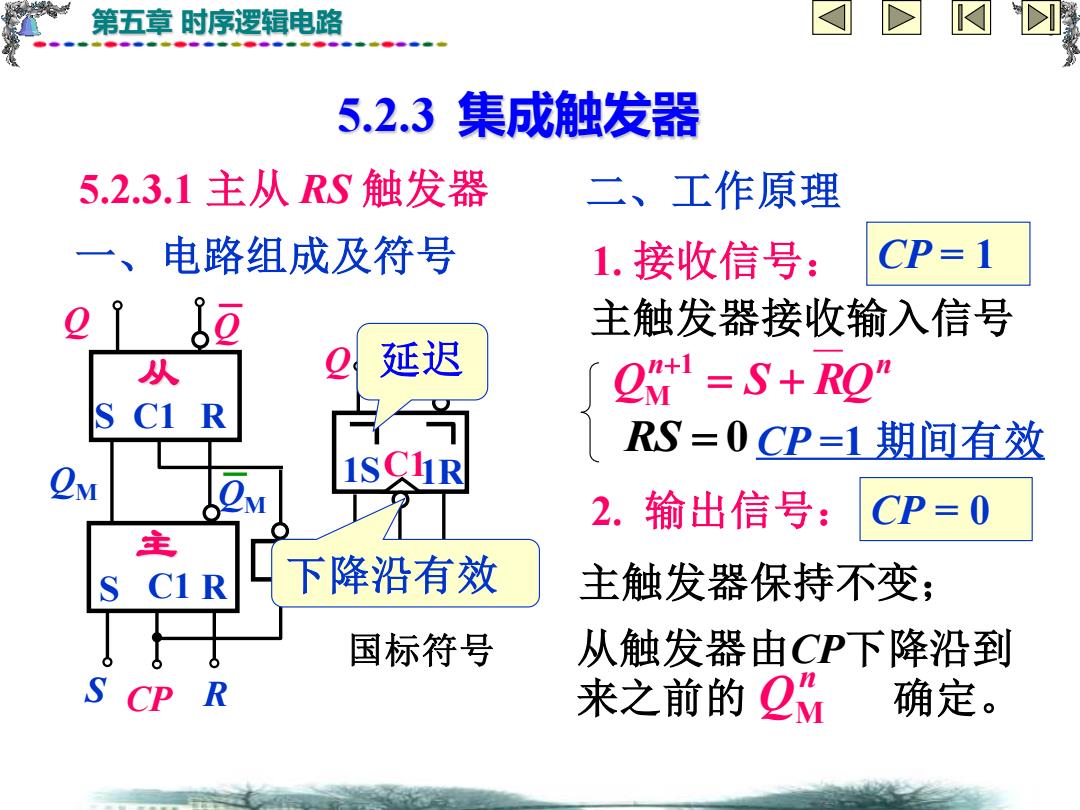

第五章时序逻辑电路 5.2.3 集成触发器 5.2.3.1主从RS触发器 二、工作原理 一、电路组成及符号 1.接收信号: CP=1 g 主触发器接收输入信号 从 延迟 O1=S+0” S C1 R RS=0CP=1期间有效 1SCHR M 2.输出信号: CP=0 主 S C1R 下降沿有效 主触发器保持不变; 国标符号 从触发器由CP下降沿到 R 来之前的24 确定

第五章 时序逻辑电路 5.2.3 集成触发器 5.2.3.1 主从 RS 触发器 一、电路组成及符号 Q Q S C1 R CP S R S R C1 1 QM QM 主 从 国标符号 Q Q 1S 1R S CP R C1 下降沿有效 延迟 二、工作原理 1. 接收信号: CP = 1 主触发器接收输入信号 n n Q = S + RQ +1 M RS = 0 CP =1 期间有效 2. 输出信号: CP = 0 主触发器保持不变; 从触发器由CP下降沿到 来之前的 确定。 n QM

第五章时序逻辑电路 波形图 CP S C1 R R S C1 R CP R

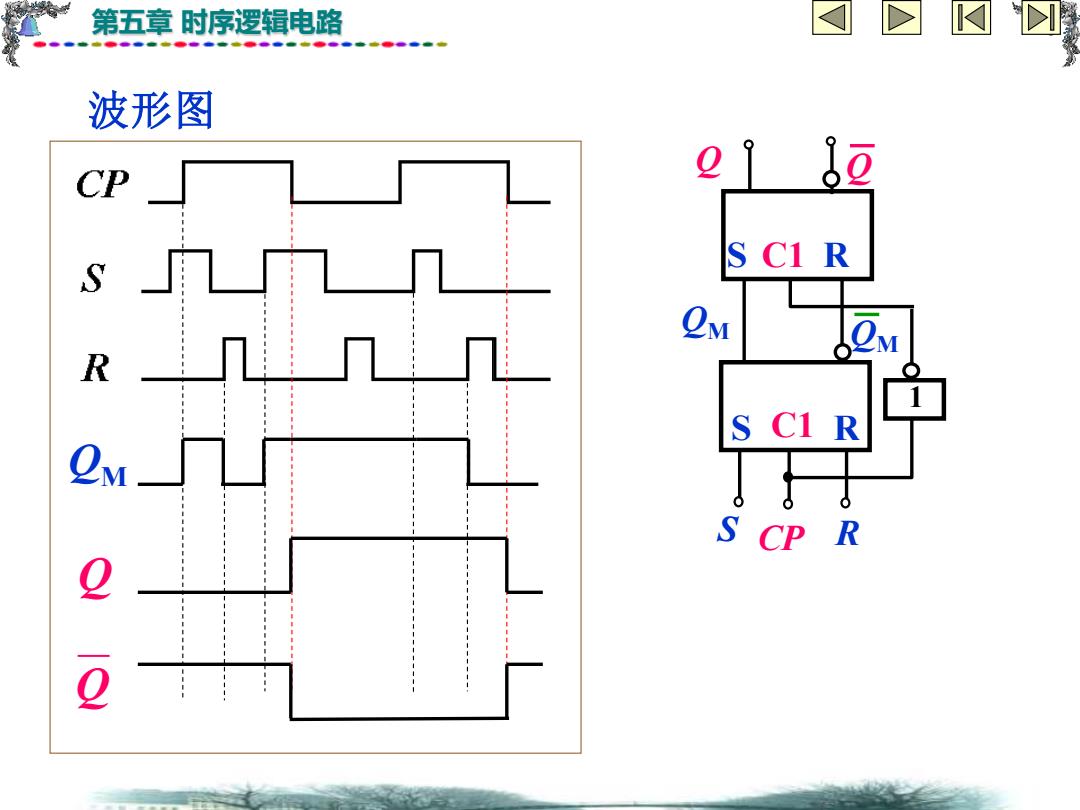

第五章 时序逻辑电路 波形图 QM Q Q Q Q S C1 R CP S R S R C1 1 QM QM

第五章时序逻辑电路 三、主要特点 1.主从控制,时钟脉冲触发。 32 CP=1主触发器接受输入信号 CP )从触发器按照主触发器 的内容更新状态。 从触发器输出端的变化只能发生 在CP的下降沿。 S CP R 2.R、S之间有约束。 CP下降沿到来时,若S=R=0,则可能出现竞态 现象

第五章 时序逻辑电路 三、主要特点 1. 主从控制,时钟脉冲触发。 CP =1 主触发器接受输入信号 从触发器按照主触发器 的内容更新状态。 从触发器输出端的变化只能发生 在 CP 的下降沿。 2. R、S 之间有约束。 CP 下降沿到来时,若 S = R = 0,则可能出现竞态 现象。 CP Q Q S C1 R CP S R S R C1 1 QM QM

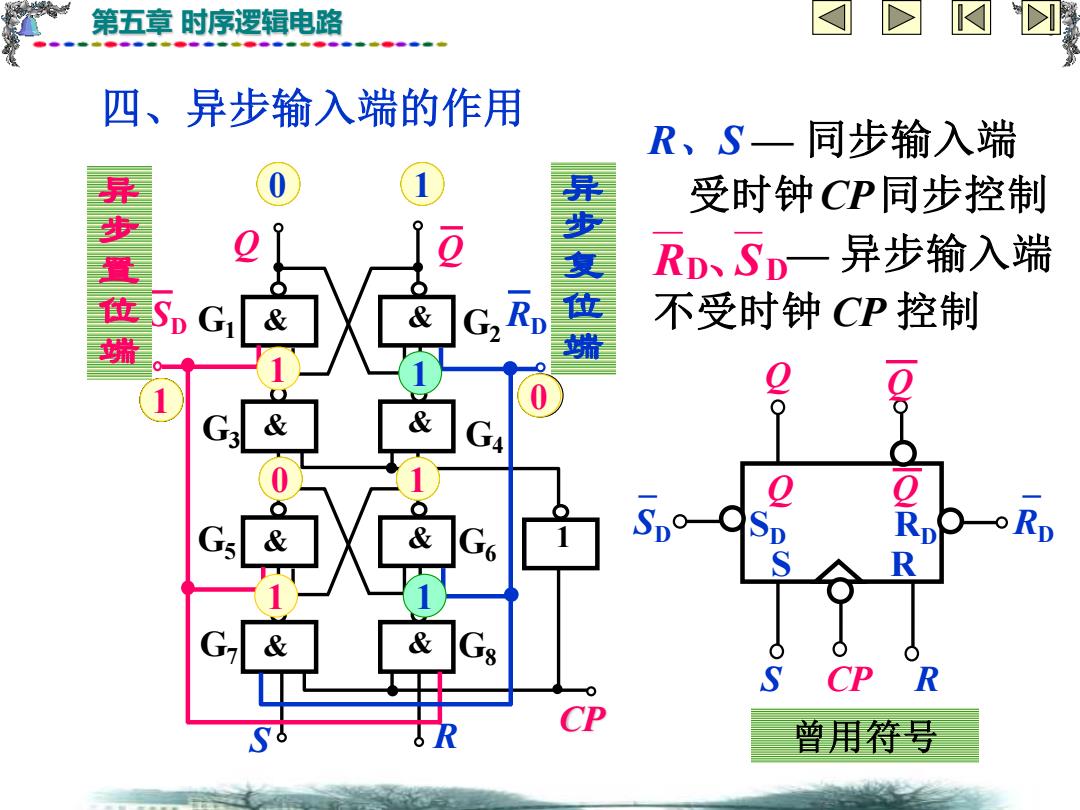

第五章时序逻辑电路 四、异步输入端的作用 R、S一同步输入端 受时钟CP同步控制 RD、SD一异步输入端 & & 异步复位蜡 不受时钟CP控制 & & & & R & & 8 S CP R CP 曾用符号

第五章 时序逻辑电路 四、异步输入端的作用 G7 CP Q R & & Q G3 & & S G2 G4 & & & & G6 G8 1 G1 G5 R、S — 同步输入端 受时钟CP同步控制 SD RD RD、S D— 异步输入端 不受时钟 CP 控制 0 1 1 1 1 0 1 0 1 0 0 1 0 1 1 直 1 接 置 位 端 直 接 复 位 端 异 步 置 位 端 异 步 复 位 端 国标符号 SD S CP R RD – – Q Q SD1S 1RRD C1 曾用符号 – – SD RD S CP R Q Q S R SD RD Q Q

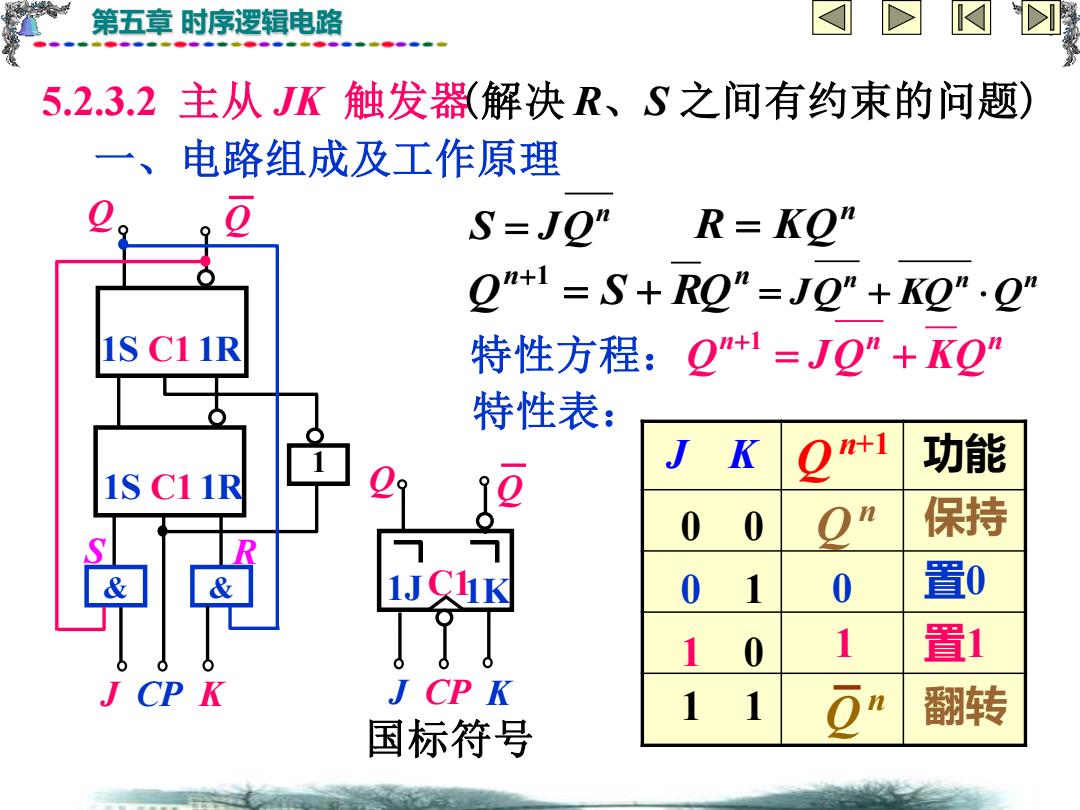

第五章时序逻辑电路 5.2.3.2主从JK触发器解决R、S之间有约束的问题) 一、 电路组成及工作原理 S=J2” R=KQ” 2m+1=S+R0"=J0"+KQ”.Q 1S C11R 特性方程:Q”+1=JQ”+KQ” 特性表: J K +1 功能 1S C11R 0 保持 0 0 置0 1 置1 翻转 国标符号

第五章 时序逻辑电路 5.2.3.2 主从 JK 触发器(解决 R、S 之间有约束的问题) 一、电路组成及工作原理 Q Q 1S C1 1R J CP K S R 1 1S C1 1R & & Q Q 1J 1K J CP K C1 国标符号 n S = JQ n R = KQ n n Q = S + RQ +1 n n n = JQ + KQ Q n n n Q = JQ + KQ 特性方程: +1 特性表: J K Q n+1 功能 0 0 0 1 1 0 1 1 Q n 0 1 Q n 保持 置0 置1 翻转