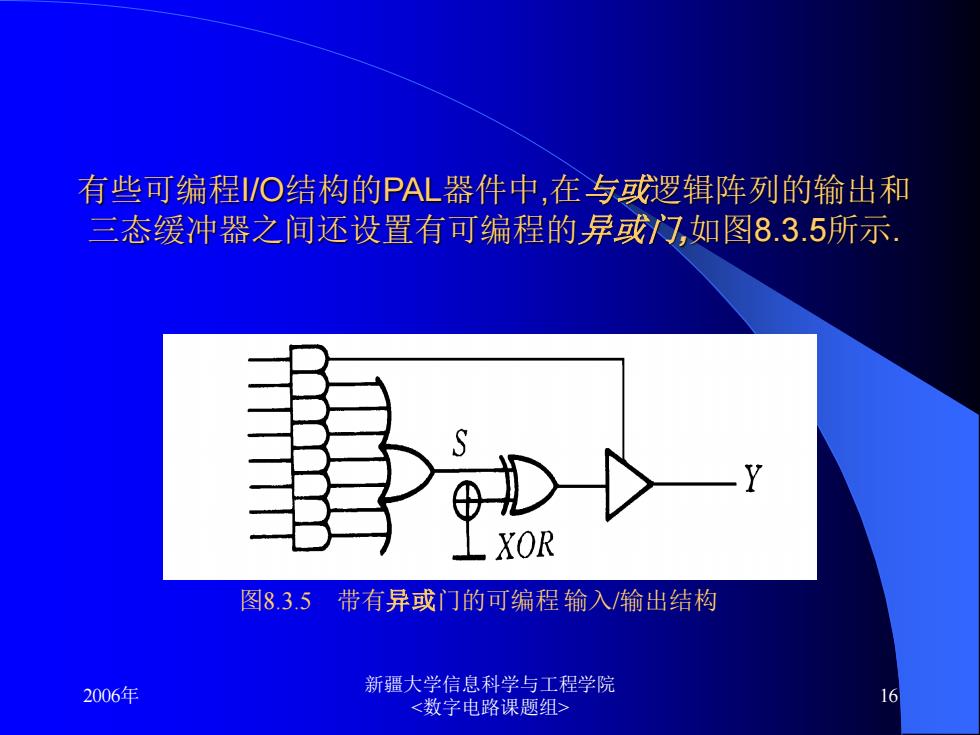

有些可编程I/O结构的PAL器件中,在与或逻辑阵列的输出和 三态缓冲器之间还设置有可编程的异或门,如图8.3.5所示. 图83.5带有异或门的可编程输入/输出结构 2006年 新疆大学信息科学与工程学院 16 <数字电路课题组

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 16 有些可编程I/O结构的PAL器件中,在与或逻辑阵列的输出和 三态缓冲器之间还设置有可编程的异或门,如图8.3.5所示. 图8.3.5 带有异或门的可编程 输入/输出结构

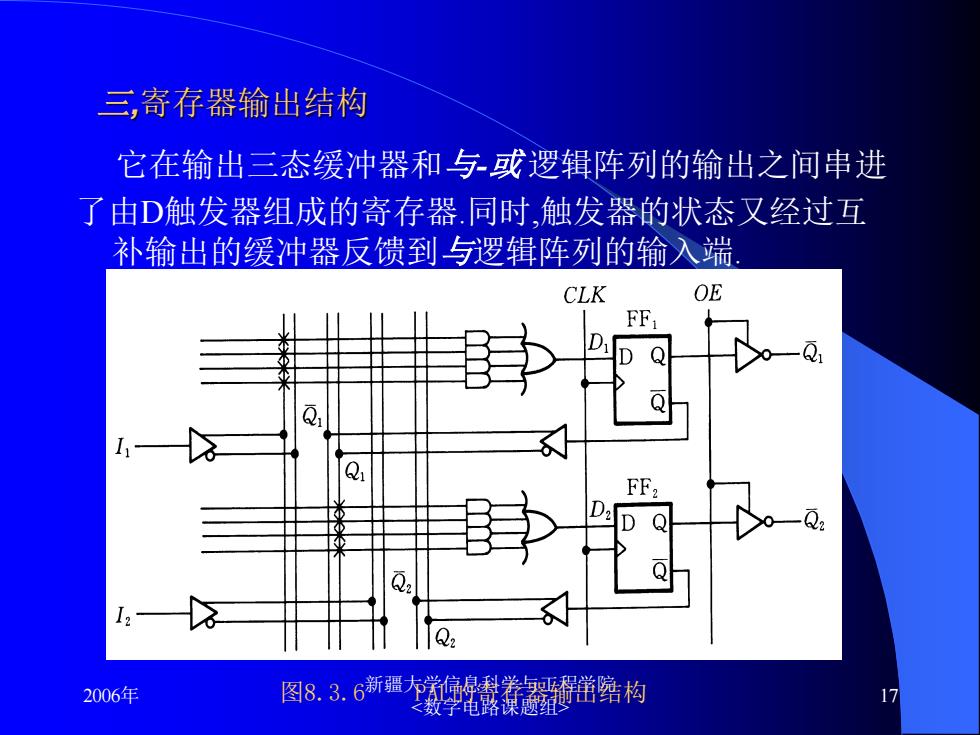

三,寄存器输出结构 它在输出三态缓冲器和与或逻辑阵列的输出之间串进 了由D触发器组成的寄存器.同时,触发器的状态又经过互 补输出的缓冲器反馈到与逻辑阵列的输入端 CLK OE FF2 )Q 2006年 图8.3.6新疆学偏载着霸递路构 <数学电路课题心

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 17 三,寄存器输出结构 它在输出三态缓冲器和与-或 逻辑阵列的输出之间串进 了由D触发器组成的寄存器.同时,触发器的状态又经过互 补输出的缓冲器反馈到与逻辑阵列的输入端. 图8.3.6 PAL的寄存器输出结构

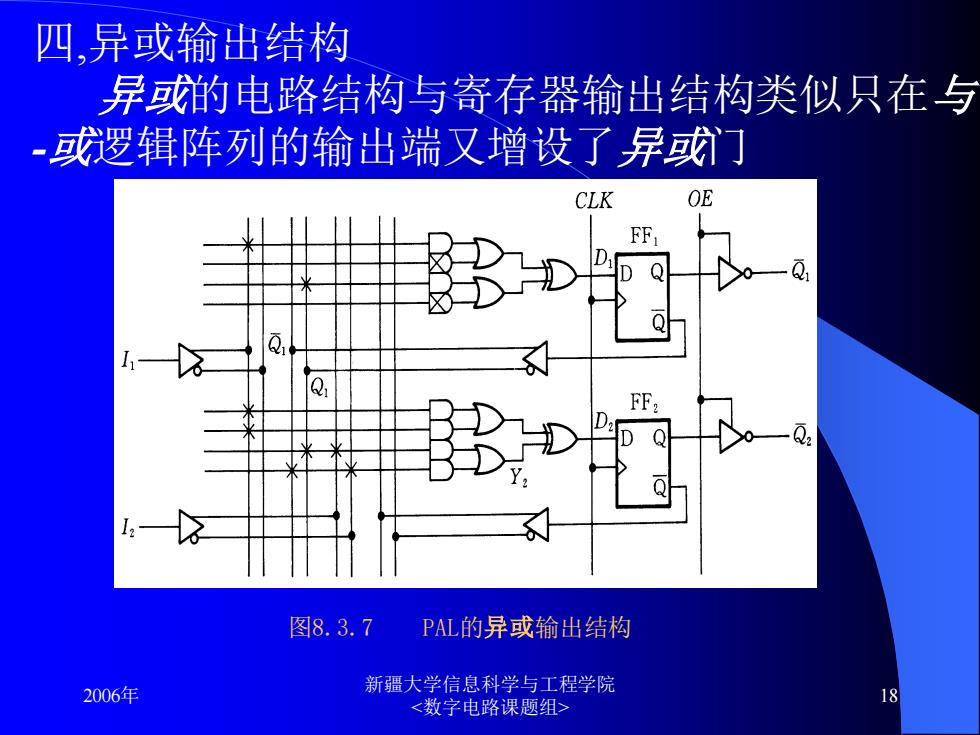

四,异或输出结构 异或的电路结构与寄存器输出结构类似只在与 -或逻辑阵列的输出端又增设了异或门 CLK OE Q Q Q Q BD 图8.3.7 PAL的异或输出结构 2006年 新疆大学信息科学与工程学院 18 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 18 四,异或输出结构 异或的电路结构与寄存器输出结构类似只在与 -或逻辑阵列的输出端又增设了异或门 图8.3.7 PAL的异或输出结构

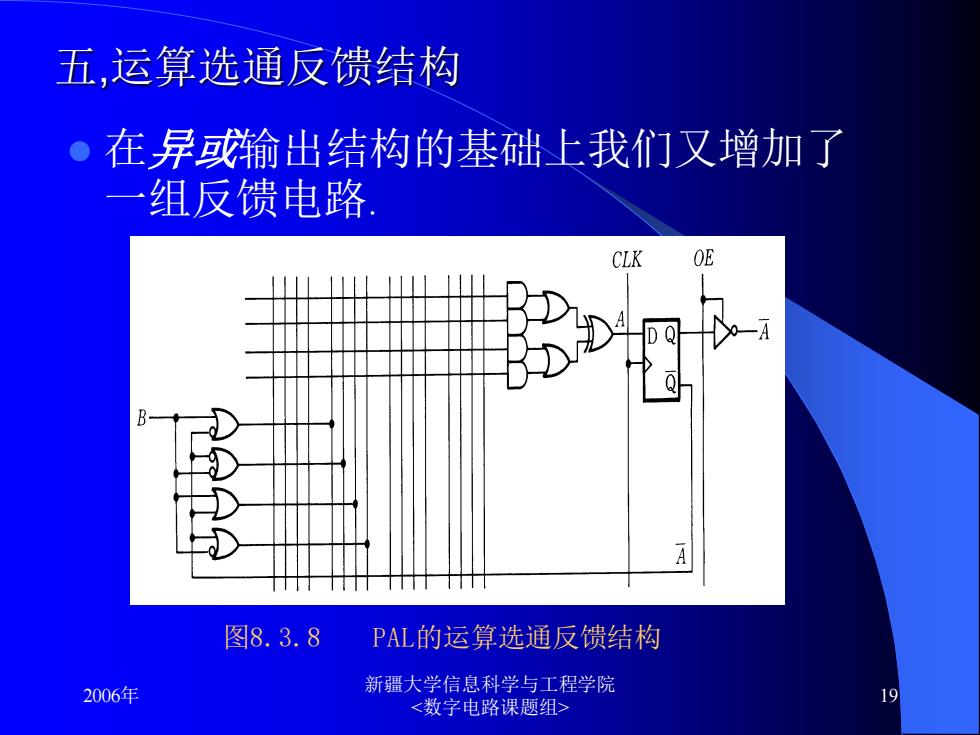

五,运算选通反馈结构 。在异或输出结构的基础上我们又增加了 一组反馈电路. CLK OE A 图8.3.8 PAL的运算选通反馈结构 2006年 新疆大学信息科学与工程学院 19 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 19 五,运算选通反馈结构 ⚫ 在异或输出结构的基础上我们又增加了 一组反馈电路. 图8.3.8 PAL的运算选通反馈结构

8.3.3PAL的应用举例 2006年 新疆大学信息科学与工程学院 20 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 20 8.3.3 PAL 的应用举例