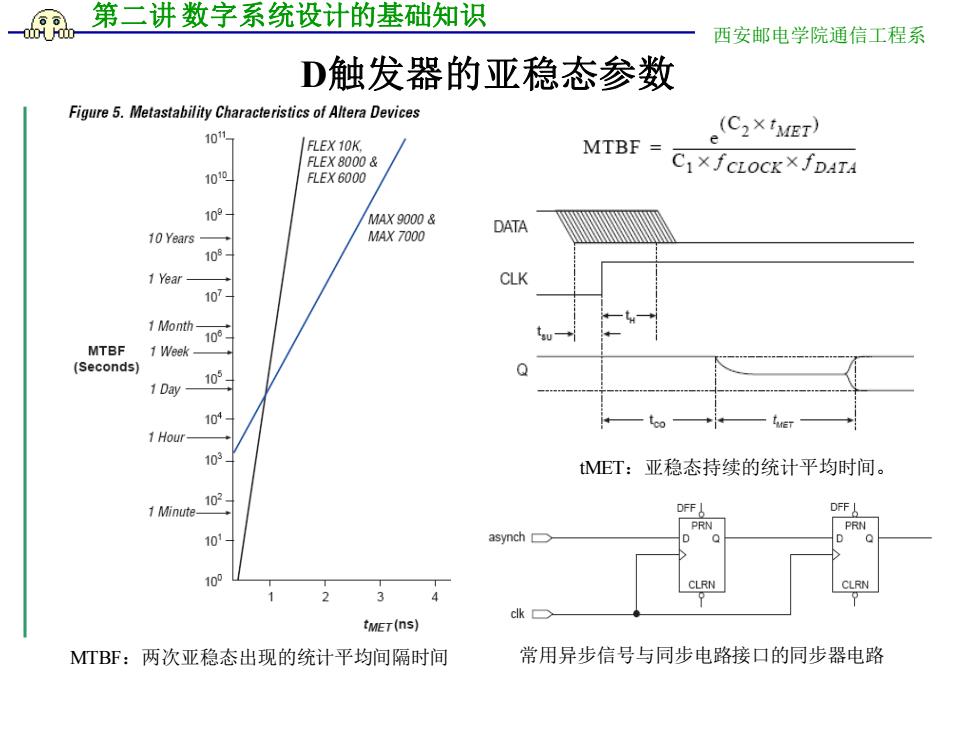

66 U应 第二讲数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态参数 Figure 5.Metastability Characteristics of Altera Devices 101 e(C2XIMEr) FLEX 10K. MTBF FLEX 8000 1010 FLEX 6000 Cx fCLOCKX JDATA 109 MAX9000& DATA 10 Years MAX 7000 108 1 Year- CLK 107- 1 Month 105 MTBF 1 Week (Seconds) 1 Day- 心 104 co T 1 Hour- 103 tM正T:亚稳态持续的统计平均时间。 102 1 Minute- DFF DFF PRN PRN 10 asynch D D 100 CLRN CLRN clk tMET(ns) MTBF:两次亚稳态出现的统计平均间隔时间 常用异步信号与同步电路接口的同步器电路

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态参数 MTBF:两次亚稳态出现的统计平均间隔时间 tMET:亚稳态持续的统计平均时间。 常用异步信号与同步电路接口的同步器电路

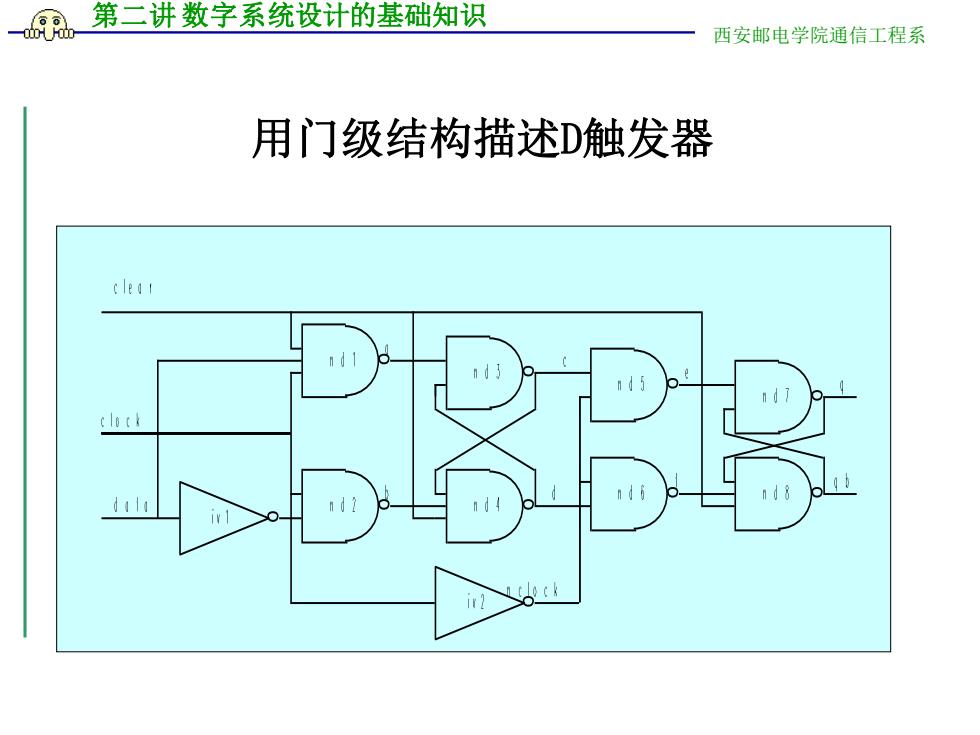

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 用门级结构描述D触发器 clear 11 15 11 n1 n d 6 11 ir

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 用门级结构描述D触发器

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的D触发器门级结构描述 module my dff(data,clock,clear,q,qb); input data,clock,clear;//输入端口 output q,qb; /输出端口 nand nd1(a,data,clock,clear),//模块调用 nd2 (b,ndata,clock) nd4(d,c,b,clear), nd5 (e, c,nclock), 按位置连接 樊 nd6 (f,d,nclock), 信号线 nd8 (qb,q,f,clear); nand nd3(c,a,d), nd7 (a,e,qb) wire类型可以 not ivl(ndata,data), 隐含说明 iv2(nclock,clock); endmodule

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 module my_dff(data,clock,clear,q,qb); input data,clock,clear; //输入端口 output q,qb; //输出端口 nand nd1(a,data,clock,clear),//模块调用 nd2(b,ndata,clock), nd4(d,c,b,clear), nd5(e,c,nclock), nd6(f,d,nclock), nd8(qb,q,f,clear); nand nd3(c,a,d), nd7(q,e,qb); not iv1(ndata,data), iv2(nclock,clock); endmodule Verilog的D触发器门级结构描述 模 块 按位置连接 信号线 wire类型可以 隐含说明

6 第二讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilogl的D触发器功能(行为)描述 module my_dff(data,clock,clear,q,qb); input data,clock,clear; output q,qb;/wire变量类型 上升沿 regq;/reg变量类型 事件 @事件控制 操作符 always @(negedge clear or posedge clock) begin Always if(!clear)g<=1b0;//非阻塞赋值 块语句 else q<=data; end assign qb=~q;/并行赋值语句 If顺序 语句 endmodule

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的D触发器功能(行为)描述 module my_dff(data,clock,clear,q,qb); input data,clock,clear; output q,qb; //wire变量类型 reg q; //reg变量类型 always @(negedge clear or posedge clock) begin if(!clear) q<=1’b0; //非阻塞赋值 else q<=data; end assign qb=~q; // 并行赋值语句 endmodule Always 块语句 @事件控制 操作符 上升沿 事件 If 顺序 语句

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog描述的抽象级别 。Verilog语言本身提供了各种层次抽象的表述能力, 可以在不同层次上描述同一个电路系统。 。行为级:系统功能和算法的Verilog描述,与电路实 现结构无关。 RTL级:基于寄存器和其间组合逻辑功能的Verilog 描述,是行为描述的低级形式。RTL级描述是当前 可综合设计的主流。 ·门级:逻辑结构的Verilog描述。 。开关级:具体的晶体管物理器件的描述

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog描述的抽象级别 Verilog 语言本身提供了各种层次抽象的表述能力, 可以在不同层次上描述同一个电路系统。 行为级:系统功能和算法的Verilog描述,与电路实 现结构无关。 RTL级:基于寄存器和其间组合逻辑功能的Verilog 描述,是行为描述的低级形式。 RTL级描述是当前 可综合设计的主流。 门级:逻辑结构的Verilog描述。 开关级:具体的晶体管物理器件的描述