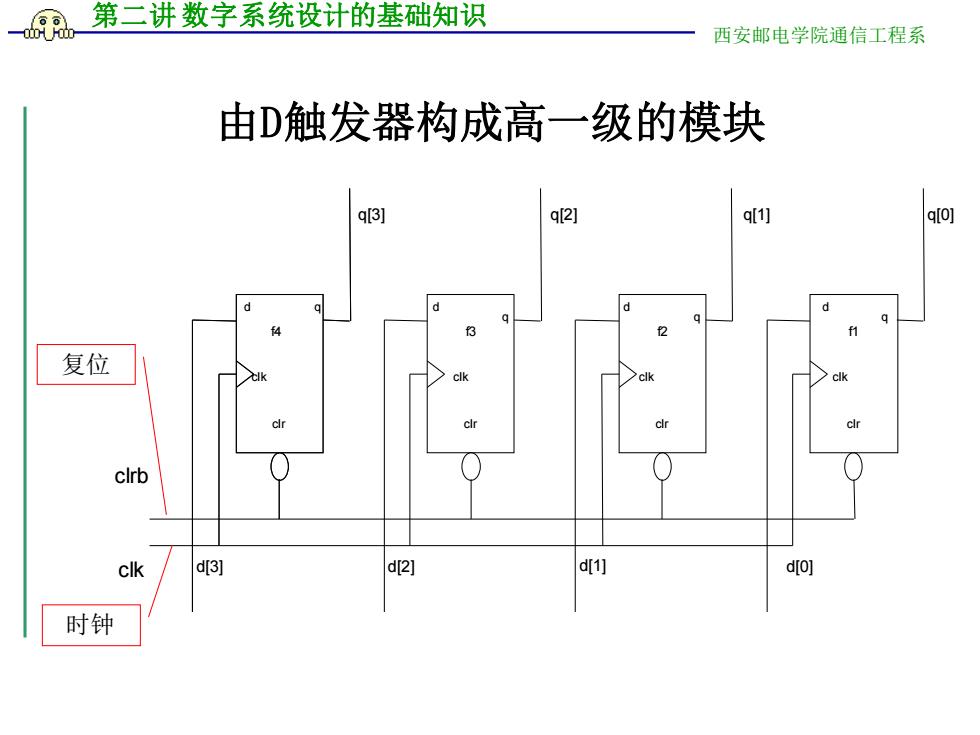

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 由D触发器构成高一级的模块 q[3] q[2] q1] q[0] d 9 d d d q q q f3 复位 clk d clr clrb clk d[3] d2] d1) d[o] 时钟

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 由D触发器构成高一级的模块 clr d q clk clr d q clk clr d q clk q[0] d[0] clr d q clk d[3] d[2] q[3] q[2] q[1] d[1] clrb clk f4 f3 f2 f1 复位 时钟

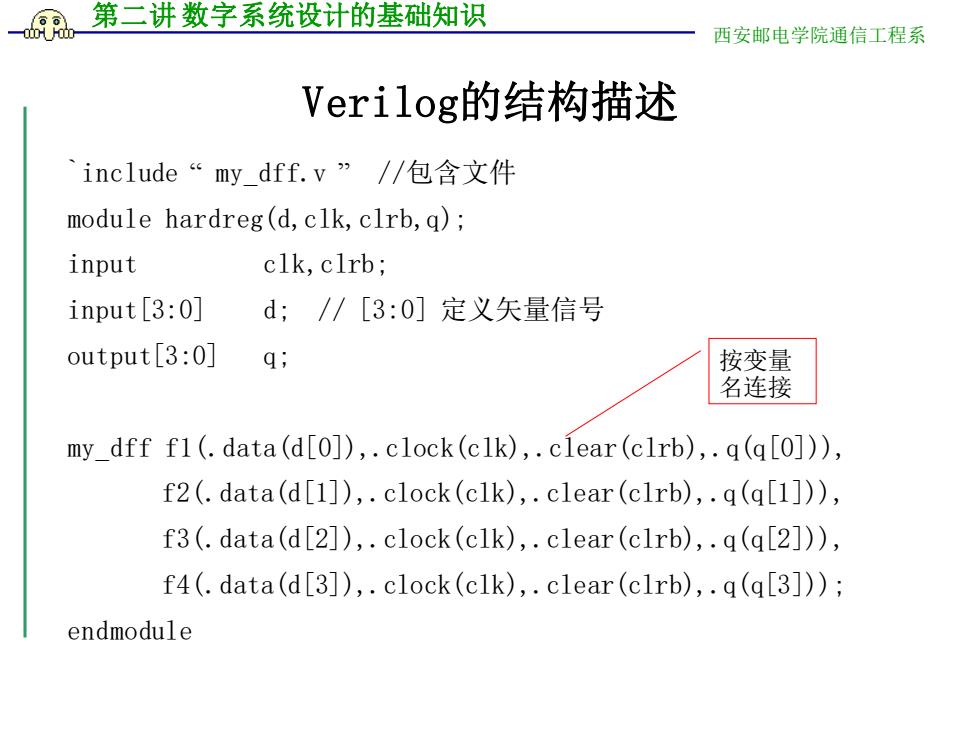

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的结构描述 include“my dff.v”/包含文件 module hardreg(d,clk,clrb,q); input clk,clrb; input [3:0] d;//[3:0]定义矢量信号 output[3:0] q; 按变量 名连接 my_dff f1(.data(d[O]),.clock(clk),.clear(clrb),.q(q[O])), f2(.data(d[1]),.clock(clk),.clear(clrb),.q(q[1])), f3(.data(d[2]),.clock(clk),.clear(clrb),.q(q[2])), f4(.data(d[3]),.clock(clk),.clear(clrb),.q(q[3])); endmodule

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的结构描述 `include “ my_dff.v ” //包含文件 module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; // [3:0] 定义矢量信号 output[3:0] q; my_dff f1(.data(d[0]),.clock(clk),.clear(clrb),.q(q[0])), f2(.data(d[1]),.clock(clk),.clear(clrb),.q(q[1])), f3(.data(d[2]),.clock(clk),.clear(clrb),.q(q[2])), f4(.data(d[3]),.clock(clk),.clear(clrb),.q(q[3])); endmodule 按变量 名连接

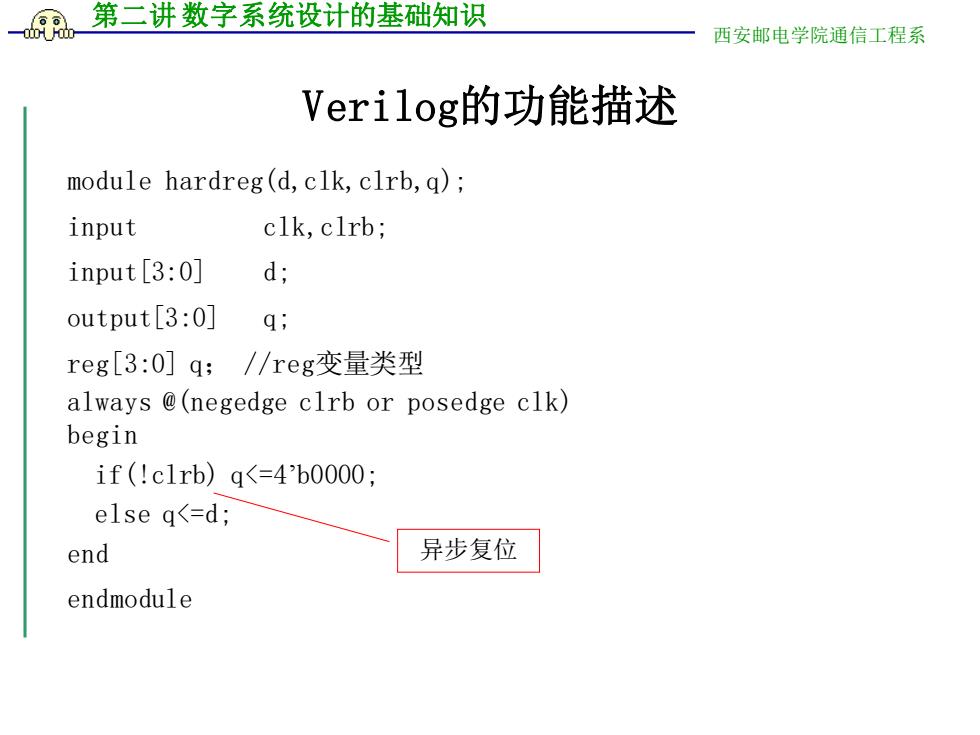

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module hardreg(d,clk,clrb,q); input clk,clrb; input [3:0] d; output[3:0] q; reg[3:0]q;/reg变量类型 always @(negedge clrb or posedge clk) begin if(!clrb)q<=4'b0000; else q<=d; end 异步复位 endmodule

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; output[3:0] q; reg[3:0] q; //reg变量类型 always @(negedge clrb or posedge clk) begin if(!clrb) q<=4’b0000; else q<=d; end endmodule 异步复位