《DL语言硬件设计》实验指导书 实验一:设计输入与门级结构建模仿真 一、实验目的: 1、掌握简单门级结构建模电路的设计方法。 2、初步掌握ModelSim6.0软件的基本操作与应用。 3、初步了解verilog建模仿真的设计全过程。 二、实验设备: PC机 ModelSim6.0开发软件 三、试验要求:设计输入(2学时) 学习使用ModelSim6.0设计软件。学习文本编辑器使用,掌握 文本编辑器的输入方法,完成本讲实例门级2选1多路选择器结 构建模的输入和门级2位全加器器结构建模的输入,并完成仿真。 四、实验步骤: ModelSim6.0设计输入具体步骤: 在这个实验中我们通过一个简单的实例来演示如何使用 ModelSim6.0。下面我们就具体来实现这一设计 以下内容为程序代码: 门级结构描述的2选1MUX module user mux(out,a,b,sel); output out; input a,b,sel; not (sel_,sel); and (al,a,sel_), (a2,b,se1); or (out,al,a2); endmodule 2选1多路选择器的仿真 timescale 1ns/1ns 第1页共49页

《HDL 语言硬件设计》实验指导书 第 1 页 共 49 页 实验一:设计输入与门级结构建模仿真 一、实验目的: 1、掌握简单门级结构建模电路的设计方法。 2、初步掌握 ModelSim6.0 软件的基本操作与应用。 3、初步了解 verilog 建模仿真的设计全过程。 二、实验设备: PC 机 ModelSim6.0 开发软件 三、试验要求:设计输入(2 学时) 学习使用 ModelSim6.0 设计软件。学习文本编辑器使用,掌握 文本编辑器的输入方法,完成本讲实例门级 2 选 1 多路选择器结 构建模的输入和门级 2 位全加器器结构建模的输入,并完成仿真。 四、实验步骤: ModelSim6.0 设计输入具体步骤: 在这个实验中我们通过一个简单的实例来演示如何使用 ModelSim6.0。下面我们就具体来实现这一设计 以下内容为程序代码: 门级结构描述的2 选1MUX module user_mux(out,a,b,sel); output out; input a,b,sel; not (sel_,sel); and (a1,a,sel_), (a2,b,sel); or (out,a1,a2); endmodule 2 选1 多路选择器的仿真 `timescale 1ns/1ns

《DL语言硬件设计》实验指导书 module mux tp; reg a,b,sel; wire out; user_muxm1(out,a,b,sel);//调用待测试模块 initial begin a=1'b0;b=1'b0;se1=1'b0: #5se1-1'b1: #5a=1'b1;se1=1'b0; #5se1=-1b1; #5a=1'b0;b=1'b1;se1-1'b0; #5se1=1'b1: #5a=1'b1;b=1'b1;se1-1'b0: #53e1=1'b1; end initial $monitor($time,"a=8b b=8b sel=$b out=8b",a,b,sel,out); endmodu le 第一步:建立新设计项目 1)、双击桌面上ModelSim6.0的图标,启动ModelSim6.0软件。 第2页共49页

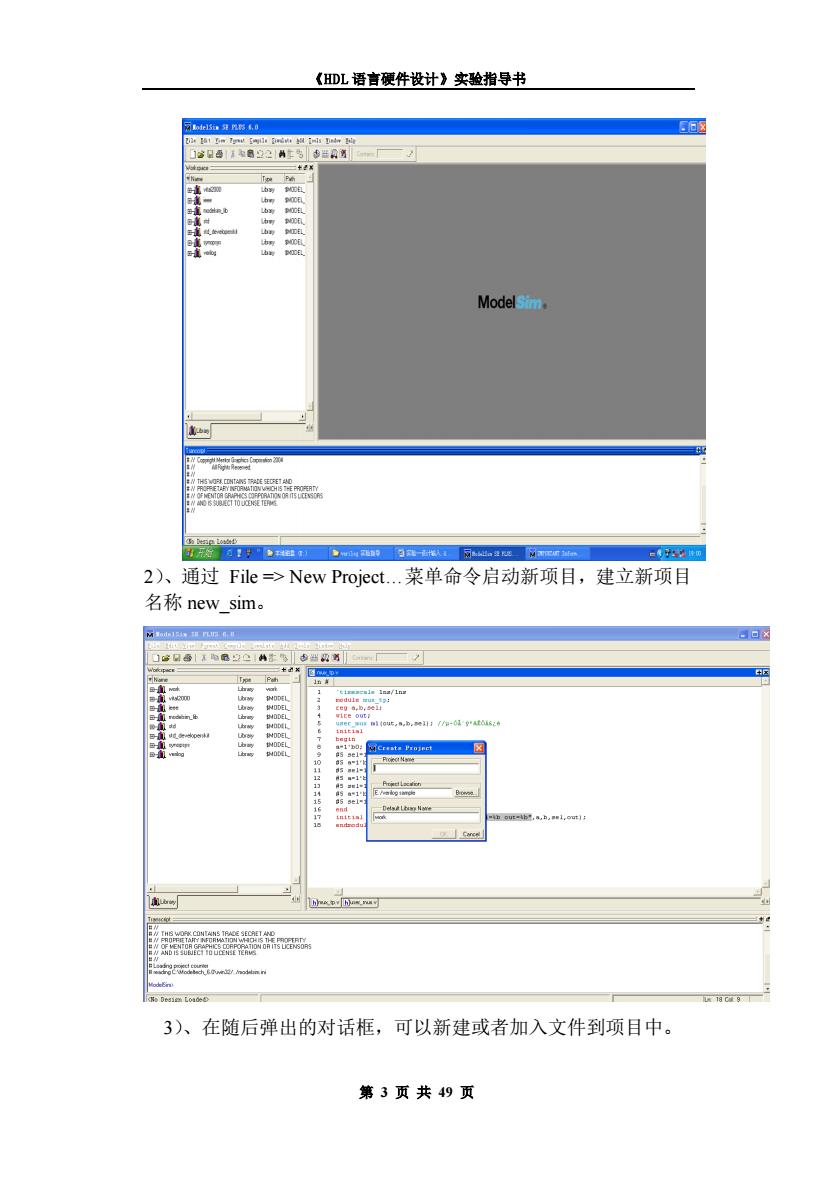

《HDL 语言硬件设计》实验指导书 第 2 页 共 49 页 module mux_tp; reg a,b,sel; wire out; user_mux m1(out,a,b,sel); //调用待测试模块 initial begin a=1'b0; b=1'b0; sel=1'b0; #5 sel=1'b1; #5 a=1'b1; sel=1'b0; #5 sel=1'b1; #5 a=1'b0; b=1'b1; sel=1'b0; #5 sel=1'b1; #5 a=1'b1; b=1'b1; sel=1'b0; #5 sel=1'b1; end initial $monitor($time,"a=%b b=%b sel=%b out=%b",a,b,sel,out); endmodule 第一步:建立新设计项目 1)、双击桌面上 ModelSim6.0 的图标,启动 ModelSim6.0 软件

《DL语言硬件设计》实验指导书 E 山公日每引1如扇22的年号多强骨 b到 h啊 MOE 山到 MDEL 0 力同 到00L Model 小 o Derip Losdd :m 2)、通过File=>New Project.菜单命令启动新项目,建立新项目 名称new sim. -1 40 mitoue,n,b,e://-01 9Atols2o Cresta Projnet 69102 图 15672 houEb”,h,■e1,at: 18Ct9 3)、在随后弹出的对话框,可以新建或者加入文件到项目中。 第3页共49页

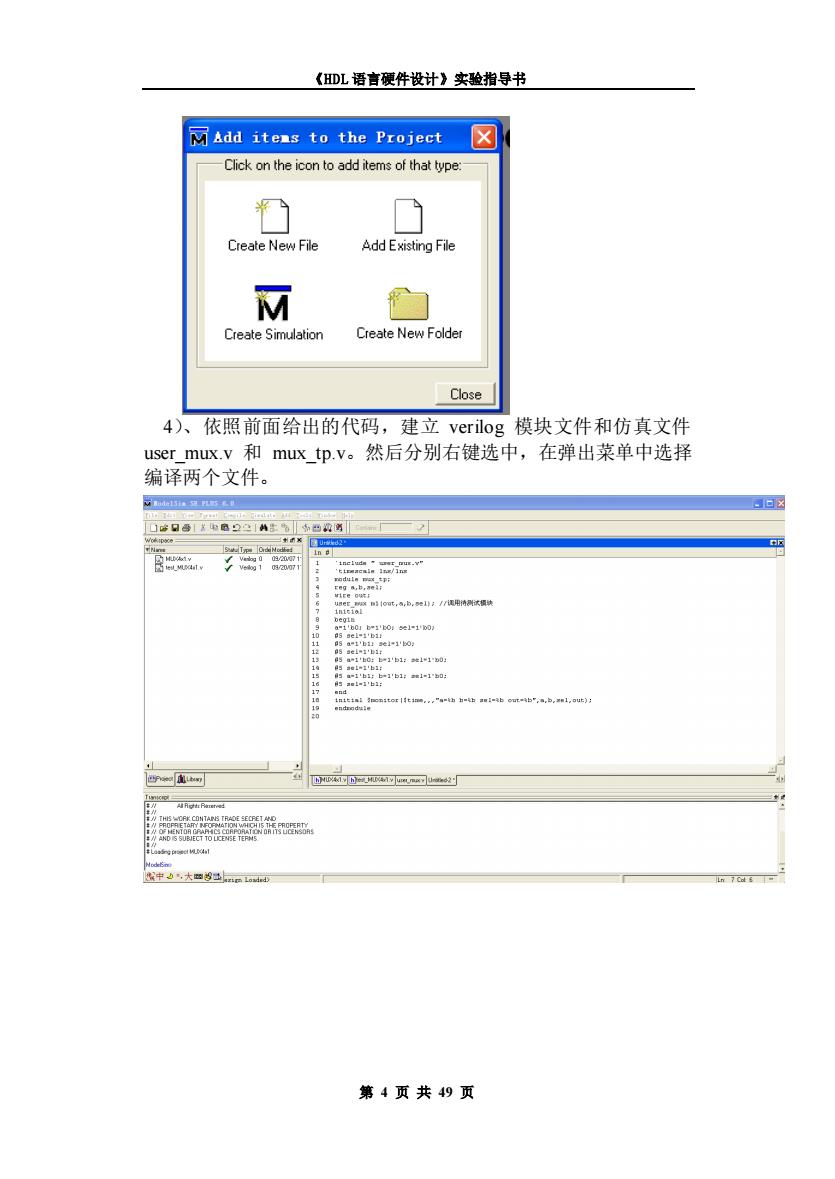

《HDL 语言硬件设计》实验指导书 第 3 页 共 49 页 2)、通过 File => New Project.菜单命令启动新项目,建立新项目 名称 new_sim。 3)、在随后弹出的对话框,可以新建或者加入文件到项目中

《DL语言硬件设计》实验指导书 MAdd items to the Project Click on the icon to add items of that type: Create New File Add Existing File M Create Simulation Create New Folder Close 4)、依照前面给出的代码,建立verilog模块文件和仿真文件 user_mux.v和mux_tp.v。然后分别右键选中,在弹出菜单中选择 编译两个文件。 Vadeli PLES C 回 山哈日香鱼24出吃克巴物腾 区 n a 10 15 1'b1:地1130: 1'b1:1-10 16 ",.,u) n Loasng proect帆4l 家中,大题9r:Losded) Lm 7 Cdl5 第4页共49页

《HDL 语言硬件设计》实验指导书 第 4 页 共 49 页 4)、依照前面给出的代码,建立 verilog 模块文件和仿真文件 user_mux.v 和 mux_tp.v。然后分别右键选中,在弹出菜单中选择 编译两个文件

《DL语言硬件设计》实验指导书 ☑■ode1 Sim SE PL.Ds6.n 昆i1。Edit View Format Compil。imulat。Add工ools Yindow上lp New 色1岭鲁‖幽风送 Ooen. Close 出函 Untitled-2 Jmport Statu Type Orde Modified 1n# 1 Save 09/20/071 include m user mux.v" timescale 1ns/ins Save As. module mux tp: 9 reg a,b,sel: Delete wire out: Change Directory. 6 user_mu×m1(out,a,b,sel)://酒用待测 Source Directory. begin a=1"b0:b-1'b0:se1=1'b0: Enyironment 0 #5se1-1'b1: Add to Project 1 #5a-1b1:se1-1'b0: #5se1-1b1: Page Setup 13 #5a-1·b0:h-1'h1:se1=1'b0: Print. #5se1-1'b1: Print Postscipl 5 #5a-1b1:b-1+h1:se1-1b0: #5se1-1*b1: Recent Directories 17 end Recent Projects initial $monitor (time,"a-sb b: Quit endmodule 4 Project ILibrary h]MUX4x1.v hest_MUX4x1.v user_muxv Untitled-2- All Rights Reserved. THIS WORK CONTAINS TRADE SECRET AND Save As ②☒ 保存在): MUX4x1 习中色心国 d 向Woxk 日K4x1.cr,nti 我最近的文档 WX4x1.mpf X4x1. WUX4x1.v.bak 桌 otest_MX4x1.v 园test_MUX4x1.v.bak 圆user_mu.V 我的文档 的vsin.Wlf 即 我的电脑 网上邻居 文件名) 世t 保存⑤) 保存类型①) 11Fi1es体,*) 习 取消 第5页共49页

《HDL 语言硬件设计》实验指导书 第 5 页 共 49 页