第二讲数字系统设计的基础知识 西安邮电学院通信工程系 逻辑门相关基本概念 。四值逻辑:逻辑值1、逻辑值0、未知值X、高阻值Z。 。逻辑器件延时:0=>1上升延时,1=>0下降延时, 0、1、x=>Z关断延时。惯性延时。 逻辑路径延时:逻辑器件间互连线的延时。传输延时。 逻辑器件负载模型:CMOS逻辑器件的负载可等效为RC 电路,负载越多,电容越大。 逻辑器件扇出:逻辑器件输出连接的负载数目为扇出。 如一个非门的输出连接了三个逻辑门的输入,则称该非 门的扇出为3。扇出越大,负载越大,等效传输延时越大

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 逻辑门相关基本概念 四值逻辑:逻辑值1、逻辑值0、未知值X、高阻值Z。 逻辑器件延时:0=>1 上升延时, 1=>0 下降延时, 0、1、x=>Z 关断延时。惯性延时。 逻辑路径延时:逻辑器件间互连线的延时。传输延时。 逻辑器件负载模型:CMOS逻辑器件的负载可等效为RC 电路,负载越多,电容越大。 逻辑器件扇出:逻辑器件输出连接的负载数目为扇出。 如一个非门的输出连接了三个逻辑门的输入,则称该非 门的扇出为3。扇出越大,负载越大,等效传输延时越大

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 2)触发器 嫌我们把具有存储记忆一位二值信号功能的基本单元电 路称为触发器。 根据触发器电路结构和功能的不同,可以分为RS触发 器、JK触发器、D触发器、T触发器和T'触发器等。 在目前的数字系统同步电路设计中,一般只使用D触发 器。 在异步电路设计中用到RS触发器和其它触发器

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 2) 触发器 我们把具有存储记忆一位二值信号功能的基本单元电 路称为触发器。 根据触发器电路结构和功能的不同,可以分为RS触发 器、JK触发器、D触发器、T触发器和T′触发器等。 在目前的数字系统同步电路设计中,一般只使用D触发 器。 在异步电路设计中用到RS触发器和其它触发器

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 D触发器 D(t) Q(+T) D(t) D D Q(1) 0 0 CLK CLK Q() Q什T)=D() Clear 建立 保持 时间 时间 (a) (b) (c) (a)符号;b)功能特点;(c)建立、保持时间 ●建立时间一在时钟跳变前数据必须保持稳定(无跳变) 的时间。 。保持时间一在时钟跳变后数据必须保持稳定的时间

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 (a) 符号; (b) 功能特点 ;(c)建立、保持时间 建立时间——在时钟跳变前数据必须保持稳定(无跳变) 的时间。 保持时间——在时钟跳变后数据必须保持稳定的时间。 D触发器 D(t) D D Q Q Q(t) CLK Q(t) (a) (b) 0 1 1 D(t) Q(t+T) 0 Q(t+T )=D(t) D CLK 建立 时间 保持 时间 (c) Clear

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态(metastability)概念 当某个异步信号被送入一个同步触发器时,就可能发生亚稳态现 象。如图所示,当输入D与时钟CLK1同时在亚稳态时间窗内翻转 时,D触发器的输出可能出现一种不是1,也不是0的不确定中间 状态,并可能维持一段时间,称亚稳态。 异步输入 输出 亚稳态 亚稳态 时间窗 CLKI CLK1

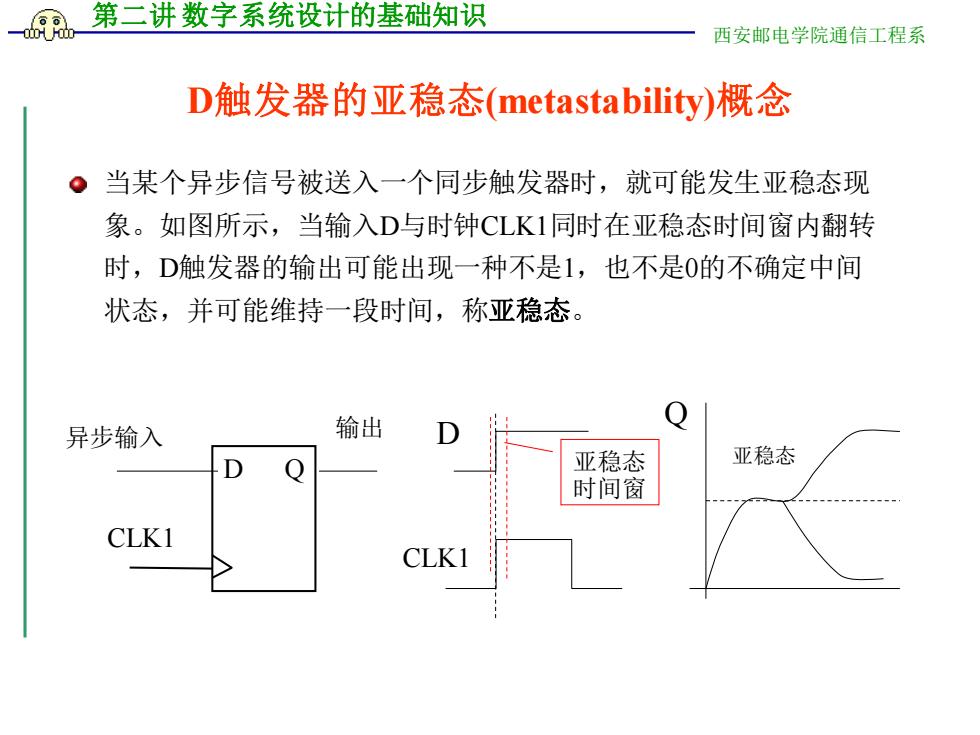

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态(metastability)概念 当某个异步信号被送入一个同步触发器时,就可能发生亚稳态现 象。如图所示,当输入D与时钟CLK1同时在亚稳态时间窗内翻转 时,D触发器的输出可能出现一种不是1,也不是0的不确定中间 状态,并可能维持一段时间,称亚稳态。 D Q CLK1 异步输入 输出 CLK1 D Q 亚稳态 亚稳态 时间窗

第二讲数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态特性 。亚稳态是触发器的固有特性,不可能消除,只能尽量减小 其的持续时间。一般器件供应商会提供MTBF(mean time between failures)和tMET数据供设计参考。 MTBF:两次亚稳态出现的统计平均间隔时间。 MET:亚稳态持续的统计平均时间。 祥见AN042:ALTERA器件的亚稳态问题。 ·设计中尽量避免出现亚稳态问题,采用同步设计是目前最 好的办法。在异步电路与同步电路接口处常用同步器处理, 在异步电路设计中要专门处理

第二讲 数字系统设计的基础知识 西安邮电学院通信工程系 D触发器的亚稳态特性 亚稳态是触发器的固有特性,不可能消除,只能尽量减小 其的持续时间。一般器件供应商会提供MTBF (mean time between failures)和tMET数据供设计参考。 MTBF:两次亚稳态出现的统计平均间隔时间。 tMET:亚稳态持续的统计平均时间。 祥见AN042:ALTERA器件的亚稳态问题。 设计中尽量避免出现亚稳态问题,采用同步设计是目前最 好的办法。在异步电路与同步电路接口处常用同步器处理, 在异步电路设计中要专门处理