行为级仿真 6 窗口里。gvan命令不支持基于周期的仿真。 2.4.1 simdepends 当你的设计源代码或工作环境有所改变时,必须先重新分析这有改变的源文件,同时 也要重新分析包含了这设计单元的其他源文件,对于一个庞大而复杂的设计来说,要找出 这些有关联的源文件是一件非常困难的事。分析器的simdepends应用帮助你解决了这麻 烦。simdepends列出了所有你相互之间有关联的文件列单,并且在重新分析源文件的同时 帮你自动重新分析相关联的源文件。它的输出文件就是UNIX中的makefile文件。 运行simdepends产生依赖文件列单命令:simdepends[options]design_unit 注意:这里的design_unit必须是你的顶层设计单元,可以是configuration, package,entity。 simdepends的使用步骤如下: a)用vhdlan或gvan分析你的设计:gvan designl design2 design3· b) 运行simdepends产生依赖列单:simdepends-o makefile top_design_unit 仿真你的设计: d)修改你的设计: e)使用NIX的make命令重新分析你的源文件和相关的源文件: make ANALYZER=gvan all 2.4.2 simcompiled 如果你是为compiled模式仿真分析源文件,且想知道将来哪个compiled选项在这个 设计单元中使用,则在这个design unit上调用simcompiled,它将为你提供这方面的 compiled仿真消息。命令为: simcompiled [options]design_unit [-u design_unit] 2.5设计的仿真与结果分析 2.5.1仿真机制 VSS提供三种仿真机制: Interpreted: 拥有强大的调试性能,在仿真过程中可以设置monitors和断点。它的调试可以是源代 码级的,例如它可以监测变量和设计模块(b1ock)中的源代码。 Compiled:利用compiled模块最大化你的仿真速度。但是它只支持少数的调试功 能,例如不能设置断点。 优化了的FTGS门级(Gate-Level): 精确的门级仿真,优化了的FTGS门级仿真机制利用ASIC供应商的门级模型,精确的 仿真设计中的物理器件。 在设计的早期,设计者需经常修改设计,建议使用Interpreted机制。当设计稳定下 来以后,为加快仿真速度,建议使用Com即iled机制。当然也可使用混合仿真机制,对未稳 定的设计部分使用Interpreted机制,稳定了的设计部分使用Compiled机制。对于综合后 的门级仿真和ASIC的完成验证当然是使用Gate-Level机制。 何时使用何种仿真机制,VSS根据你的设计文件自动调用。例如目标文件(.o)VSS自 动调用Compiled机制,但是你也可以利用屏蔽调试功能对已编译设计强制使用 Interpreted机制来进行进一步的调试。要使用屏蔽调试功能在启动VSS时加上-fi或者- fi_all选项即可。 2.5.2VSS的启动 启动VSS可以有两中方法,一种是vhd1sim,使用命令行界面:一种是vhdldbx,使用 图形窗口界面。 调用vhdldbx:%vhdldbx[options]design或%vhdldbx&再在Vhdldbx--Select Simulator Arguments窗口中选择仿真单元。 调用vhdlsim:‰vhdlsim[options]design显示命令行提示符# design可以是[libname]cfgname,也可以是[libname].entname,[1 ibname].entname archname。较常用的是[libname]cfgname。 options中有很多的选项和setup文件中定义的变量功能是相同的,options中的变 量优先级高于setup文件中的变量,即options的定义将覆盖setup文件中的变量定义

行为级仿真 6 窗口里。 gvan 命令不支持基于周期的仿真。 2.4.1 simdepends 当你的设计源代码或工作环境有所改变时,必须先重新分析这有改变的源文件,同时 也要重新分析包含了这设计单元的其他源文件,对于一个庞大而复杂的设计来说,要找出 这些有关联的源文件是一件非常困难的事。分析器的 simdepends 应用帮助你解决了这麻 烦。 simdepends 列出了所有你相互之间有关联的文件列单,并且在重新分析源文件的同时 帮你自动重新分析相关联的源文件。它的输出文件就是 UNIX 中的 makefile 文件。 运行 simdepends 产生依赖文件列单命令: simdepends [options] design_unit 注意:这里的 design_unit 必须是你的顶层设计单元,可以是 configuration , package , entity 。 simdepends 的使用步骤如下: a) 用 vhdlan 或 gvan 分析你的设计: gvan design1 design2 design3 …… b) 运行 simdepends 产生依赖列单: simdepends -o makefile top_design_unit c) 仿真你的设计: d) 修改你的设计: e) 使用 UNIX 的 make 命令重新分析你的源文件和相关的源文件: make ANALYZER=gvan all 2.4.2simcompiled 如果你是为 compiled 模式仿真分析源文件,且想知道将来哪个 compiled 选项在这个 设计单元中使用,则在这个 design unit 上调用 simcompiled,它将为你提供这方面的 compiled 仿真消息。命令为: simcompiled [options] design_unit [-u design_unit] 2.5 设计的仿真与结果分析 2.5.1 仿真机制 VSS 提供三种仿真机制: Interpreted: 拥有强大的调试性能,在仿真过程中可以设置 monitors 和断点。它的调试可以是源代 码级的,例如它可以监测变量和设计模块(block)中的源代码。 Compiled: 利用 compiled 模块最大化你的仿真速度。但是它只支持少数的调试功 能,例如不能设置断点。 优化了的 FTGS 门级(Gate-Level): 精确的门级仿真,优化了的 FTGS 门级仿真机制利用 ASIC 供应商的门级模型,精确的 仿真设计中的物理器件。 在设计的早期,设计者需经常修改设计,建议使用 Interpreted 机制。当设计稳定下 来以后,为加快仿真速度,建议使用 Compiled 机制。当然也可使用混合仿真机制,对未稳 定的设计部分使用 Interpreted 机制,稳定了的设计部分使用 Compiled 机制。对于综合后 的门级仿真和 ASIC 的完成验证当然是使用 Gate-Level 机制。 何时使用何种仿真机制, VSS 根据你的设计文件自动调用。例如目标文件(.o)VSS 自 动调用 Compiled 机制,但是你也可以利用屏蔽调试功能对已编译设计强制使用 Interpreted 机制来进行进一步的调试。要使用屏蔽调试功能在启动 VSS 时加上-fi 或者- fi_all 选项即可。 2.5.2VSS 的启动 启动 VSS 可以有两中方法,一种是 vhdlsim ,使用命令行界面;一种是 vhdldbx,使用 图形窗口界面。 调用 vhdldbx: %vhdldbx [options] design 或%vhdldbx &再在 Vhdldbx-Select Simulator Arguments 窗口中选择仿真单元。 调用 vhdlsim: %vhdlsim [options] design 显示命令行提示符 # design 可以是[libname]cfgname,也可以是[libname] entname,[libname] entname archname 。较常用的是[libname] cfgname 。 options 中有很多的选项和 setup 文件中定义的变量功能是相同的, options 中的变 量优先级高于 setup 文件中的变量,即 options 的定义将覆盖 setup 文件中的变量定义

行为级仿真 常用options: -i filename 启动时调用命令文件filename -e filename 启动时调用命令文件,同时显示执行的命令 -sdf filename.sdf读入SDF文件。 2.5.3常用的命令行命令: run [n] 运行n个时间单位 trace [options object name list 绘出name的波形在波形观察器里 1s [name] 列出name匹配的对象 cd region 改变当前工作域 quit 结束仿真 restart 重启 include filename 调用命令文件filename help topic 特定主题和命令的帮助 assign(7 DL expression)(VHDL object name}给对象赋值 evaluate vhdlexpression list 计算并显示表达式的值 statue [-t](process name/dignal_name) 列出准备运行或等待事件发生的进程 调用命令文件的方法有四: include filename vhdlsim -i filename design unit vhdlsim -e filename design unit 年执行时显示命令*/ 或在.Synopsys_.vSs.setup文件中设置:RUNREAD=filename VSS,则每次调用都 执行这个文件。如果调用VSS时使用一i filename,VSS先执行RUNREAD指定的文件,再 执行-i filename指定的文件。 configuration informations:environment sim_config #show_setup >sim_config 暂时逃到操作系统执行数条命令方法: #! First command Second command last command exit 纠错:#help vss--error_number 得到变量的值:$variable 显示变量的值:echo Svariable 设置变量的值:set如:set PROMPT> 产生用户定义的变量:如:set MY_REGION/CPU/alu/addwe/,nand2 产生波形文代.ow),在setup文件中设置:WAVEFORM=wif,同时调用Waveform Viewer 则设置为:WAVEFORM=wif+waves 产生命令过程:#comm name >first command 7. > end 运行的话,只需打入过程的名字就行了。 产生监测(monitors):monitor[options]condition 编辑monitors:#edit monitor_name

行为级仿真 7 常用 options: -i filename 启动时调用命令文件 filename -e filename 启动时调用命令文件,同时显示执行的命令 -sdf filename.sdf 读入 SDF 文件。 2.5.3 常用的命令行命令: run [n] 运行 n 个时间单位 trace [options] object_name_list 绘出 name 的波形在波形观察器里 ls [name] 列出 name 匹配的对象 cd region 改变当前工作域 quit 结束仿真 restart 重启 include filename 调用命令文件 filename help topic 特定主题和命令的帮助 assign (VHDL_expression) {VHDL_object_name} 给对象赋值 evaluate vhdl_expression_list 计算并显示表达式的值 statue [-t] {process_name|dignal_name} 列出准备运行或等待事件发生的进程 调用命令文件的方法有四: # include filename 或% vhdlsim –i filename design_unit 或% vhdlsim –e filename design_unit /*执行时显示命令*/ 或在. Synopsys_vss.setup 文件中设置: RUNREAD = filename VSS ,则每次调用都 执行这个文件。如果调用 VSS 时使用- i filename , VSS 先执行 RUNREAD 指定的文件,再 执行-i filename 指定的文件。 得到 configuration informations: # environment > sim_config # !show_setup >> sim_config 暂时逃到操作系统执行数条命令方法: #! First command Second command . . last command exit # 纠错:# help vss-error_number 得到变量的值:$ variable 显示变量的值: echo $variable 设置变量的值: set 如: set PROMPT ^> ^ 产生用户定义的变量:如: set MY_REGION /CPU/alu/addwe/nand2 产生波形文件(.ow ),在setup文件中设置:WAVEFORM=wif,同时调用Waveform Viewer 则设置为: WAVEFORM=wif+waves 产生命令过程: # comm name >first command > . > . > end # 运行的话,只需打入过程的名字就行了。 产生监测(monitors): monitor [options] condition 编辑 monitors: #edit monitor_name

行为级仿真 8 重导monitor的输出:redirect device tag monitor list coverage-计算和显示在interpreted simulation中执行的VHDL源代码的每一行 的时间数 #coverage [options][vhdl source file list]/*/ coverage [options](filename} /*调用*/ VCD(a Value Change Dump)文件:包含有时间量程,范围定义,堆放了的时间类型和 随着时间的增加实际值的改变等信息的ASCII文件。 产生常规的VCD file: 启动vhdlsim, 执行vcdfiel vcdcomment,.vcdaddobjectsvcddumpobjects和其他SCL偷 令。 产生扩展的VCD fi文件同上。SCL命令不同:vcdaddports等 也可同时产生这两个文件,用vedon,vedoff,vedlimit等 使用WIF文件作为激励文件: vhdlsim -iw input wif filename.ow design name 产生SAIF(a Switching Activity Interchange Format),文件: vhdlsim -saiffile alarm clock saif cfg tb top_behavioral 2.6设计实例 对于I2C,DDFS,couter等涉及来说,操作的方法相同,由于篇幅的限制,本文只 介绍DDFS设计。 实例:DDFS设计源文件: ddfs.vhd,froma.vhd,fromb.vhd,croma.vhd,cromb.vhd(注意这里的VHDL源文件不要 忘了加configuration。) testbench文件为DDFS_TB(源文件见附录) 1. 仿真前准备 转到工作目录,设工作目录为/home/usr/design cd /home/usr/design mkdir vhdl 把设计源文件存放在vhdl/目录下 2. 创建setup文件 在工作目录下创建setup文件,setup文件的内容如下: WORK DEFAULT DEFAULT work TIMEBASE ps 3.创建设计库 mkdir work 4.设计分析 产生设计分析的命令文件analyzel.sh,内容为: #!/bin/sh -f vhdlan -event vhdl/ddfs.vhd vhdl/froma.vhd vhdl/fromb.vhd vhdl/croma.vhd vhdl/cromb.vhd vhdl/DDFS_TB.vhd 注:更好的命令文件是把创建设计库也写在里面,其内容见附录。 执行命令文件,对源文件进行分析: analyzel.sh 5.设计调用仿真器进行设计仿真 产生仿真命令文件simfile,其最基本的内容为:

行为级仿真 8 重导 monitor 的输出: redirect device_tag monitor_list coverage -- 计算和显示在 interpreted simulation 中执行的 VHDL 源代码的每一行 的时间数 #coverage [options] [vhdl_source_file_list] /*产生*/ % coverage [options] {filename} /*调用*/ VCD(a Value Change Dump) 文件:包含有时间量程,范围定义,堆放了的时间类型和 随着时间的增加实际值的改变等信息的 ASCII 文件。 产生常规的 VCD file: 启动 vhdlsim , 执行 vcdfiel vcdcomment,vcdaddobjectsvcddumpobjects 和其他 SCL 命 令。 产生扩展的 VCD fi 文件同上。 SCL 命令不同: vcdaddports 等 也可同时产生这两个文件,用 vcdon ,vcdoff,vcdlimit 等 使用 WIF 文件作为激励文件: % vhdlsim –iw input_wif_filename.ow design_name 产生 SAIF(a Switching Activity Interchange Format) 文件 : % vhdlsim –saiffile alarm_clock_saif cfg_tb_top_behavioral 2.6 设计实例 对于 I2C , DDFS , couter 等涉及来说,操作的方法相同,由于篇幅的限制,本文只 介绍 DDFS 设计。 实例: DDFS 设计源文件: ddfs.vhd,froma.vhd,fromb.vhd,croma.vhd,cromb.vhd(注意这里的 VHDL 源文件不要 忘了加 configuration 。) testbench 文件为 DDFS_TB (源文件见附录) 1. 仿真前准备 转到工作目录,设工作目录为/home/usr/design % cd /home/usr/design % mkdir vhdl 把设计源文件存放在 vhdl/目录下 2. 创建 setup 文件 在工作目录下创建 setup 文件, setup 文件的内容如下: WORK > DEFAULT DEFAULT : work TIMEBASE = ps 3. 创建设计库 % mkdir work 4. 设计分析 产生设计分析的命令文件 analyze1.sh,内容为: #!/bin/sh -f vhdlan -event \ vhdl/ddfs.vhd \ vhdl/froma.vhd \ vhdl/fromb.vhd \ vhdl/croma.vhd \ vhdl/cromb.vhd \ vhdl/DDFS_TB.vhd 注;更好的命令文件是把创建设计库也写在里面,其内容见附录。 执行命令文件,对源文件进行分析: % analyze1.sh 5. 设计调用仿真器进行设计仿真 产生仿真命令文件 simfile ,其最基本的内容为:

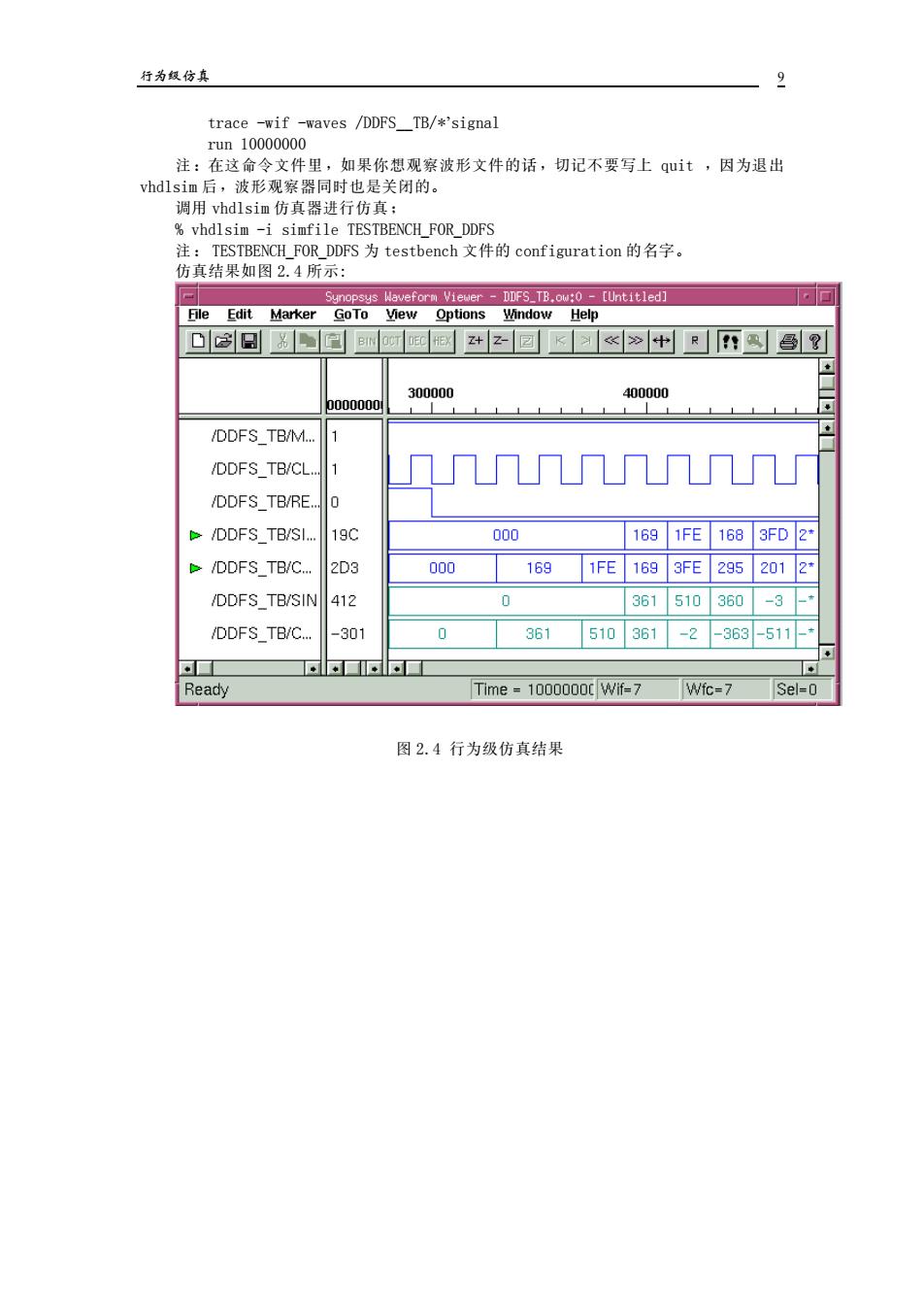

行为级仿真 9 trace -wif -waves /DDFS_TB/*'signal run10000000 注:在这命令文件里,如果你想观察波形文件的话,切记不要写上quit,因为退出 vhdlsim后,波形观察器同时也是关闭的。 调用vhdlsim仿真器进行仿真; vhdlsim -i simfile TESTBENCH FOR DDFS 注:TESTBENCH_FOR_DDFS为testbench文件的configuration的名字。 仿真结果如图2.4所示: Synopsys Waveform Viewer DDFS_TB.ow:0 [Untitled] File Edit Marker GoTo View Options Window Help D日多间W画+z回K习之中:恩昼? 300000 400000 0000000 /DDFS_TB/M... /DDFS TB/CL.. /DDFS TB/RE.. 0 /DDFS TB/SI... 19C 000 169 1FE 168 3FD 2* /DDFS_TB/C.. 2D3 000 169 1FE 169 3FE 295 201 2 /DDFS_TB/SIN 412 0 361 510 360 /DDFS_TB/C.. -301 0 361 510 361 -2 -363 -511- ■ 布■■ Ready Time=1000000C Wif=7 Wfc=7 Sel=0 图2.4行为级仿真结果

行为级仿真 9 trace -wif -waves /DDFS__TB/*’signal run 10000000 注:在这命令文件里,如果你想观察波形文件的话,切记不要写上 quit ,因为退出 vhdlsim 后,波形观察器同时也是关闭的。 调用 vhdlsim 仿真器进行仿真; % vhdlsim -i simfile TESTBENCH_FOR_DDFS 注: TESTBENCH_FOR_DDFS 为 testbench 文件的 configuration 的名字。 仿真结果如图 2.4 所示: 图 2.4 行为级仿真结果

Behavioral Compiler Module Compiler 第三章 Behavioral Compiler Module Compiler 3.1 Behavioral Compiler Behavioral Compiler自动把行为级的HDL设计综合成了RTL级设计,提高了设计者 的设计效率。 3.1.1 Behavioral Compiler的设计流程图(如图3.1所示) Behavioral code Analyze Elaborate elaborated.db (optional) Check syntax (bc_check_design) Initial constraints (Detail of Timing timing process) Estimate timing and area (bc_time_design) timed.db Read timed.db (Detail of scheduling process) ¥ Add constraints Scheduling schedule command Review results (bc view,report schedule) RTL HDL RTL.db No Code Yes Constraints change? Simulate met? Compile Synthesis RTL Yes No Constraint Yes Gate-level netlist To other change? RTL tools 图3.1 Behavioral Compiler的设计流程 3.1.2 Behavioral Compiler设计流程及相关偷令 1.分析设计: analyze [-library library_name][-work library_name][-format vhdl verilog] [-create_update][-update][-define define_netlist]file_list 如:analyze-format vhdl name_design.vhd 2.Elaborating设计: elaborate design_name [-library library_name -work library_name][ architecture arch_name][-parameters parameter_list][-file_parameters

Behavioral Compiler 和 Module Compiler 1 第三章 BehavioralCompiler 和 ModuleCompiler 3.1 BehavioralCompiler Behavioral Compiler 自动把行为级的 HDL 设计综合成了 RTL 级设计,提高了设计者 的设计效率。 3.1.1 BehavioralCompiler 的设计流程图(如图 3.1 所示) 图 3.1 Behavioral Compiler 的设计流程 3.1.2BehavioralCompiler 设计流程及相关命令 1. 分析设计: analyze [-library library_name] [-work library_name] [-format vhdl | verilog] [-create_update] [-update] [-define define_netlist] file_list 如: analyze -format vhdl name_design.vhd 2. Elaborating 设计: elaborate design_name [-library library_name | -work library_name] [- architecture arch_name] [-parameters parameter_list] [-file_parameters