采样数据输出形式 >采样数据输出 高速串行CML 差分信号摆幅为800mV,共模电压为VCC-0.2V、 特征阻抗100Q,结构简单。 通常适用于极高数据带宽传输的器件中。 如:AD9625,2.5GSPS、12位 数据线:6.25Gbps,8对差分(16根线) JESD204B 参考时钟线:1对差分(2根线),可不用

第11页 采样数据输出 采样数据输出形式 高速串行——CML 差分信号摆幅为800mV,共模电压为VCC-0.2V 、 特征阻抗100Ω,结构简单。 通常适用于极高数据带宽传输的器件中。 如:AD9625,2.5GSPS、12位 数据线:6.25Gbps,8对差分(16根线) 参考时钟线:1对差分(2根线),可不用 JESD204B

采样数据输出形式 >采样数据输出 高速串行一CML JESD204B AD9625时序图 需具有高速电路设计要求!且 需专用的串化器和解串器 N-226 SAMPLE N ANALOG INPUT KN-225 N+1 SIGNAL N-224 CLK- CLK+ 采样钟 CLK- CLK+ SERDOUTO+ SERDOUT7 数据线 SAMPLE N-226 SAMPLE N-225 SAMPLE N-224 ENCODED INTO 2 ENCODED INTO2 ENCODED INTO 2 8-8T710-8 IT SYMB01 8-BIT/10-BIT SYMBOL 8-BIT/10-BIT SYMBOL

第12页 采样数据输出 采样数据输出形式 高速串行——CML 需具有高速电路设计要求!且 需专用的串化器和解串器 数据线 采样钟 AD9625时序图 JESD204B

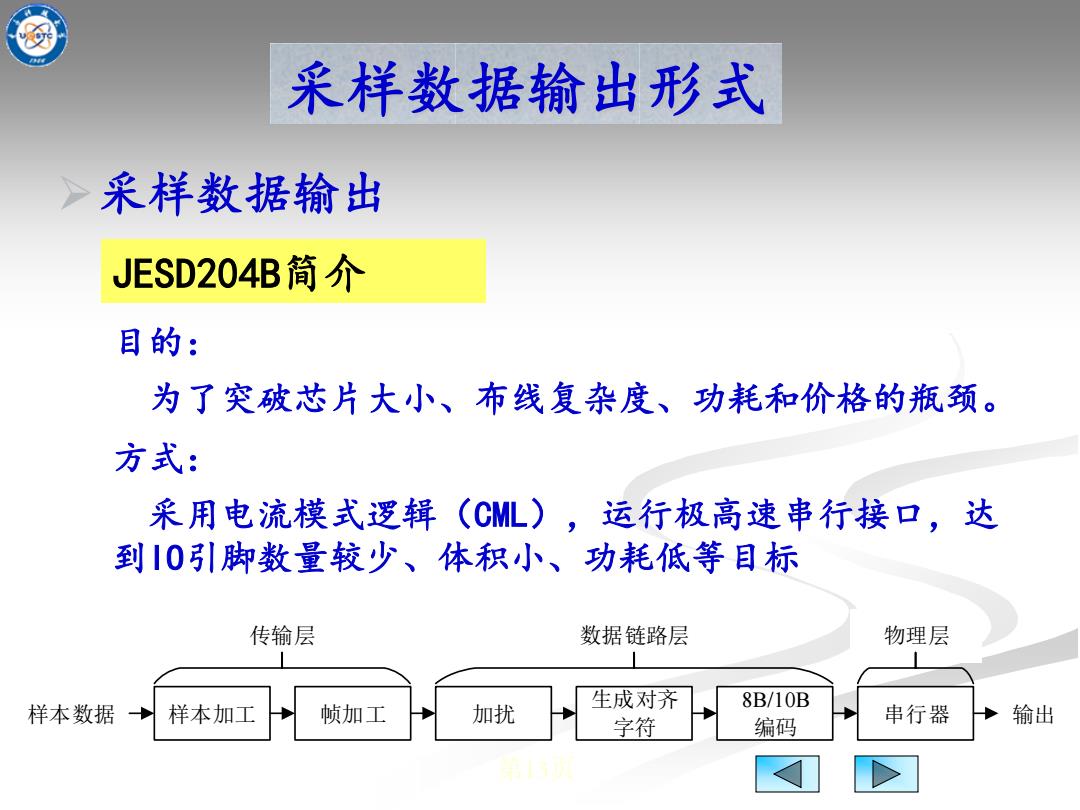

采样数据输出形式 >采样数据输出 JESD204B简介 目的: 为了突破芯片大小、布线复杂度、功耗和价格的瓶颈。 方式: 采用电流模式逻辑(CML),运行极高速串行接口,达 到0引脚数量较少、体积小、功耗低等目标 传输层 数据链路层 物理层 样本数据 生成对齐 8B/10B 样本加工 帧加工 加扰 字符 编码 串行器 →输出

第13页 采样数据输出 采样数据输出形式 JESD204B简介 目的: 为了突破芯片大小、布线复杂度、功耗和价格的瓶颈。 方式: 采用电流模式逻辑(CML),运行极高速串行接口,达 到IO引脚数量较少、体积小、功耗低等目标 传输层 数据链路层 物理层 样本加工 帧加工 加扰 生成对齐 字符 8B/1 0B 编码 样本数据 串行器 输出

采样数据输出形式 >采样数据输出 JESD204B简介 传输层负责将数据(由样本数据和可选的控制位组成) 加工成8位字并发送至数据链路层。工作模式受到链路配 置数据生成的规则制约,来加工数据,需要时可添加结 束位来填补空隙。 数据链路层负责执行通过链路传送数据的功能,执行加 扰、同步对齐、编码操作。抑制频谱尖峰所产生的电容兼容问题。 传输层 频谱平衡 数据链路层 物理层 生成对齐 8B/10B 样本数据 样本加工 帧加工 加扰 字符 编码 串行器 ·输出 数据成颅 多通道同步 直流平衡

第14页 采样数据输出 采样数据输出形式 JESD204B简介 传输层负责将数据(由样本数据和可选的控制位组成) 加工成8位字并发送至数据链路层。工作模式受到链路配 置数据生成的规则制约,来加工数据,需要时可添加结 束位来填补空隙。 传输层 数据链路层 物理层 样本加工 帧加工 加扰 生成对齐 字符 8B/1 0B 编码 样本数据 串行器 输出 数据链路层负责执行通过链路传送数据的功能,执行加 扰、同步对齐、编码操作。 频谱平衡 数据成帧 多通道同步 直流平衡 抑制频谱尖峰所产生的电容兼容问题

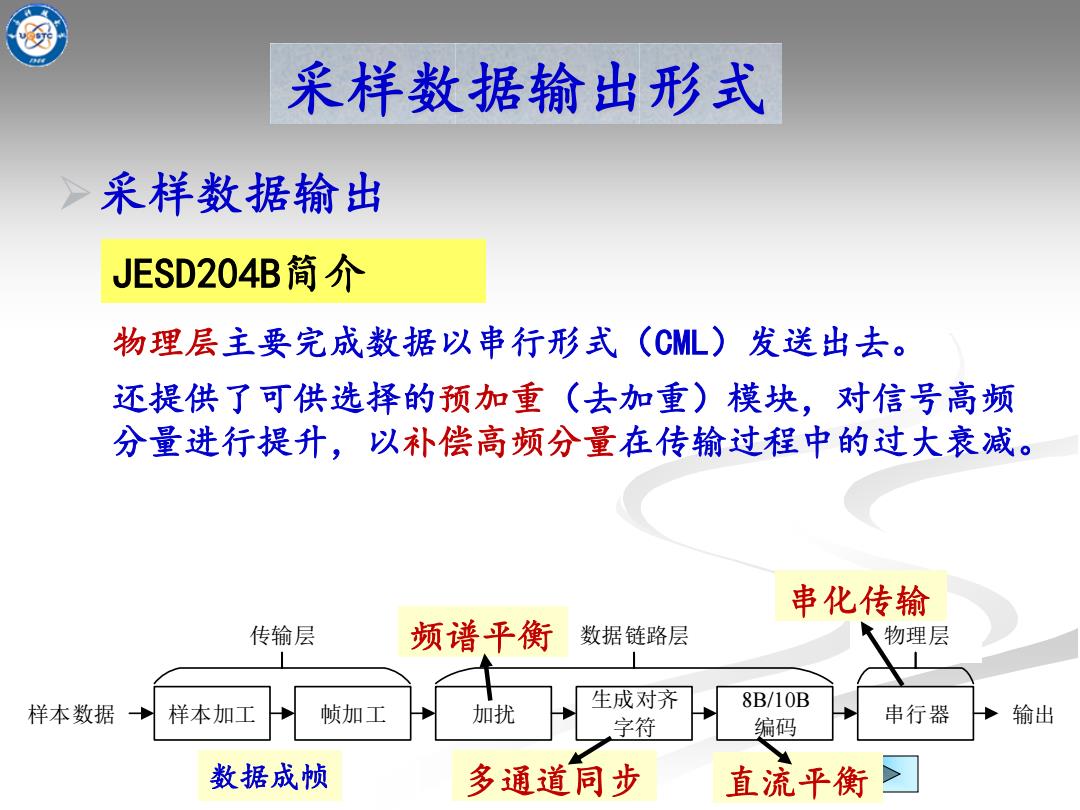

采样数据输出形式 >采样数据输出 JESD204B简介 物理层主要完成数据以串行形式(CML)发送出去。 还提供了可供选择的预加重(去加重)模块,对信号高频 分量进行提升,以补偿高频分量在传输过程中的过大衰减。 串化传输 传输层 频谱平衡 数据链路层 物理层 生成对齐 8B/10B 样本数据 样本加工 帧加工 加扰 字符 编码 串行器 ·输出 数据成颅 多通道同步 直流平衡

第15页 采样数据输出 采样数据输出形式 JESD204B简介 物理层主要完成数据以串行形式(CML)发送出去。 还提供了可供选择的预加重(去加重)模块,对信号高频 分量进行提升,以补偿高频分量在传输过程中的过大衰减。 传输层 数据链路层 物理层 样本加工 帧加工 加扰 生成对齐 字符 8B/1 0B 编码 样本数据 串行器 输出 频谱平衡 数据成帧 多通道同步 直流平衡 串化传输