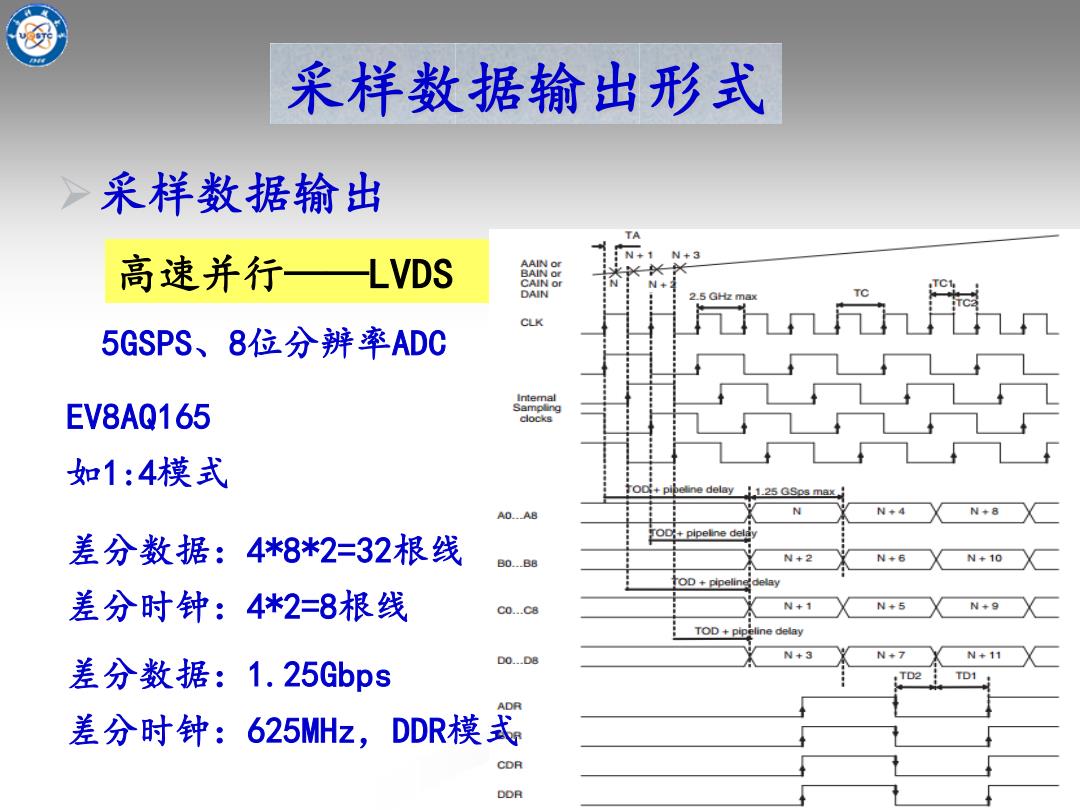

采样数据输出形式 >采样数据输出 TA N+1N+3 高速并行LVDS CAIN or TC DAIN 2.5 GHz max TC CLK 5GSPS、8位分辨率ADC Intemal EV8AQ165 如1:4模式 o+pibeline delay 1.25 GSps max AD..AB N+4 N+8 TOD+pipeline delay 差分数据:4*8*2=32根线 B0...B8 N+2 N+6 N+10 OD pipelinedelay 差分时钟:4*2=8根线 C0..c8 N+1 N+5 N+9 TOD+pipeline delay D0..D8 N+3 N+7 N+11 差分数据:1.25Gbps TD2 TD1 差分时钟:625MHz,DDR模式 CDR DOR

第6页 采样数据输出 采样数据输出形式 高速并行——LVDS 5GSPS、8位分辨率ADC EV8AQ165 如1:4模式 差分数据:4*8*2=32根线 差分时钟:4*2=8根线 差分数据:1.25Gbps 差分时钟:625MHz,DDR模式

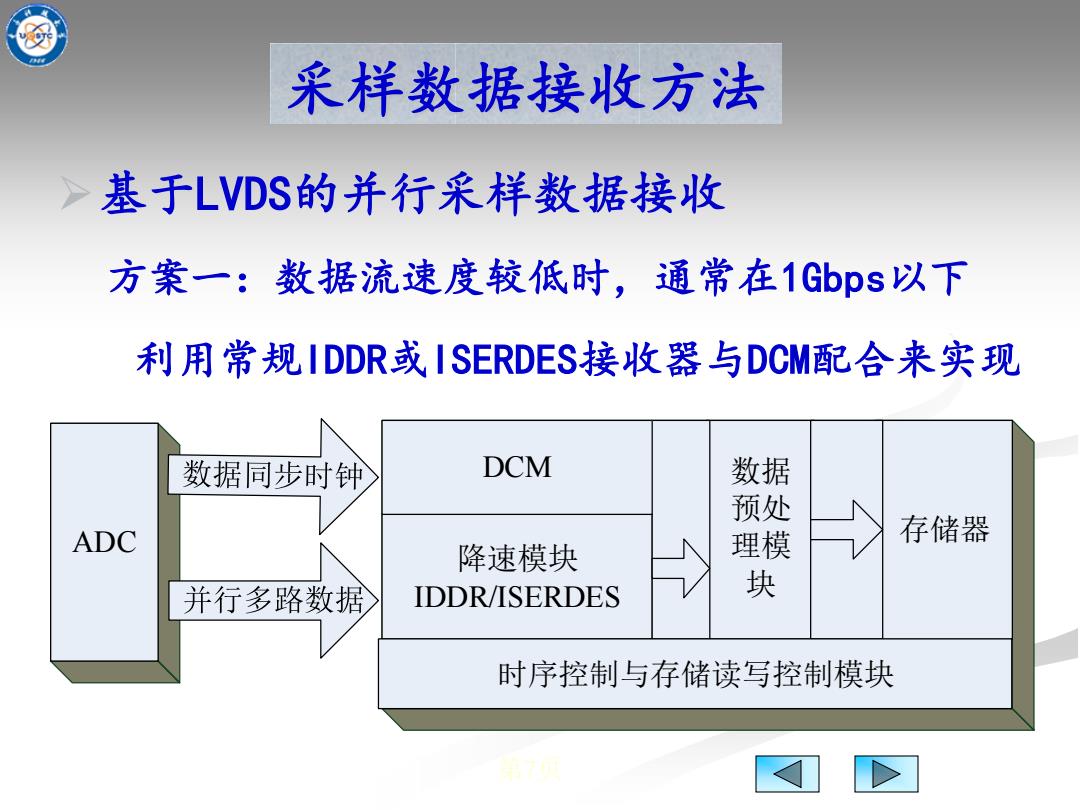

采样数据接收方法 >基于LVDS的并行采样数据接收 方案一:数据流速度较低时,通常在1Gbps以下 利用常规IDDR或I SERDES.接收器与DCM配合来实现 数据同步时钟 DCM 数据 预处 ADC 理模 存储器 降速模块 并行多路数据 IDDR/ISERDES 块 时序控制与存储读写控制模块

第7页 基于LVDS的并行采样数据接收 采样数据接收方法 方案一:数据流速度较低时,通常在1Gbps以下 降速模块 IDDR/ISERDES 数据 预处 理模 块 存储器 时序控制与存储读写控制模块 ADC DCM 利用常规IDDR或ISERDES接收器与DCM配合来实现

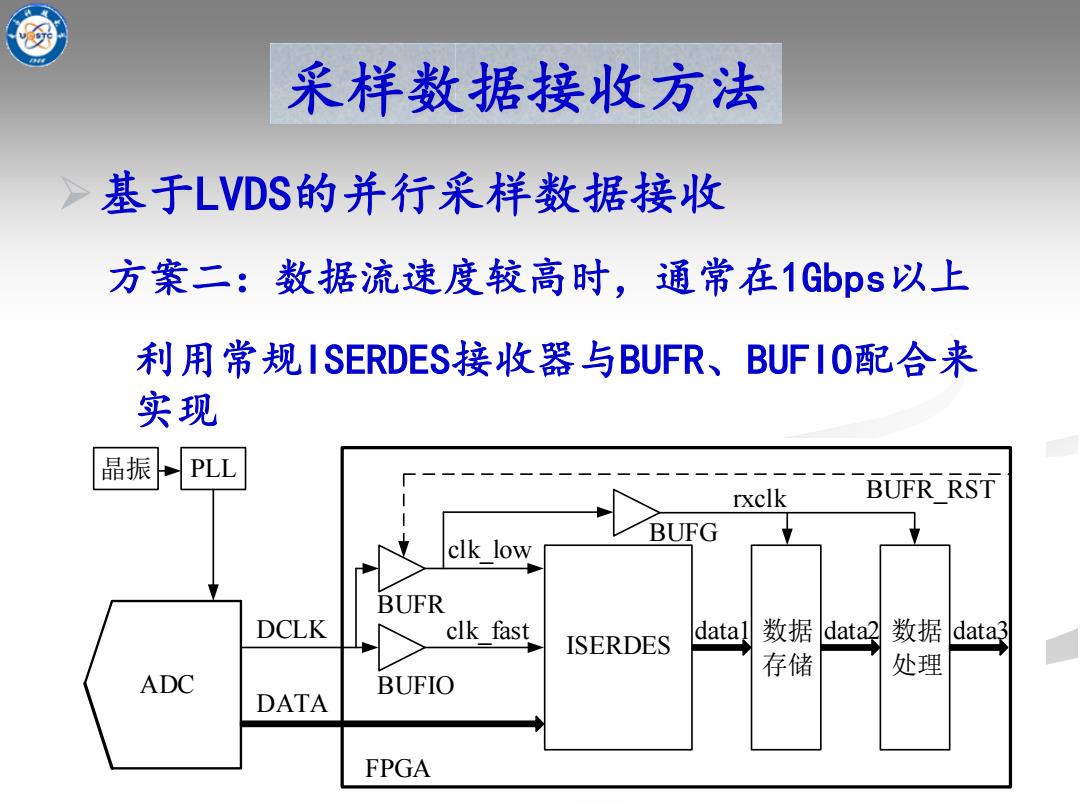

采样数据接收方法 >基于LVDS的并行采样数据接收 方案二:数据流速度较高时,通常在1Gbps以上 利用常规I SERDES接收器与BUFR、BUFI0配合来 实现 晶振 PLL rxclk BUFR RST BUFG clk low BUFR DCLK clk fast ISERDES datal 数据data2 数据data3 存储 处理 ADC BUFIO DATA FPGA

第8页 基于LVDS的并行采样数据接收 采样数据接收方法 方案二:数据流速度较高时,通常在1Gbps以上 利用常规ISERDES接收器与BUFR、BUFIO配合来 实现 ADC DCLK DATA BUFR FPGA BUFIO clk_fast clk_low ISERDES BUFR_RST data1 数据 存储 data2 数据 处理 BUFG rxclk 晶振 PLL data3

采样数据接收方法 >基于LVDS的并行采样数据接收 难点? 建立时间和保持时间难以满足 解决方案? 源同步设计,利用FPGA内部的I ODELAY,调整 输入数据的延迟,直到满足建立时间和保持 时间要求

第9页 基于LVDS的并行采样数据接收 采样数据接收方法 难点? 建立时间和保持时间难以满足 解决方案? 源同步设计,利用FPGA内部的IODELAY,调整 输入数据的延迟,直到满足建立时间和保持 时间要求

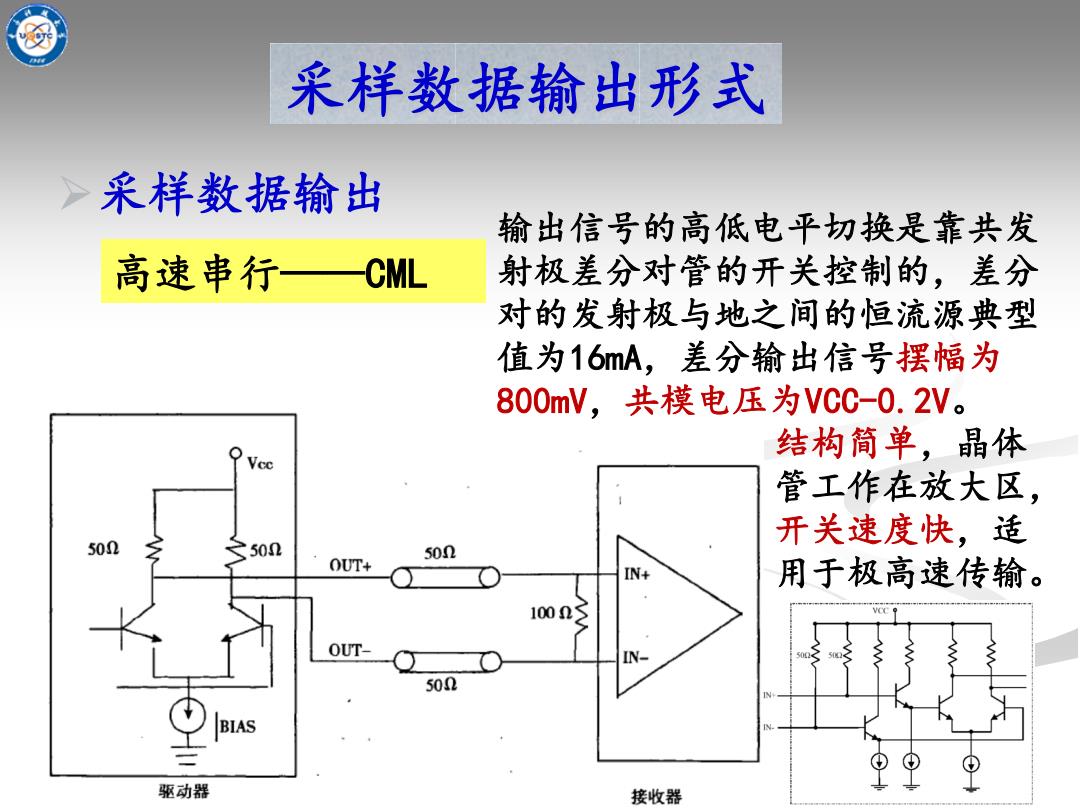

采样数据输出形式 >采样数据输出 输出信号的高低电平切换是靠共发 高速串行 CML 射极差分对管的开关控制的,差分 对的发射极与地之间的恒流源典型 值为16mA,差分输出信号摆幅为 800mV,共模电压为VCC-0.2V。 Q 结构简单,晶体 Vec 管工作在放大区, 开关速度快,适 502 350n 50n OUT+ IN+ 用于极高速传输。 1000 OUT- 50n BIAS 9 驱动器 接收器

第10页 采样数据输出 采样数据输出形式 高速串行——CML 输出信号的高低电平切换是靠共发 射极差分对管的开关控制的,差分 对的发射极与地之间的恒流源典型 值为16mA,差分输出信号摆幅为 800mV,共模电压为VCC-0.2V。 结构简单,晶体 管工作在放大区, 开关速度快,适 用于极高速传输