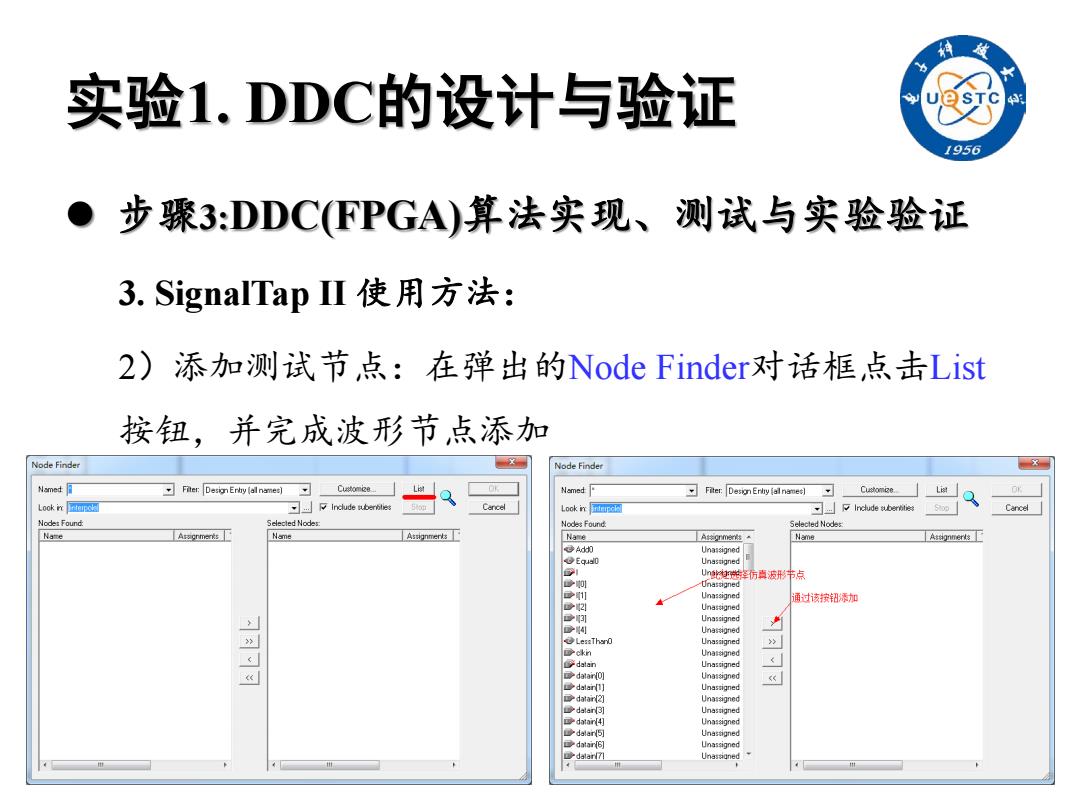

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 2)添加测试节,点:在弹出的Node Finder对话框,点击List 按钮,并完成波形节点添加 Node Finder Node Finder Named Fiter:Desin Erly (al names) Customize L Named Fiter:Desion Erlry (al namee] L Look ix s 习Include 55 Look in图 。7 Include beities 30 Cancel Node:Found: Selected Nodes Nodes Found Selected Nodes A2 orments工 Name Assignmerts Name A9nmet” Name Assignmer格冒 Unaisigned Equso Unastigned 1 Un生洗经伤真波形节点 口1 Unassigned 诵过该按钮添加 Unassigned Unassigned 心同 Unassigned Le: Unassigned ckn Unatsigned datain(0] dalar(1] Unassigned ydat。n3 Unastigned datar(4] Unassgned dtar6 Unassigned dalar☑

7 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 2)添加测试节点:在弹出的Node Finder对话框点击List 按钮,并完成波形节点添加 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 3)初始化输入信号: 图 Master Time Bar 16725s Pointer: 100ps Intervat 1663s Start: kA 10.0ns 20.0n 30.0 Yane 光® 16 16.725n5 回 A [J 少6 clkin 纳令 7 datain O][O] 炬点 司22 ▣dataout 00 37 i_clkic A 三烟 对于输入信号可以设置初始值 汇烟 炬器 及置常量 c 用于设置时钟信号 炬海 跟! 8

8 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 3)初始化输入信号: 实验1. DDC的设计与验证