ASIC设计方法 按版图结构及制造方法分,有半定制(Semi-custom)和 全定制(Ful1-custom)两种实现方法。 全定制方法是一种基于晶 ASIC设计方法 体管级的,手工设计版图的制 造方法。 全定制法 半定制法 半定制法是一种约 束性设计方式,在其内 部集成了大量的门和触 发器,用户通过编程来 门阵列法 标准单元法 改变PLD内部的逻辑关 系和连线,得到需要的 可编程逻辑器件法 电路 南州克通大

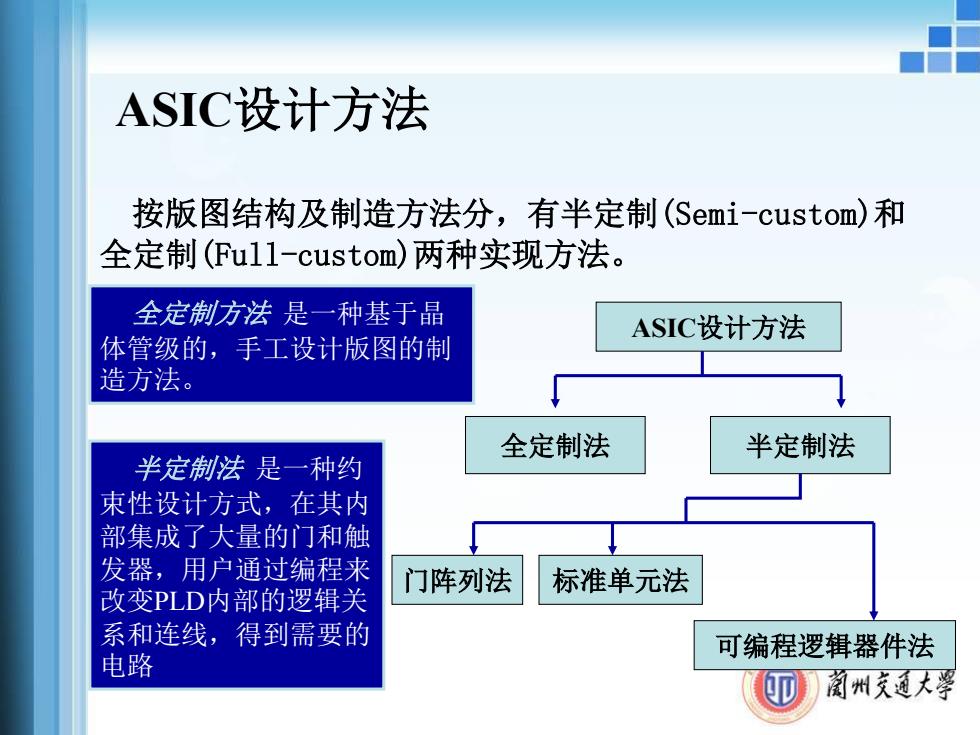

ASIC设计方法 按版图结构及制造方法分,有半定制(Semi-custom)和 全定制(Full-custom)两种实现方法。 全定制方法 是一种基于晶 体管级的,手工设计版图的制 造方法。 半定制法 是一种约 束性设计方式,在其内 部集成了大量的门和触 发器,用户通过编程来 改变PLD内部的逻辑关 系和连线,得到需要的 电路 ASIC设计方法 全定制法 半定制法 门阵列法 标准单元法 可编程逻辑器件法

EDA技术实现目标: 作为EDA技术最终实现目标的ASIC,通过三种途径来完成: EDA技术 ASIC设计 SOPC/SOC 门阵列 (MPGA); FPGA/CPLD 混合 标准单元 可编程ASIC ASIC (CBIC); 设计 设计 全定制; (FCIC); ASIC设计

EDA技术 ASIC设计 FPGA/CPLD 可编程ASIC 设计 门阵列 (MPGA); 标准单元 (CBIC); 全定制; (FCIC); ASIC设计 SOPC/SOC 混合 ASIC 设计 EDA技术实现目标: 作为EDA技术最终实现目标的ASIC,通过三种途径来完成:

SOPC NIOS UART PCI ARM Ethernet USB Interface RAM/ROM Multiply Unit FIFO PLLs JPEG CPL SDRAM CONTROL FIR,IIR,FFT VGA PS2 DSP Blocks SOC: SYSTEM ON A CHIP SOPC: SYSTEM ON A PROGAMMABLE CHIP 南州克通大

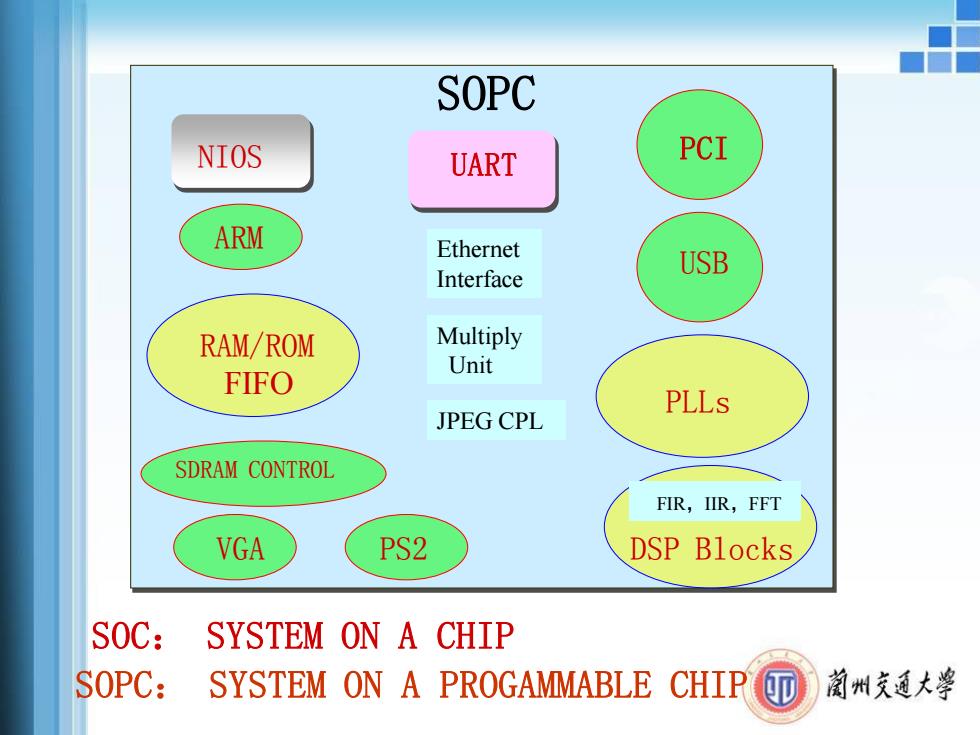

SOC: SYSTEM ON A CHIP SOPC: SYSTEM ON A PROGAMMABLE CHIP SOPC NIOS Ethernet Interface ARM UART RAM/ROM FIFO USB PCI DSP Blocks PLLs SDRAM CONTROL VGA PS2 Multiply Unit JPEG CPL FIR,IIR,FFT

ASIC设计流程 系统规 系统划分 逻辑设计 范说明 与综合 7 版图验证 版图设计 综合后仿 真 参数提取与 制版、流 芯片测试 后仿真 片 ⑩ 菌州克通大等

ASIC设计流程 系统规 范说明 逻辑设计 与综合 系统划分 版图验证 综合后仿 真 版图设计 参数提取与 后仿真 制版、流 芯片测试 片

2.7简单PLD原理 2.7.1常用逻辑门符号与现有国标符号的对照 非门 与门 或门 异或门 常用符号 A- D- 国标符号 & 逻辑表达式 不NOTA 下=AB F=A+B F=A⊕B 葡州克通大

2.7 简单PLD原理 2.7.1常用逻辑门符号与现有国标符号的对照