第六章半导体存储器 6.3.1RAM的结构与工作原理 地 地址码输入1SF : 址译码器 存储矩阵 R/) 读/写 控制器

第六章 半导体存储器 6.3.1 RAM 的结构与工作原理 … 存储矩阵 读/写 控制器 地 址 译 码 器 … 地 址 码 输 入 片选 读/写控制 输入/输出 CS R / W I / O

第六章半导体存储器 [例]对256×4存储矩阵进行地址译码 元地址译码 二元地址译码 0 1 译码器 010 0 行译码器 out W256 0111 X15 8线一 256线 1 0 0 4线一-16线 列译码器 缺点: 10.. 0 n位地址输入的 8位地址输入的 译码器,需要2n条 地址译码器,只有32 输出线。 条输出线

第六章 半导体存储器 [例] 对 256 4 存储矩阵进行地址译码 一元地址译码 … … … D3D2D1D0 W0 W1 W256 译 码 器 0 0 1 1 1 0 1 0 0 1 1 1 A0 A1 A7 1 0 . . . 0 W1 1 0 1 0 8线 — 256线 缺点: n 位地址输入的 译码器,需要 2 n 条 输出线。 1 0 1 0 二元地址译码 Y0Y1 Y15 … A0 A1 A2 A3 X0 X1 X15 行 译 码 器 A4 A5 A6 A7 … 列译码器 Dout 4线 —16线 1 0 . . . 0 1 0 … 0 8 位地址输入的 地址译码器,只有 32 条输出线

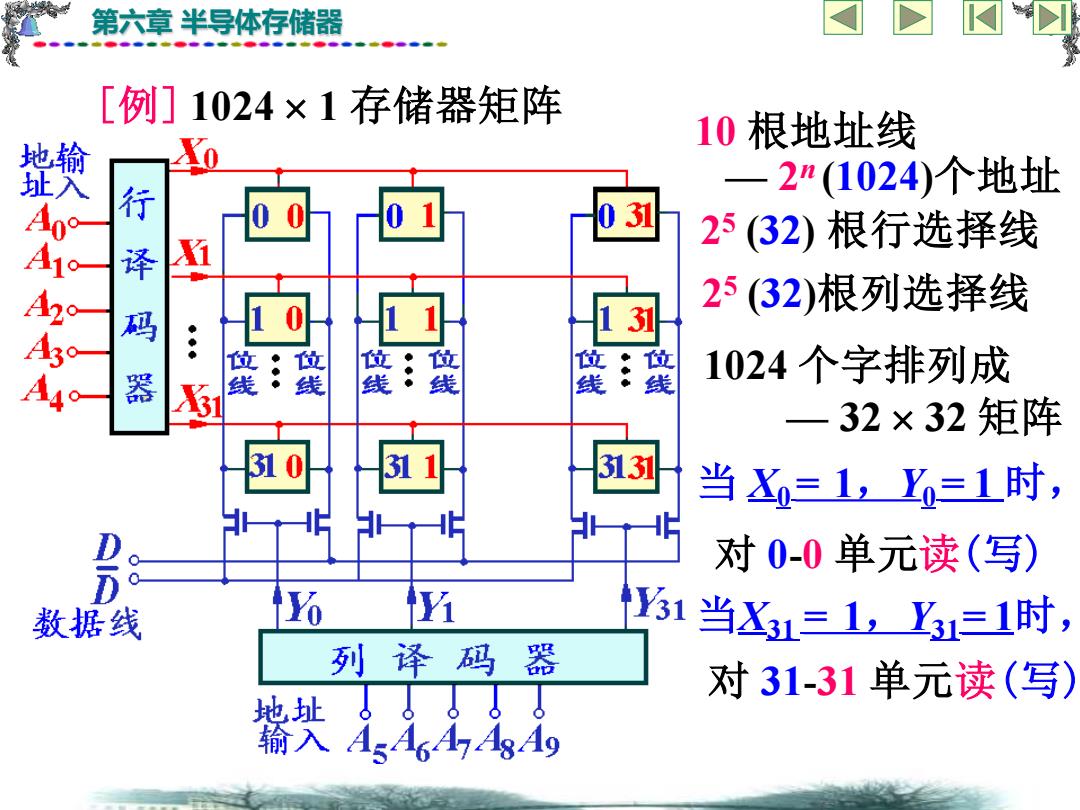

第六章半导体存储器 [例]1024×1存储器矩阵 10根地址线 紫 一 2"(1024)个地址 0 行译码器 0 25(32)根行选择线 10 25(32)根列选择线 131 位位 位: 1024个字排列成 1 线· 线 一32×32矩阵 3131 当X=1,Y=1时, 对0-0单元读(写) D 数据 i 1 当X1=1,Y1=1时, 列译码器 对31-31单元读(写) 地址。。。。。 输入AsA64gA9

第六章 半导体存储器 2 5 (32) 根行选择线 10 根地址线 — 2 n (1024)个地址 2 5 (32)根列选择线 1024 个字排列成 — 32 32 矩阵 当 X0= 1,Y0= 1 时, 对 0-0 单元读(写) 当X31 = 1,Y31= 1时, 对 31-31 单元读(写) [例] 1024 1 存储器矩阵

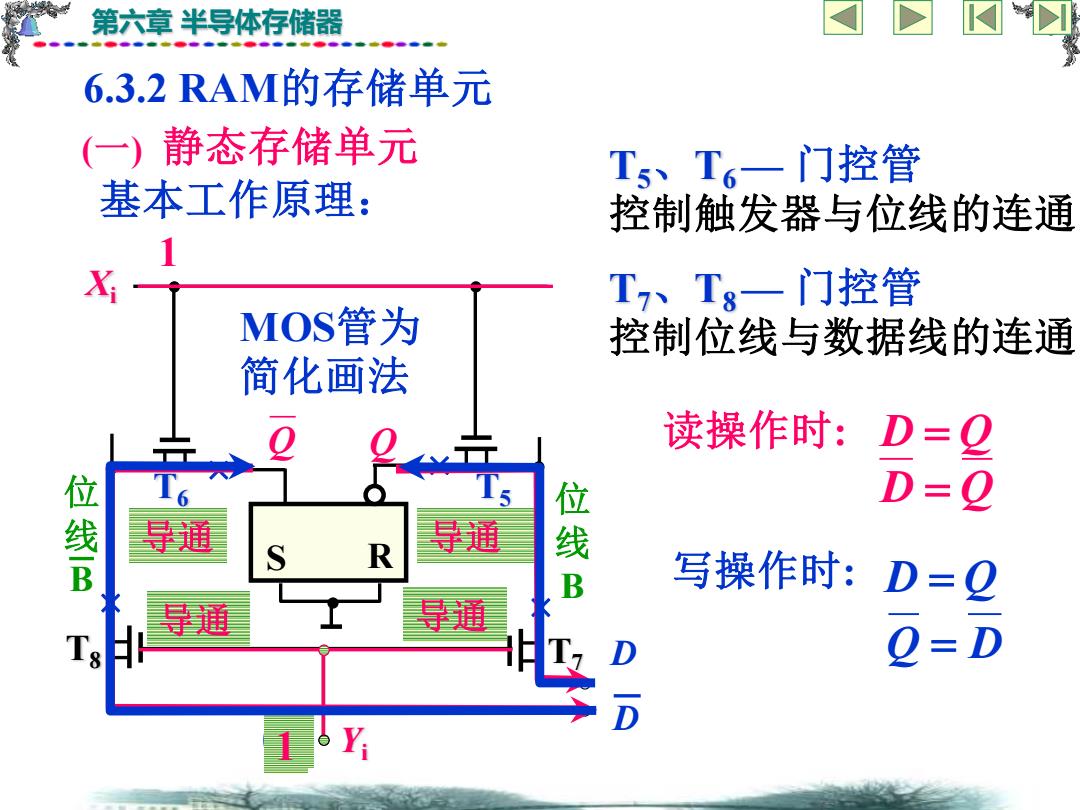

第六章半导体存储器 6.3.2RAM的存储单元 (一)静态存储单元 T5、T6一门控管 基本工作原理: 控制触发器与位线的连通 1 X T、T8一门控管 MOS管为 控制位线与数据线的连通 简化画法 读操作时: D= 位 D= 位线B Q 导通 导通 线 B 写操作时:D=2 导通 导通 O=D 16

第六章 半导体存储器 6.3.2 RAM的存储单元 (一) 静态存储单元 基本工作原理: T6 T5 T8 T7 D D Xi Yi S R Q Q 位 线 B 位 线 B T5、T6— 门控管 控制触发器与位线的连通 截止 截止 导通 导通 0 截止 截止 10 导通 导通 读操作时: D = Q D = Q 写操作时: D = Q Q = D T7、T8— 门控管 控制位线与数据线的连通 010 MOS管为 简化画法