滋的甲盗▣景型赵本收兴名继名 第三章SYNOPSYS中的测试部分及扫描结构 第三章SYNOPSYS中的测试部分及扫描结构 3.1 SYNOPSYS中扫描电路的基本结构 DFT COMPILER支持以下四种扫描结构: 。多路选择型(MULTIPLEXED FLIP FLOP); ·时钟型(CLOCKED SCAN): ·电平敏感型(LSSD): ·辅助时钟电平敏感型(AUXILIARY CLOCK LSSD)。 后三种结构都是在第一种结构的基础上进行的改进,目的是减少由于扫描电 路的误触发导致的竞争和冒险的问题。比如第三种LSSD结构便是在触发时,使 用时钟电平而不是常用的时钟边沿,从而有效的避免了上述问题。但这种改进也 会大大的增加电路的复杂度,所以最常用的还是第一种多路选择型的扫描结构。 SCAN ENABLE SCAN IN SCAN OUT CLK 组合电路部分 图3.1典型的扫描方式电路 所谓多路选择结构,是使用一个多路信号输入来实现串行移位功能。在正常 工作模式下,扫描使能端(也就是输入信号多路选择器的控制端)选择系统输入信 号。当扫描工作模式时,扫描使能端选择扫描输入信号。扫描输入信号来自扫描 输入端口,或者上一个扫描器件的扫描输出端口。图3.1是典型扫描方式电路的 大致框图。图中电路组合部分被单列开来,而由D触发器组成的时序电路部分 成为了扫描链。由图中可以看出,当控制输入SCAN ENABLE=0时,电路动作 按通常方式进行,执行电路的功能。当控制信号SCAN ENABLE=1时,各触发 器形成一个移位寄存器,为扫描方式。在扫描方式下,各触发器可设定任意值, 也可方便的从扫描输出端(scan output)观察其输出值。 对于多路选择结构,需要增加以下端口:

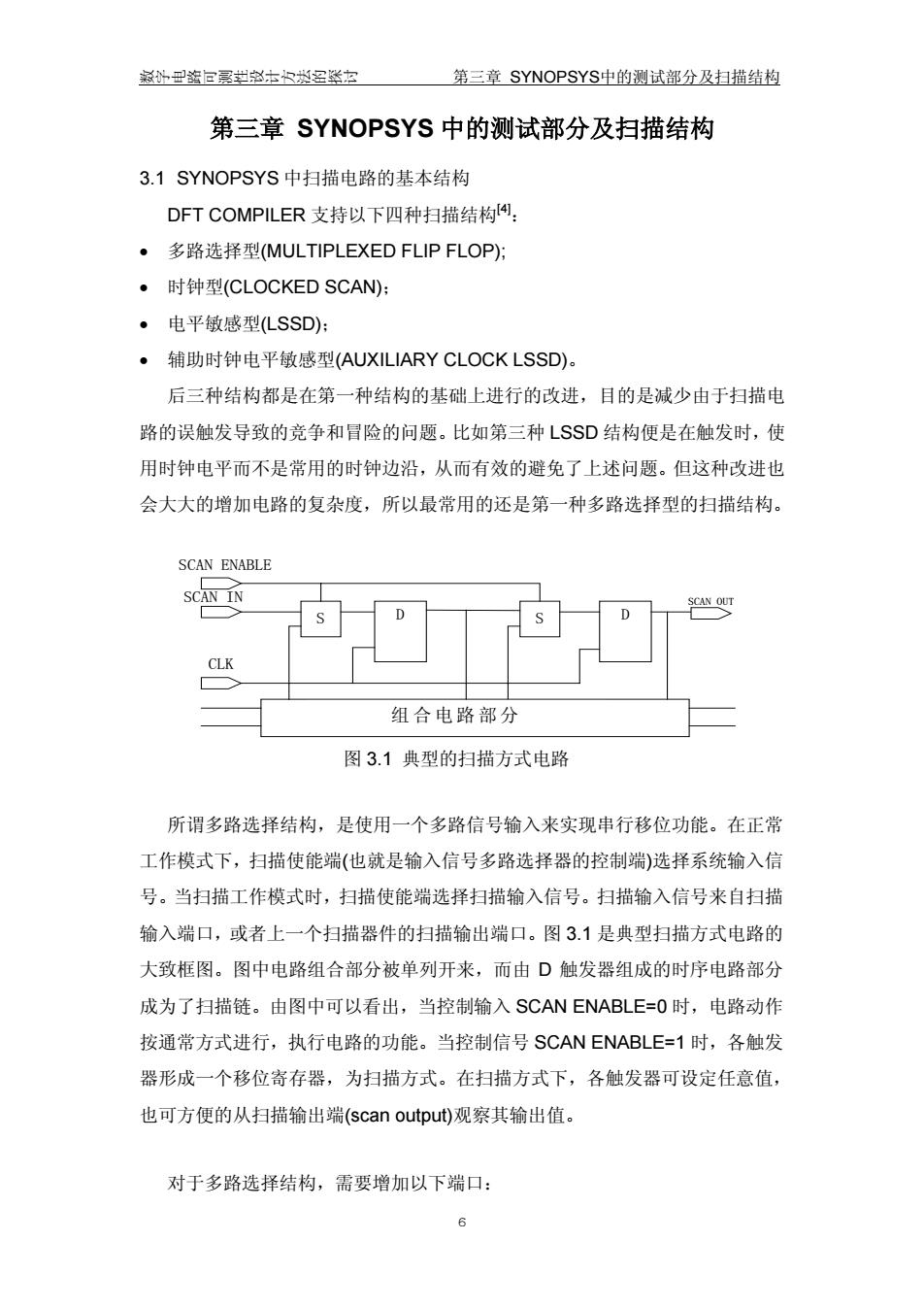

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第三章 SYNOPSYS中的测试部分及扫描结构 6 第三章 SYNOPSYS 中的测试部分及扫描结构 3.1 SYNOPSYS 中扫描电路的基本结构 DFT COMPILER 支持以下四种扫描结构[4]: • 多路选择型(MULTIPLEXED FLIP FLOP); • 时钟型(CLOCKED SCAN); • 电平敏感型(LSSD); • 辅助时钟电平敏感型(AUXILIARY CLOCK LSSD)。 后三种结构都是在第一种结构的基础上进行的改进,目的是减少由于扫描电 路的误触发导致的竞争和冒险的问题。比如第三种 LSSD 结构便是在触发时,使 用时钟电平而不是常用的时钟边沿,从而有效的避免了上述问题。但这种改进也 会大大的增加电路的复杂度,所以最常用的还是第一种多路选择型的扫描结构。 所谓多路选择结构,是使用一个多路信号输入来实现串行移位功能。在正常 工作模式下,扫描使能端(也就是输入信号多路选择器的控制端)选择系统输入信 号。当扫描工作模式时,扫描使能端选择扫描输入信号。扫描输入信号来自扫描 输入端口,或者上一个扫描器件的扫描输出端口。图 3.1 是典型扫描方式电路的 大致框图。图中电路组合部分被单列开来,而由 D 触发器组成的时序电路部分 成为了扫描链。由图中可以看出,当控制输入 SCAN ENABLE=0 时,电路动作 按通常方式进行,执行电路的功能。当控制信号 SCAN ENABLE=1 时,各触发 器形成一个移位寄存器,为扫描方式。在扫描方式下,各触发器可设定任意值, 也可方便的从扫描输出端(scan output)观察其输出值。 对于多路选择结构,需要增加以下端口: S D S D SCAN ENABLE SCAN IN CLK SCAN OUT 组合电路部分 图 3.1 典型的扫描方式电路

滋的已篮日景型士R州妇继名 第三章SYNOPSYS中的测试部分及扫描结构 ●扫描输入(SCAN IN) ●扫描使能(SCAN ENABLE) ●扫描输出(SCAN OUTPUT) 其中扫描输入端必须单独列出,而扫描输入和扫描输出都可以和其它管脚公 用,所以扫描结构所增加的管脚数也十分有限。 scan_in g/scan_out (est_scan_i间 ecn山 scan_enable qb/scan_outinverted (estscan_onable】 (bast_scan_out_inverted) clk 图3.2 SYNOPSYS中D触发器的扫描结构 大多数器件库都支持多路选择结构的D触发器,但大都不支持锁存器模型 (LATCH)。图3.2为转换后默认的多路选择结构D触发器结构,框图中的S是 二路选择器。下面是其真值表。 d scan_in scan_enable clk qb Mode 0 X 0 平 0 Functional 1 X 0 平 Functional 0 1 平 Scan X 平 0 Scan 0/1 gb Either ↑=时钟上升沿 X=无关 表3.1二路选择器的真值表 多路选择结构的特征: ●由于在电路中增加了多路选择器,会导致电路正常工作时,额外延时的 增加。 ●对于芯片面积的增加较少。多路选择型的D触发器比一般的D触发器增 加15到30%的芯片面积。 ●最少只需要增加一个SCAN ENABLE管脚。扫描输入、输出管脚可以与 7

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第三章 SYNOPSYS中的测试部分及扫描结构 7 z 扫描输入(SCAN IN) z 扫描使能(SCAN ENABLE) z 扫描输出(SCAN OUTPUT) 其中扫描输入端必须单独列出,而扫描输入和扫描输出都可以和其它管脚公 用,所以扫描结构所增加的管脚数也十分有限。 大多数器件库都支持多路选择结构的 D 触发器,但大都不支持锁存器模型 (LATCH)。图 3.2 为转换后默认的多路选择结构 D 触发器结构,框图中的 S 是 二路选择器。下面是其真值表。 多路选择结构的特征: z 由于在电路中增加了多路选择器,会导致电路正常工作时,额外延时的 增加。 z 对于芯片面积的增加较少。多路选择型的 D 触发器比一般的 D 触发器增 加 15 到 30%的芯片面积。 z 最少只需要增加一个 SCAN ENABLE 管脚。扫描输入、输出管脚可以与 图 3.2 SYNOPSYS 中 D 触发器的扫描结构 时钟上升沿 无关 表 3.1 二路选择器的真值表

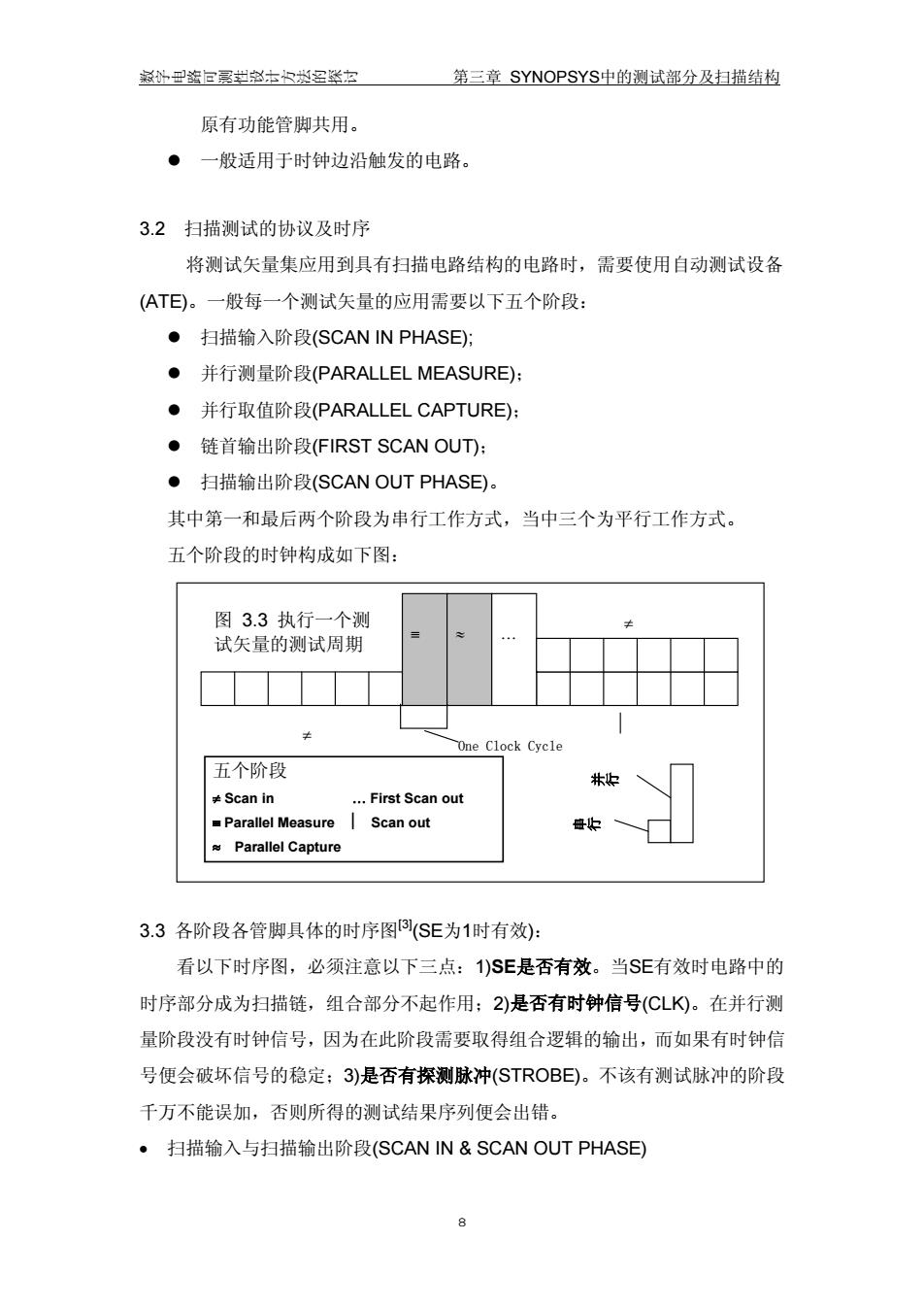

兹的巴篮包悬型出本收兴名举女 第三章SYNOPSYS中的测试部分及扫描结构 原有功能管脚共用。 ● 一般适用于时钟边沿触发的电路。 3.2扫描测试的协议及时序 将测试矢量集应用到具有扫描电路结构的电路时,需要使用自动测试设备 (ATE)。一般每一个测试矢量的应用需要以下五个阶段: ●扫描输入阶段(SCAN IN PHASE); ·并行测量阶段(PARALLEL MEASURE): ●并行取值阶段(PARALLEL CAPTURE): ·链首输出阶段(FIRST SCAN OUT): ●扫描输出阶段(SCAN OUT PHASE)。 其中第一和最后两个阶段为串行工作方式,当中三个为平行工作方式。 五个阶段的时钟构成如下图: 图3.3执行一个测 试矢量的测试周期 4+ One Clock Cycle 五个阶段 ≠Scan in ..First Scan out Parallel Measure Scan out 母点 Parallel Capture 3.3各阶段各管脚具体的时序图3(SE为1时有效): 看以下时序图,必须注意以下三点:1)SE是否有效。当SE有效时电路中的 时序部分成为扫描链,组合部分不起作用:2)是否有时钟信号(CL)。在并行测 量阶段没有时钟信号,因为在此阶段需要取得组合逻辑的输出,而如果有时钟信 号便会破坏信号的稳定;3)是否有探测脉冲(STROBE)。不该有测试脉冲的阶段 千万不能误加,否则所得的测试结果序列便会出错。 ·扫描输入与扫描输出阶段(SCAN IN&SCAN OUT PHASE)

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第三章 SYNOPSYS中的测试部分及扫描结构 8 原有功能管脚共用。 z 一般适用于时钟边沿触发的电路。 3.2 扫描测试的协议及时序 将测试矢量集应用到具有扫描电路结构的电路时,需要使用自动测试设备 (ATE)。一般每一个测试矢量的应用需要以下五个阶段: z 扫描输入阶段(SCAN IN PHASE); z 并行测量阶段(PARALLEL MEASURE); z 并行取值阶段(PARALLEL CAPTURE); z 链首输出阶段(FIRST SCAN OUT); z 扫描输出阶段(SCAN OUT PHASE)。 其中第一和最后两个阶段为串行工作方式,当中三个为平行工作方式。 五个阶段的时钟构成如下图: 3.3 各阶段各管脚具体的时序图[3](SE为1时有效): 看以下时序图,必须注意以下三点:1)SE是否有效。当SE有效时电路中的 时序部分成为扫描链,组合部分不起作用;2)是否有时钟信号(CLK)。在并行测 量阶段没有时钟信号,因为在此阶段需要取得组合逻辑的输出,而如果有时钟信 号便会破坏信号的稳定;3)是否有探测脉冲(STROBE)。不该有测试脉冲的阶段 千万不能误加,否则所得的测试结果序列便会出错。 • 扫描输入与扫描输出阶段(SCAN IN & SCAN OUT PHASE) ≡ ≈ … 图 3.3 执行一个测 试矢量的测试周期 ≠ ≠ O n e C l o c k C y c l e 五个阶段 ≠ Scan in … First Scan out ≡ Parallel Measure Scan out ≈ Parallel Capture 并 行 串 行