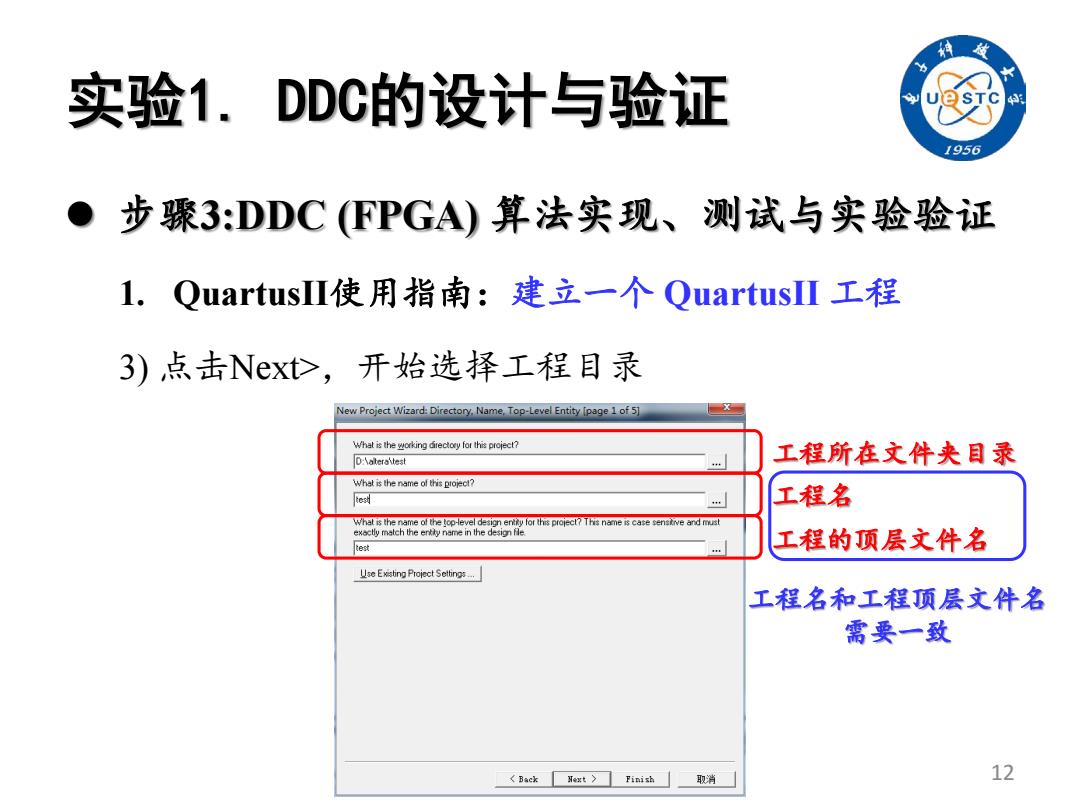

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南:建立一个QuartusIⅡ工程 3)点击Next>,开始选择工程目录 New Project Wizard:Directory,Name,Top-Level Entity [page 1 of 5] What is the working directory for this project? D:\ateratest 工程所在文件夹目录 What is the name of this project? e到 工程名 What is the name of the top-evel design entity for this projecl?This name is case senstive and must exactly match the ently name in the design fle test 工程的顶层文件名 seExising Proiect Settings 工程名和工程顶层文件名 需要一致 《Back Next Finish 取消 12

12 步骤3:DDC (FPGA) 算法实现、测试与实验验证 1. QuartusII使用指南:建立一个 QuartusII 工程 3) 点击Next>,开始选择工程目录 工程所在文件夹目录 工程名 工程的顶层文件名 工程名和工程顶层文件名 需要一致 实验1. DDC的设计与验证

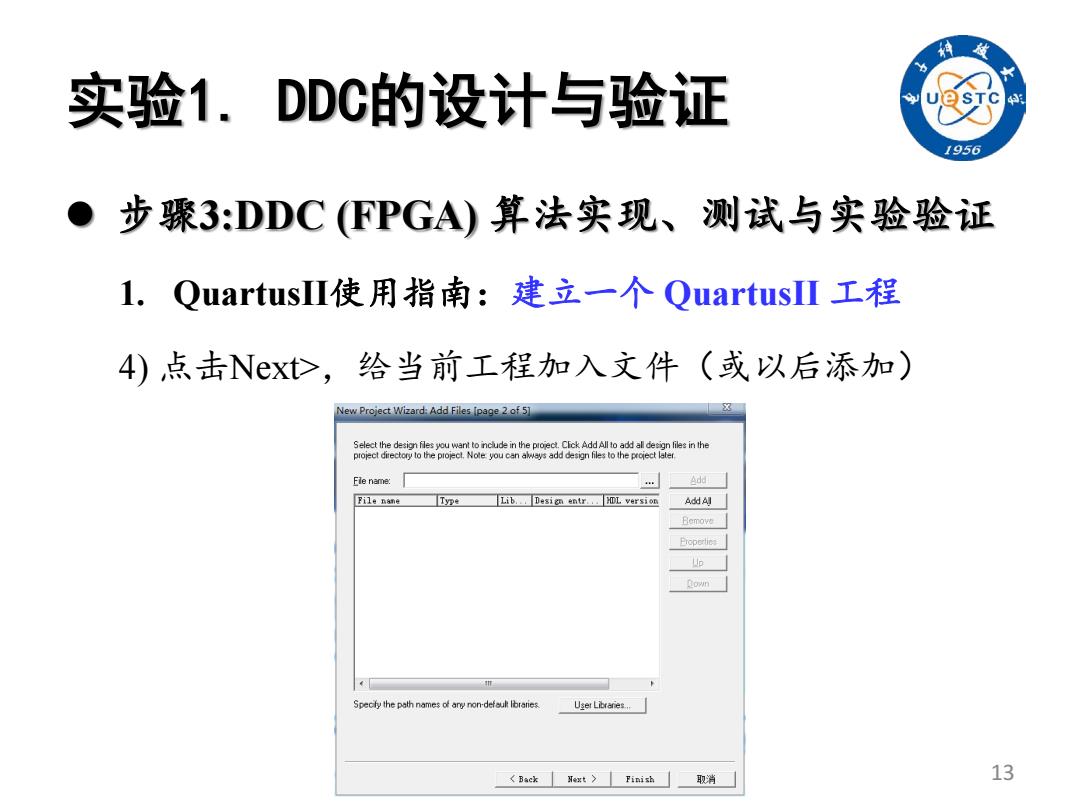

实验1.DDG的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南:建立一个QuartusⅡ工程 4)点击Next>,给当前工程加入文件(或以后添加) New Project Wizard:Add Files [page 2 of 5] Select the design fles you want to include in the proect.Clck Add All to add all design liles in the project ditectory to the project.Note you can always add design files to the project later. Fle name: Add Fi1。na Type Lib.Desien entr..HL version Ad时g Bemove Propertics Bown Specly the path names o any non-defaul lbraries Uger Libraries 《Back Moxt Finish 取消 13

13 步骤3:DDC (FPGA) 算法实现、测试与实验验证 1. QuartusII使用指南:建立一个 QuartusII 工程 4) 点击Next>,给当前工程加入文件(或以后添加) 实验1. DDC的设计与验证

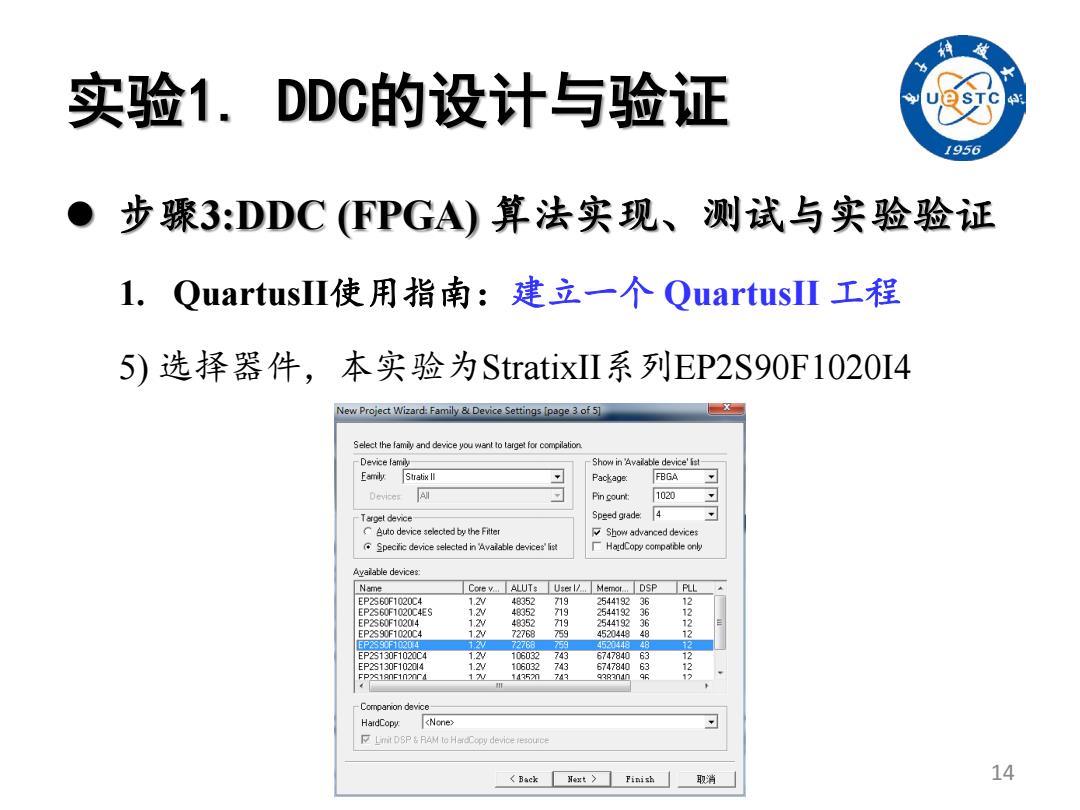

实验1.DDC的设计与验证 L956 步骤3:DDC(PGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南:建立一个QuartusⅡ工程 5)选择器件,本实验为StratixIⅡ系列EP2S90F1020I4 New Project Wizard:Family Device Settings [page 3 of 5] Select the famiy and device you want to target for compilation -Device family Show in Avaiable device'ist- Femily:Stratix Il Package FBGA Devices Pin gount: 1020 Target device Speed grade: 4 Auto device selected by the Fitter Show advanced devices Specific device selected in Avatable devices'list HadCopy compatible cnl Avaiable devices: Name Core v..ALUTs User 1/:.Memot...DSP PLL EP2560F1020C4 12y 48352 719 254419236 EP2S60F1020C4ES 1.2w 48352 19 2544192 EP2S60F10204 1 48352 719 2544192 EP2S90F1020C4 1.2w 72768 759 4520449 FP9年F10051 7276 52A EP2S130F1020C 1.2W 106032 743 6747840 63 EP2S130F1020I4 1%u 106032 743 74794n 1 143520 282n4n Comparion device HardCopy <None> Limit DSP&RAM to HerdCopy device fesouce 〈Back Next Finish 取消 14

14 步骤3:DDC (FPGA) 算法实现、测试与实验验证 1. QuartusII使用指南:建立一个 QuartusII 工程 5) 选择器件,本实验为StratixII系列EP2S90F1020I4 实验1. DDC的设计与验证