人 MIMJAYG UNEEEKITY 2,逻辑代数与硬件描述语言基础 2.1逻辑代数 2.2逻辑函数的卡诺图化简法 2.3硬件描述语言Verilog HDL基础 《》☐☐

2 .逻辑代数与硬件描述语言基础 2.1 逻辑代数 2.2 逻辑函数的卡诺图化简法 2.3 硬件描述语言Verilog HDL基础

教学基本要求 1、熟悉逻辑代数常用基本定律、恒等式 和规则。 2、掌握逻辑代数的变换和卡诺图化简法; 3、熟悉硬件描述语言Verilog HDL 《□》□国

教学基本要求 1、熟悉逻辑代数常用基本定律、恒等式 和规则。 3、熟悉硬件描述语言Verilog HDL 2、掌握逻辑代数的变换和卡诺图化简法;

XIMJAYG UNEEEKITY 2.1逻辑代数 2.1.1逻辑代数的基本定律和恒等式 2.1.2逻辑代数的基本规则 2.1.3逻辑函数的变换及代数化简法 《》☐☐

2.1.1 逻辑代数的基本定律和恒等式 2.1 逻辑代数 2.1.3 逻辑函数的变换及代数化简法 2.1.2 逻辑代数的基本规则

2.1逻辑代数 逻辑代数又称布尔代数。它是分析和设计现代数字逻辑电路不 可缺少的数学工具。逻辑代数有一系列的定律、定理和规则,用 于对数学表达式进行处理,以完成对逻辑电路的化简、变换、分 析和设计。 逻辑关系指的是事件产生的条件和结果之间的因果关系。在数 字电路中往往是将事情的条件作为输入信号,而结果用输出信号 表示。条件和结果的两种对立状态分别用逻辑“1和“0”表示。 《》☐4□

2.1 逻辑代数 逻辑代数又称布尔代数。它是分析和设计现代数字逻辑电路不 可缺少的数学工具。逻辑代数有一系列的定律、定理和规则,用 于对数学表达式进行处理,以完成对逻辑电路的化简、变换、分 析和设计。 逻辑关系指的是事件产生的条件和结果之间的因果关系。在数 字电路中往往是将事情的条件作为输入信号,而结果用输出信号 表示。条件和结果的两种对立状态分别用逻辑“1” 和“0”表示

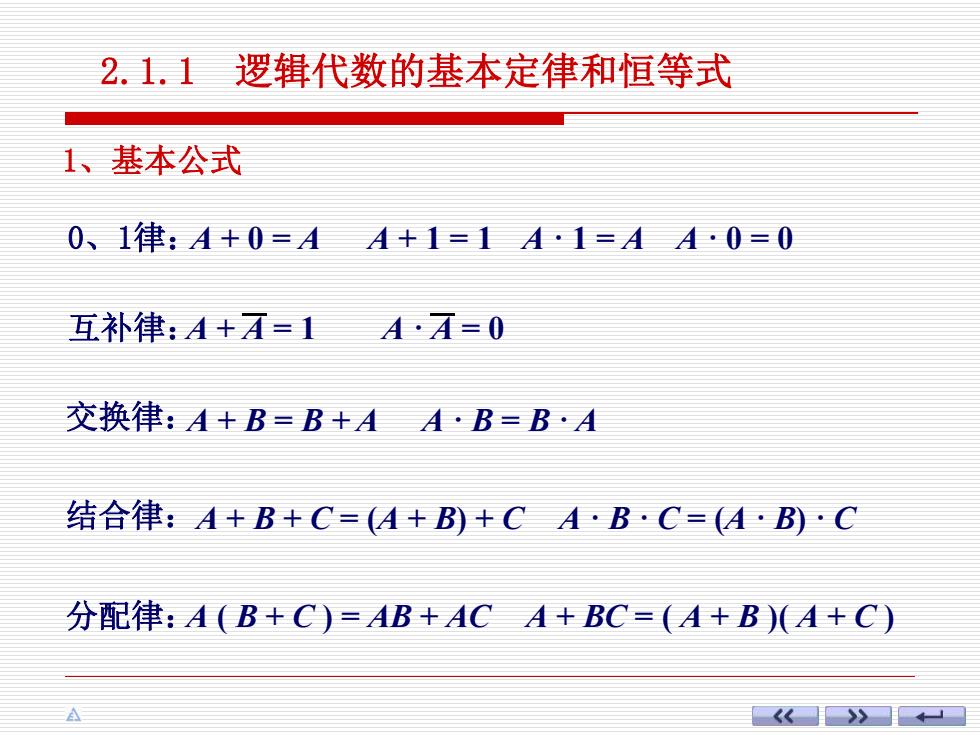

2.1.1逻辑代数的基本定律和恒等式 1、基本公式 0、1律:A+0=AA+1=1A·1=AA·0=0 互补律:A+A=1AA=0 交换律:A+B=B+AA·B=B·A 结合律:A+B+C=(A+B)+CA·B·C=AB)·C 分配律:A(B+C)=AB+ACA+BC=(A+B)(A+C) 父》☐回

1、基本公式 交换律:A + B = B + A A · B = B · A 结合律:A + B + C = (A + B) + C A · B · C = (A · B) · C 分配律:A ( B + C ) = AB + AC A + BC = ( A + B )( A + C ) 0、1律:A + 0 = A A + 1 = 1 A · 1 = A A · 0 = 0 互补律:A + A = 1 A · A = 0 2.1.1 逻辑代数的基本定律和恒等式