访存(mem access,图4-5,图4-7) ·读写控制:地址、数据、命令 一时钟同步假设:异步读,同步写,1个周期内 一读写不能同时:任一时刻只能完成读写之一 单端口(一读一写) MemWrite CLK Read address Address Read data Instruction Data Write memory Instruction data me mory MemRead

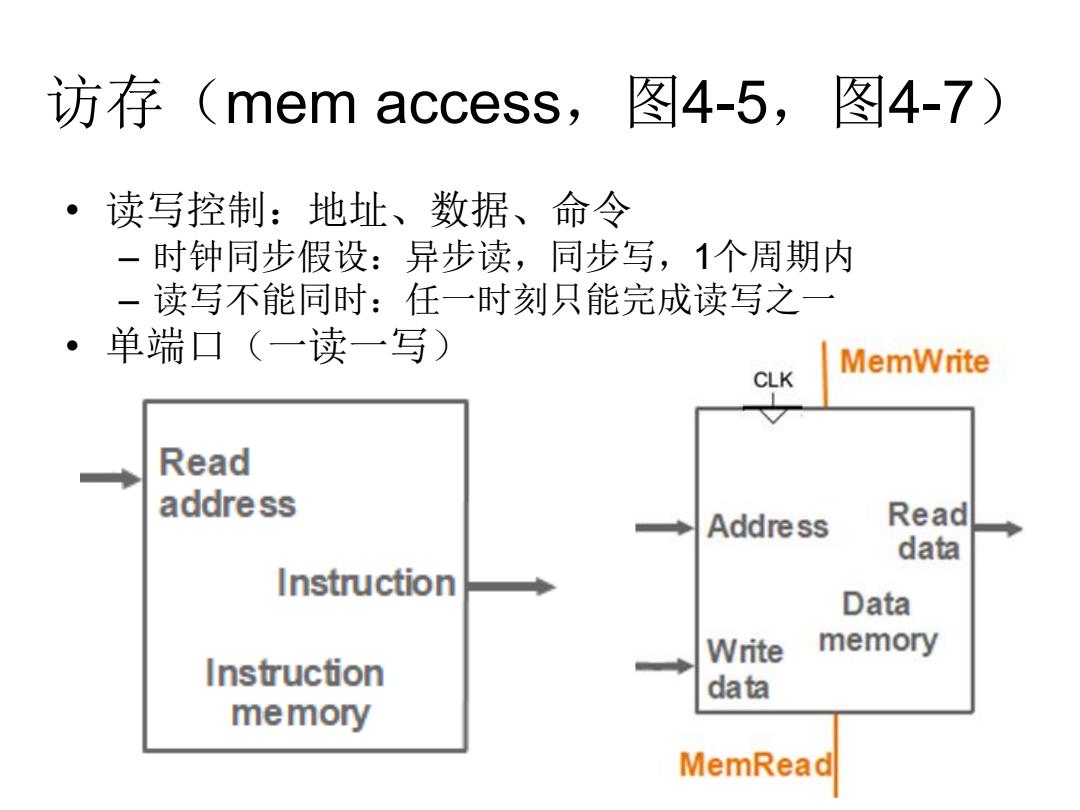

访存(mem access,图4-5,图4-7) • 读写控制:地址、数据、命令 – 时钟同步假设:异步读,同步写,1个周期内 – 读写不能同时:任一时刻只能完成读写之一 • 单端口(一读一写)

ALU Interface and Impl:A.5 ALU operation B F2 F1 FO Func. 0 0 0 A&B 0 0 1 AlB 1 0 A+B Zero 0 1 1 ALU Result 1 0 0 A&B Overflow 1 0 1 AlB 1 0 A-B 1 1 1 A B(slt) CarryOut ALU operation 图A-5-14 N-1S Extend Zero Zero N ALU ALU Add Sum result 10 N

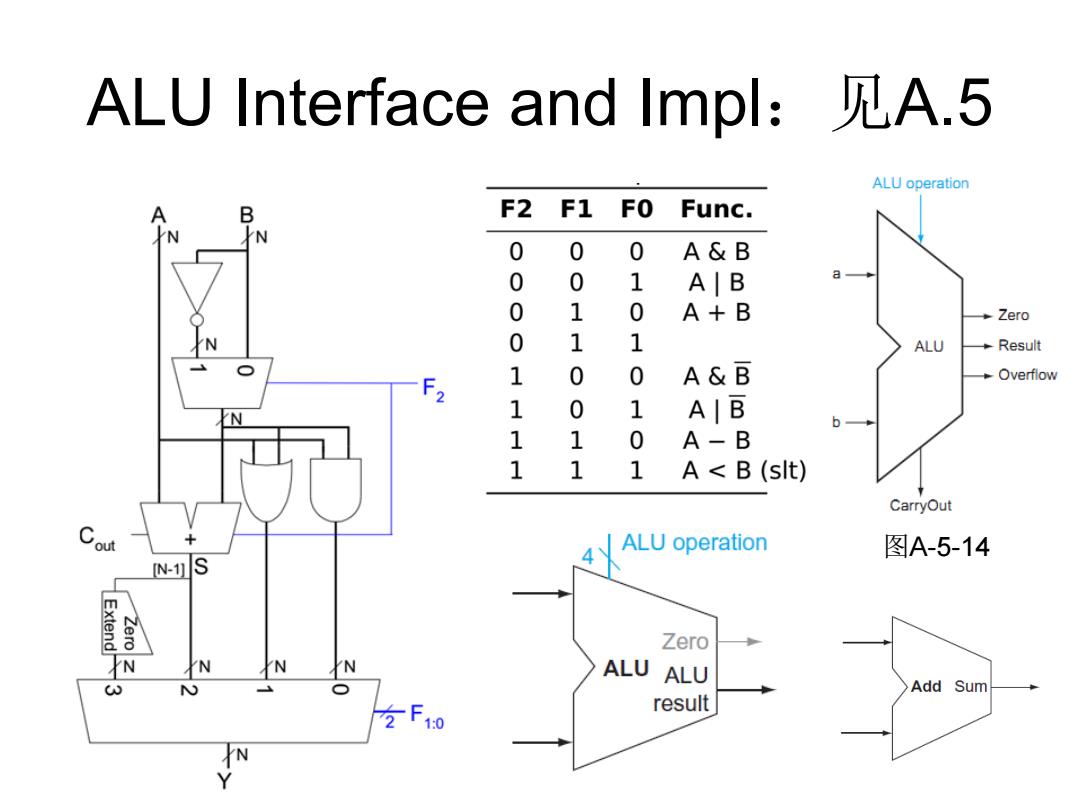

ALU Interface and Impl:见A.5 图A-5-14

同步电路、clk cycle、控制信号 C State Combinational logic Address A element Register file Address C Address B B Immediate value MuxB State State element C om bina tional lo gic element 2 InA InB ALU Out Clock cycle

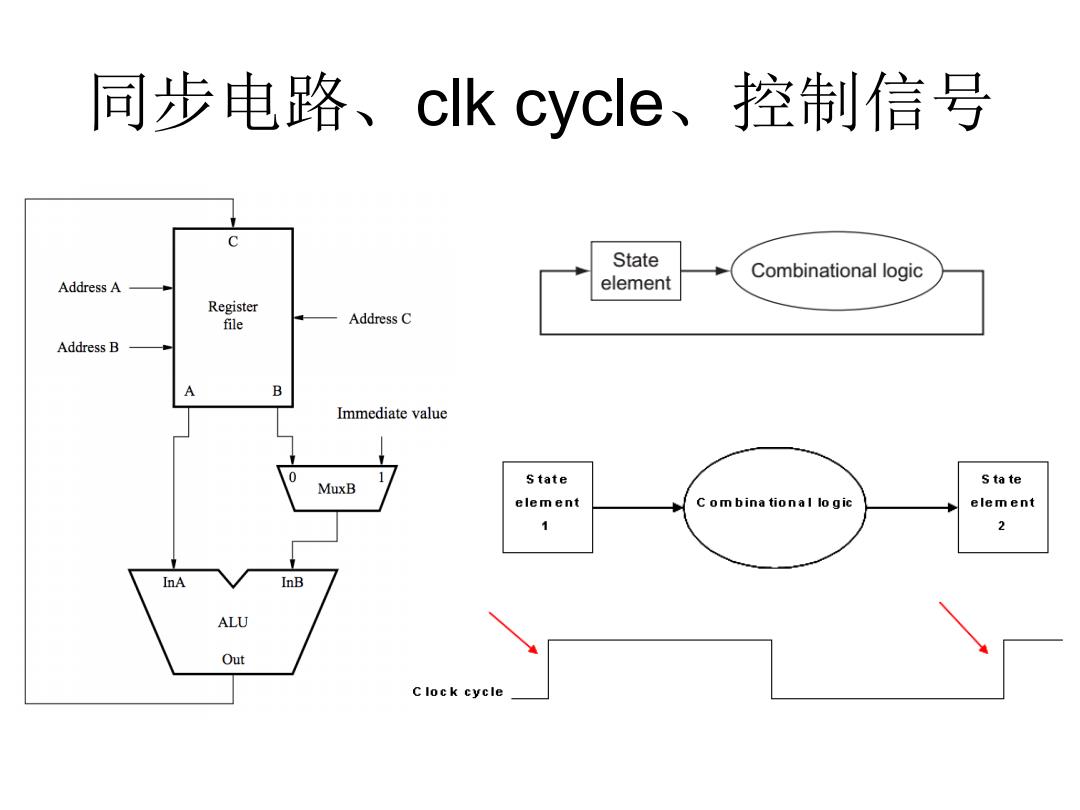

同步电路、clk cycle、控制信号

指令周期的定时模式 ·单周期实现:1指令周期=1时钟周期 -All stages of an instruction are completed within one long clock cycle. 一所需控制信号同时生成 1.Instruction 2.Decode/ 5.Reg. Fetch Register 3.Execute 4.Memory Write Read 0 多周期实现:指令周期=n时钟周期 Only one stage of instruction per clock cycle 一按时钟周期(=机器周期)生成当前周期所需控制信号 1.Instruction 2.Decode/ Fetch 3.Execute 4.Memory 5.Reg. Register Write Read 15

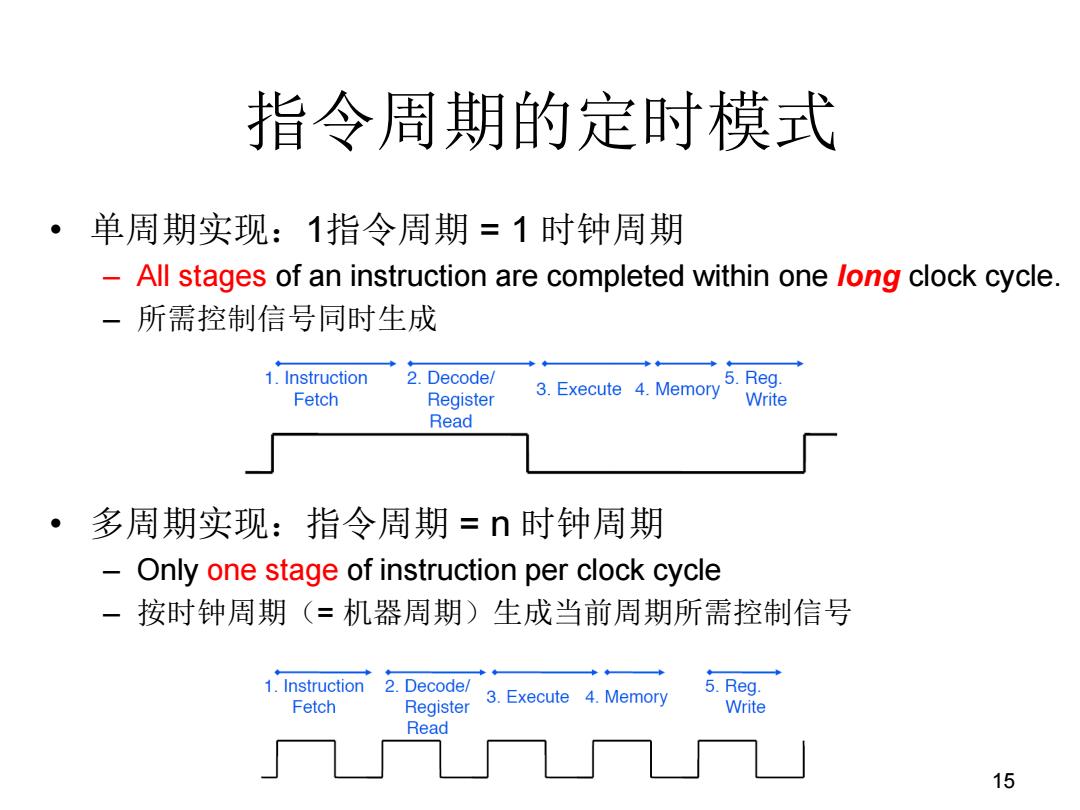

15 指令周期的定时模式 • 单周期实现:1指令周期 = 1 时钟周期 – All stages of an instruction are completed within one long clock cycle. – 所需控制信号同时生成 • 多周期实现:指令周期 = n 时钟周期 – Only one stage of instruction per clock cycle – 按时钟周期(= 机器周期)生成当前周期所需控制信号