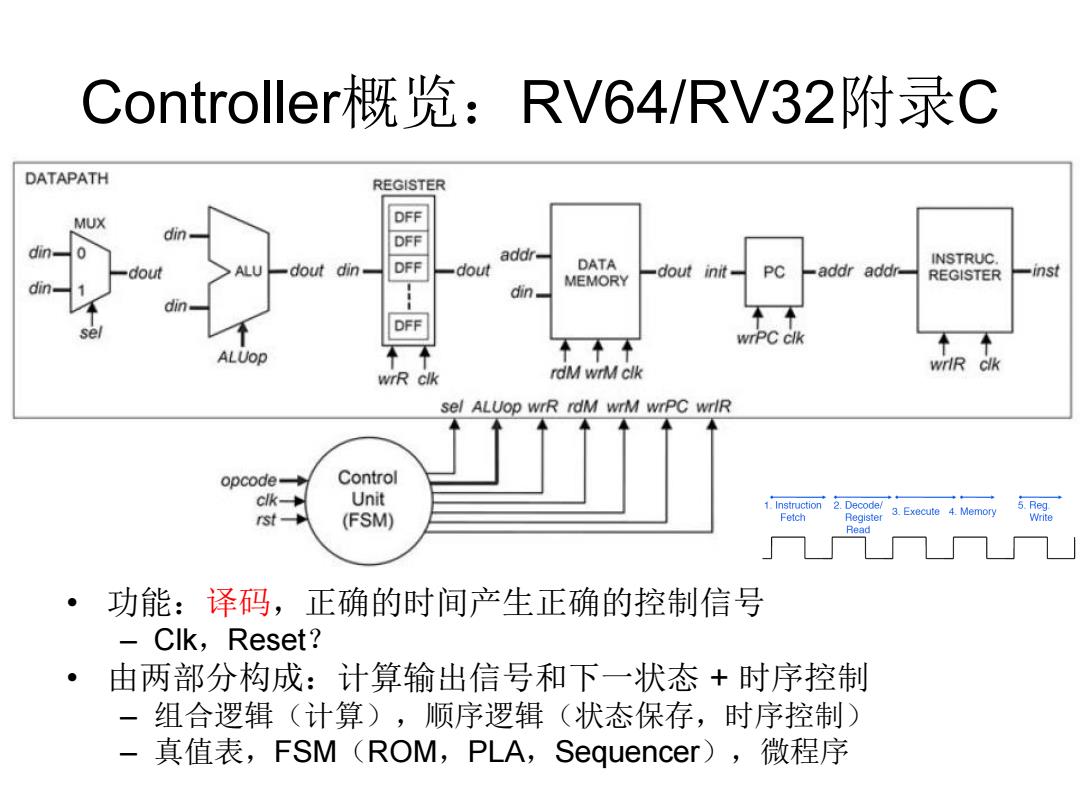

Controller慨览:RV64/RV32附录C DATAPATH REGISTER MUX DFF din DFF din- addr- DFF DATA INSTRUC. -dout ALU -dout din- -dout -dout init- PC -addr addr- REGISTER -inst din- MEMORY din din- sel DFF wrPC clk ALUop rdM wrM clk wrlR clk wrR clk sel ALUop wrR rdM wrM wrPC wrlR opcode- Control clk- Unit 1.Instruction 2.Decode/ 3.Execute 4.Memory 5.R6g (FSM) Fetch Register Write Read 功能:译码,正确的时间产生正确的控制信号 Clk,Reset? 由两部分构成:计算输出信号和下一状态+时序控制 一组合逻辑(计算),顺序逻辑(状态保存,时序控制) -真值表,FSM(ROM,PLA,Sequencer),微程序

Controller概览:RV64/RV32附录C • 功能:译码,正确的时间产生正确的控制信号 – Clk,Reset? • 由两部分构成:计算输出信号和下一状态 + 时序控制 – 组合逻辑(计算),顺序逻辑(状态保存,时序控制) – 真值表,FSM(ROM,PLA,Sequencer),微程序

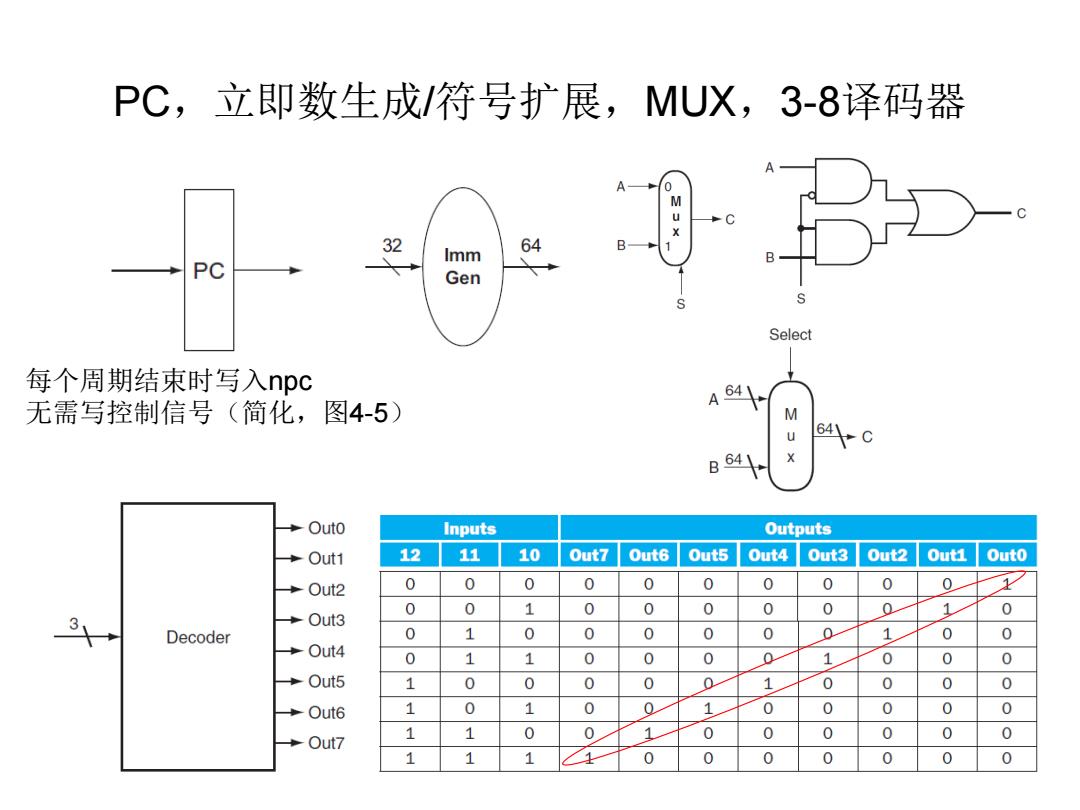

PC,立即数生成/符号扩展,MUX,3-8译码器 M 32 Imm 64 B PC Gen Select 每个周期结束时写入npc 无需写控制信号(简化,图4-5) M 641 64 Outo Inputs Outputs Out1 12 11 10 Out7 Out6 Out5 Out4 Out3 Out2 Out1 Outo Out2 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 Out3 Decoder 0 1 0 0 0 0 0 0 0 0 Out4 0 1 1 0 0 0 0 1 0 0 0 Out5 1 0 0 0 0 0 1 0 0 0 0 Out6 1 0 1 0 0 1 0 0 0 0 0 2 1 0 0 0 0 0 0 0 0 Out7 1 1 1 0 0 0 0 0 0 0

PC,立即数生成/符号扩展,MUX,3-8译码器 每个周期结束时写入npc 无需写控制信号(简化,图4-5)

$A.8.1:D触发器,寄存器 D Master Slave (Data) 0 Clock C C Clock D锁存器:ck电平控制 一位D触发器:ck边沿控制 Preset Preset 数据输入 数据输出 数据使能 D触发器 时钟 Clear 复位 带清零Clear和预置Preset的D触发器 一位寄存器,数据使能=write,clk

$A.8.1:D触发器,寄存器 D 锁存器:clk电平控制 一位 D 触发器:clk边沿控制 = = 带清零Clear和预置Preset的D 触发器 一位寄存器,数据使能=write,clk

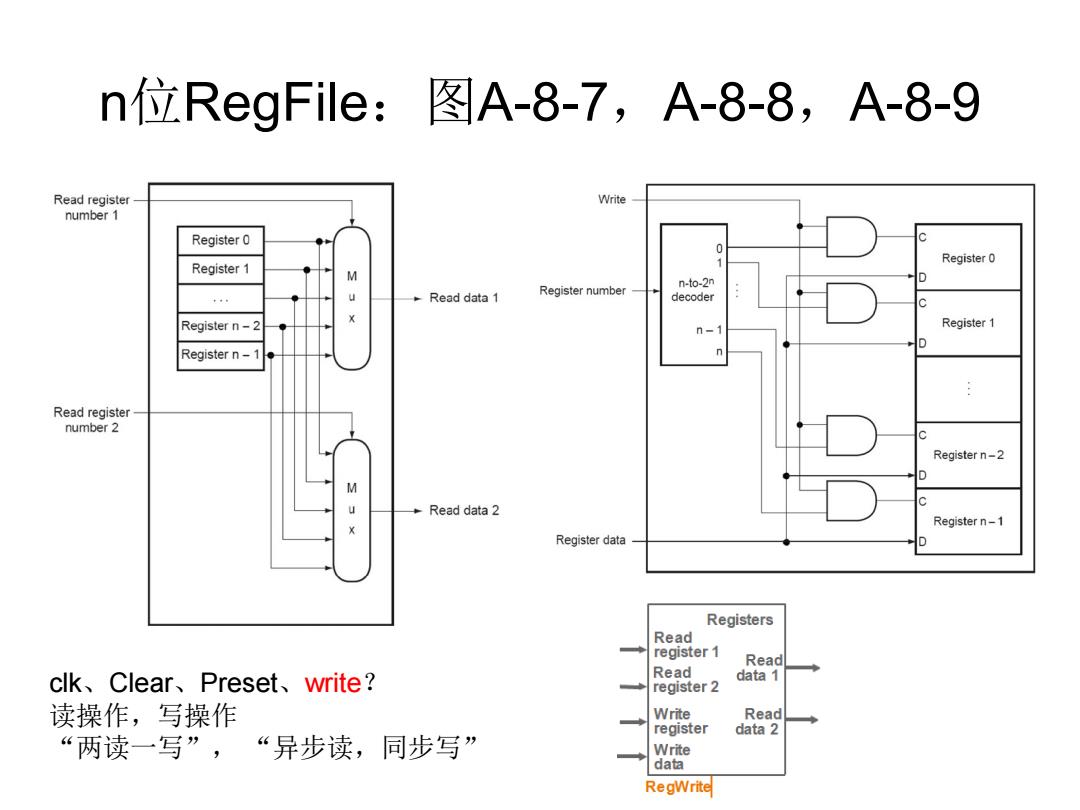

n位RegFile:图A-8-7,A-8-8,A-8-9 Read register Write number 1 Register 0 0 Register 0 Register 1 1 M n-to-2n u Read data 1 Register number decoder Register n-2 n-1 Register 1 Register n- n Read register number 2 Register n-2 M u Read data 2 Register n-1 Register data Registers Read register 1 Read clk、Clear、Preset、write? Read data 1 register 2 读操作,写操作 Write Read register data 2 “两读一写”,“异步读,同步写” Write data Re gWrite

n位RegFile:图A-8-7,A-8-8,A-8-9 clk、Clear、Preset、write? 读操作,写操作 “两读一写”, “异步读,同步写

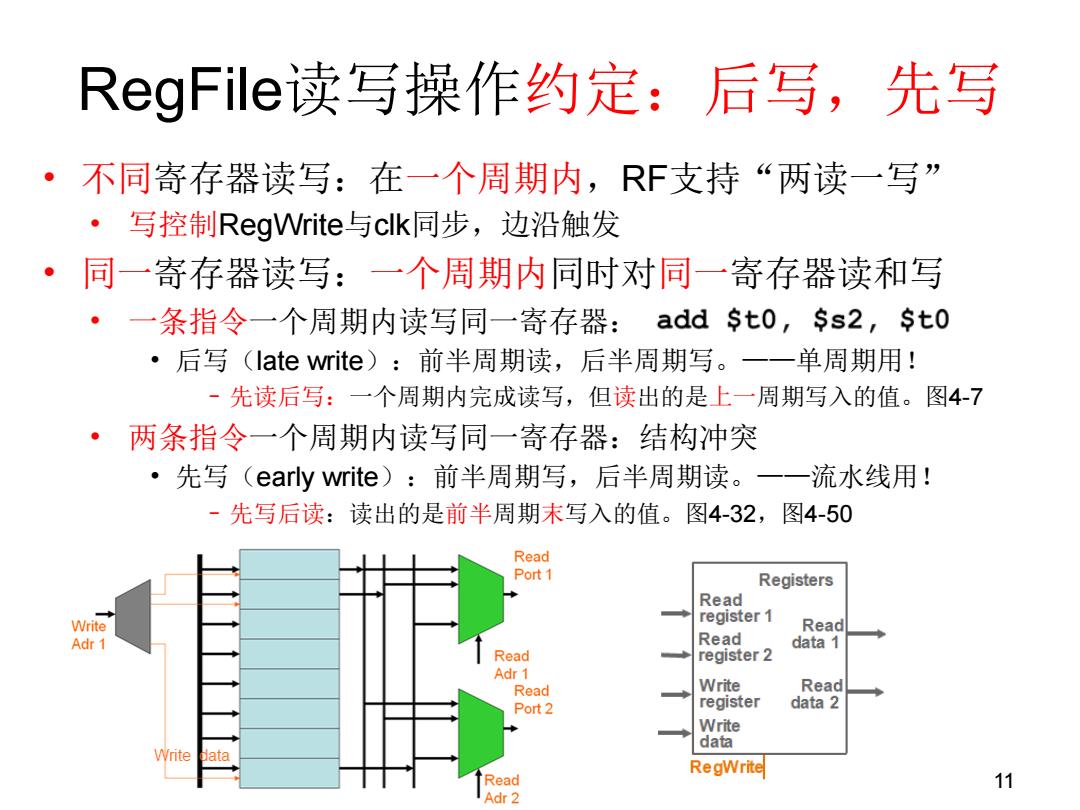

RegFile读写操作约定:后写,先写 ·不同寄存器读写:在一个周期内,RF支持“两读一写” ·写控制RegWrite.与clk同步,边沿触发 o 同一寄存器读写:一个周期内同时对同一寄存器读和写 一条指令一个周期内读写同一寄存器:add$t0,$s2,$t0 ·后写(late write):前半周期读,后半周期写。一一单周期用! -先读后写:一个周期内完成读写,但读出的是上一周期写入的值。图4-7 ·两条指令一个周期内读写同一寄存器: 结构冲突 ·先写(early write):前半周期写,后半周期读。一一流水线用! -先写后读:读出的是前半周期末写入的值。图4-32,图4-50 Read Port 1 Registers Read Write register 1 Read Adr 1 Read data 1 Read register 2 Adr 1 Read Write Read Port 2 register data 2 Write data Write RegWrite Read 11 Adr 2

RegFile读写操作约定:后写,先写 • 不同寄存器读写:在一个周期内,RF支持“两读一写” • 写控制RegWrite与clk同步,边沿触发 • 同一寄存器读写:一个周期内同时对同一寄存器读和写 • 一条指令一个周期内读写同一寄存器: • 后写(late write):前半周期读,后半周期写。——单周期用! –先读后写:一个周期内完成读写,但读出的是上一周期写入的值。图4-7 • 两条指令一个周期内读写同一寄存器:结构冲突 • 先写(early write):前半周期写,后半周期读。——流水线用! –先写后读:读出的是前半周期末写入的值。图4-32,图4-50 11