计算机组成原理 第5章层次化存储 概述,Cache llxx@ustc.edu.cn

计算机组成原理 第5章 层次化存储 概述,Cache llxx@ustc.edu.cn

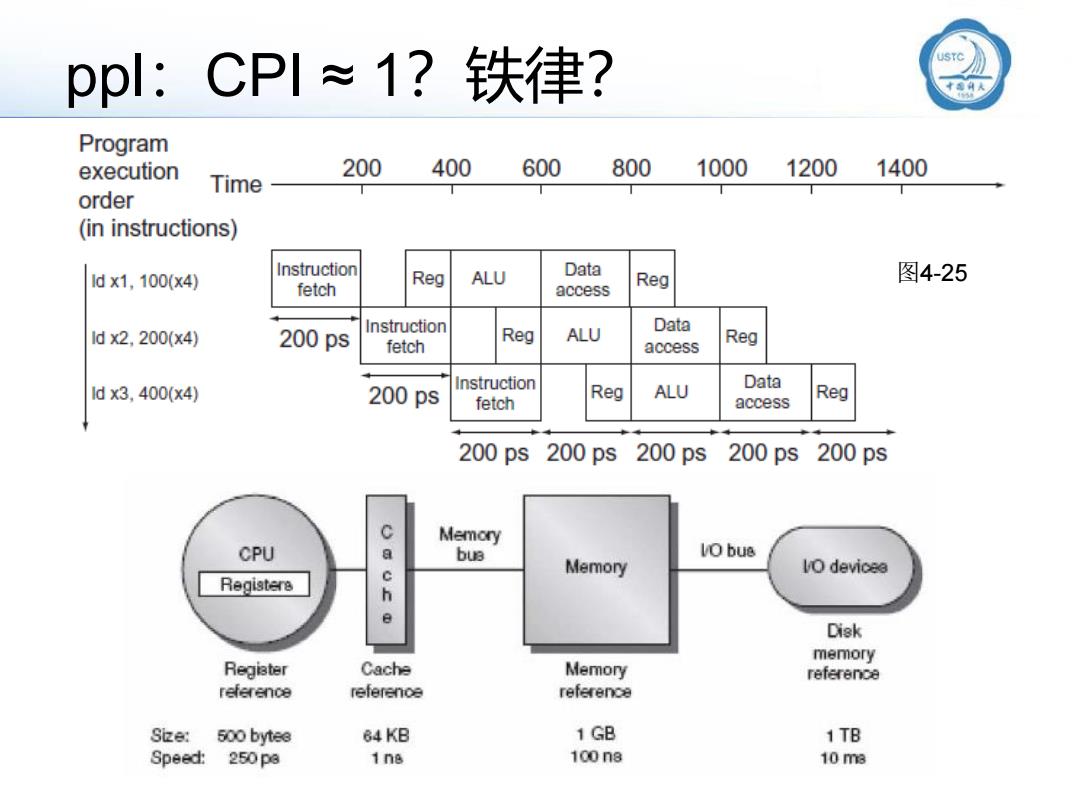

ppl:CPI≈1?铁律? Program execution 200 400 600 800 1000 1200 1400 Time order (in instructions) 1dx1,100(x4) Instruction fetch Reg ALU Data 图4-25 access Reg Data 1dx2,200(x4) 200ps Instruction ALU fetch Reg access Reg Data 1dx3.400(x4) 200ps Instruction fetch Reg ALU access Reg 200ps200ps200ps 200ps200ps Memory CPU G UE bu3 VO bue Memory VO devicea Registere e Disk memory Regiater Cache Memory reference reference referenoe reference Size:500 bytee 64KB 1 GB 1TB Speed: 250pa 1n8 100n8 10 me

ppl:CPI ≈ 1?铁律? 图4-25

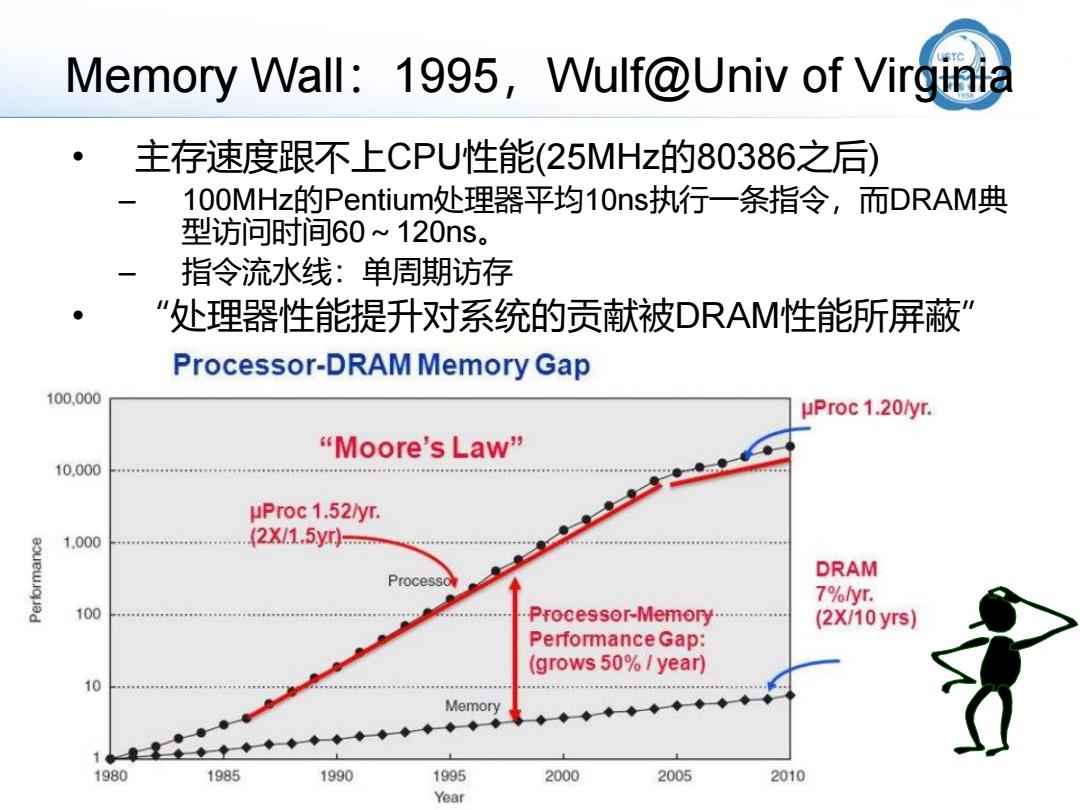

TC Memory Wall:1995,Wulf@Univ of Virginia 主存速度跟不上CPU性能(25MHz的80386之后) 100MHz的Pentium处理器平均10ns执行一条指令,而DRAM典 型访问时间60~120ns。 指令流水线:单周期访存 ● "处理器性能提升对系统的贡献被DRAM性能所屏蔽'” Processor-DRAM Memory Gap 100.000 μProc1.20y “Moore'sLaw" 10.000 μProc1.52yT. 1.000 (2X/1.5yr) DRAM Processo 7%yt. 100 Processor-Memory (2X/10yrs) Performance Gap: (grows 50%/year) 10 Memory 1980 1985 1990 1995 2000 2005 2010 Year

Memory Wall:1995,Wulf@Univ of Virginia • 主存速度跟不上CPU性能(25MHz的80386之后) – 100MHz的Pentium处理器平均10ns执行一条指令,而DRAM典 型访问时间60~120ns。 – 指令流水线:单周期访存 • “处理器性能提升对系统的贡献被DRAM性能所屏蔽

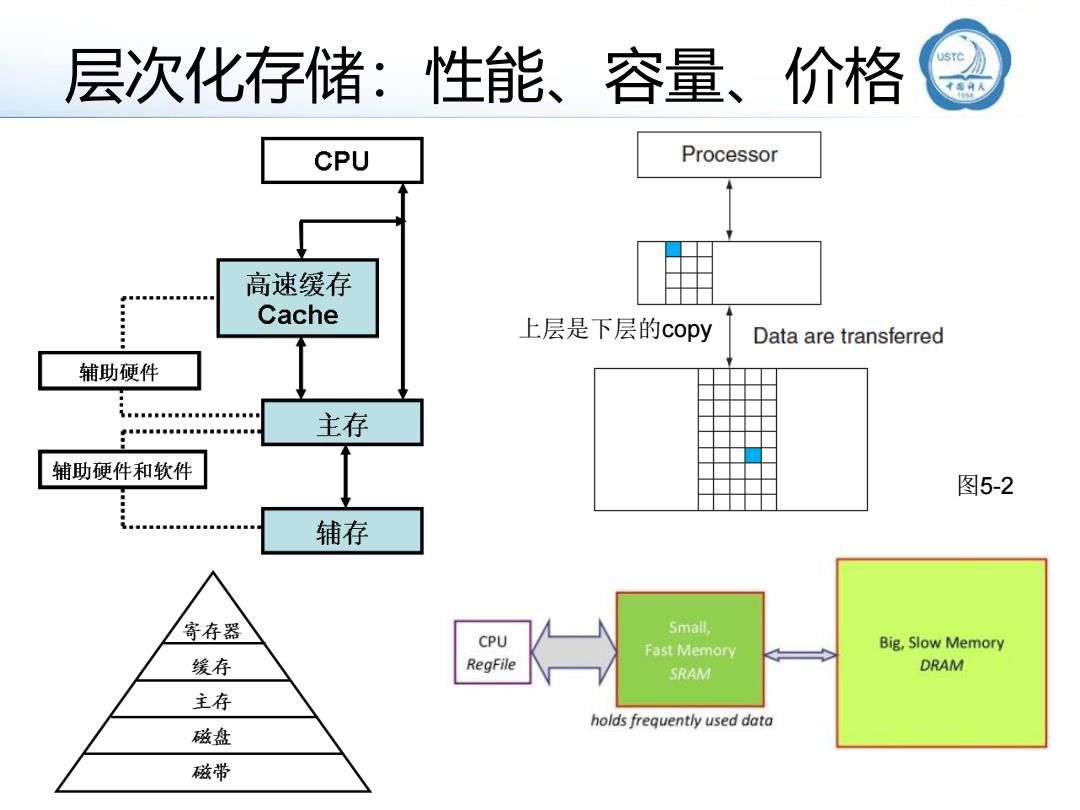

层次化存储:性能、容量、价格 CPU Processor 高速缓存 Cache 上层是下层的copy Data are transferred 辅助硬件 : 0.008008000复■000000 主存 辅助硬件和软件 图5-2 辅存 寄存器 Small, CPU Fast Memory Big,Slow Memory 缓存 RegFile SRAM DRAM 主存 holds frequently used data 磁盘 磁带

层次化存储:性能、容量、价格 上层是下层的copy 图5-2

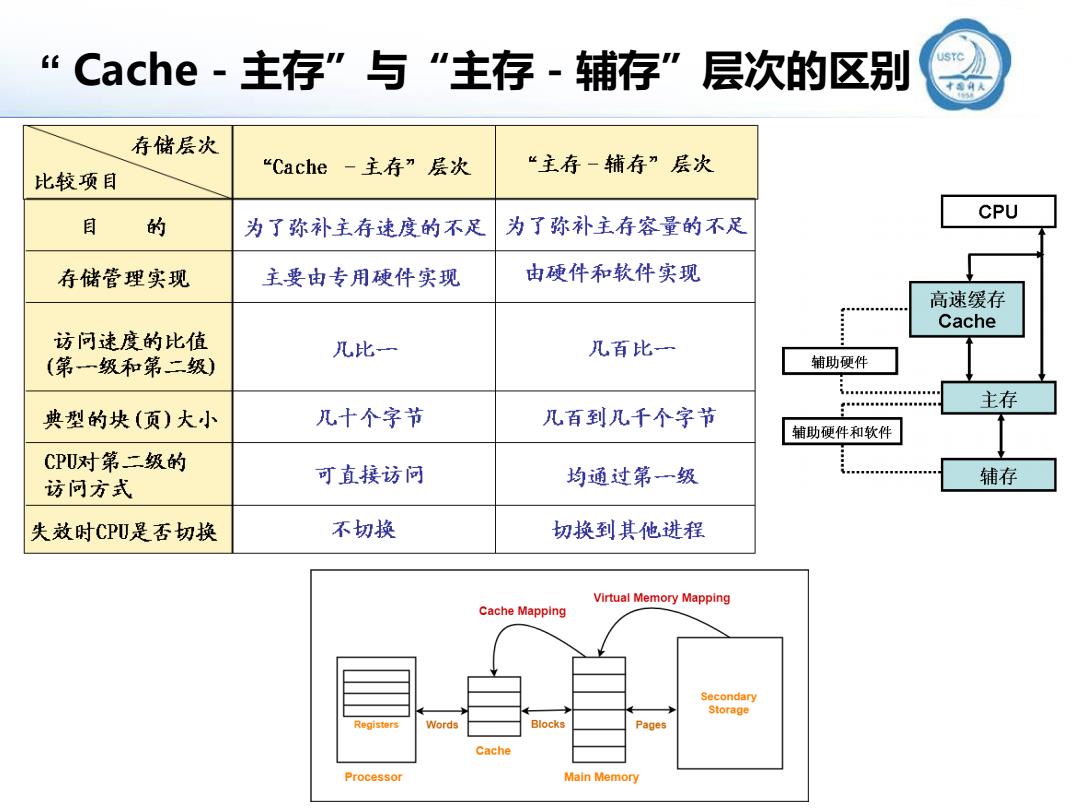

Cache-主存”与“主存-辅存”层次的区别 sc》 存储层次 “Cache-主存”层次 “主存一辅存”层次 比较项目 CPU 目 的 为了弥补主存速度的不足 为了弥补主存容量的不足 存储管理实现 主要由专用硬件实现 由硬件和软件实现 高速缓存 Cache 访问速度的比值 几比一 几百比一 (第一级和第二级) 辅助硬件 飞84■88■88588 主存 典型的块(页)大小 几十个字节 几百到几千个字节 辅助硬件和软件 CPU对第二级的 访问方式 可直接访问 均通过第一级 辅存 失效时CPU是否切换 不切换 切换到其他进程 Virtual Memory Mapping Cache Mapping Secondary Storage Registers Words Blocks Pages Cache Processor Main Memory

“ Cache-主存”与“主存-辅存”层次的区别