中国种学技术大学 计算机组成原理 系统互连与通信—总线 (RV$6.9,唐第3章) 李曦(llxx@ustc.edu.cn)

计算机组成原理 系统互连与通信——总线 (RV $6.9,唐第3章) 李曦(llxx@ustc.edu.cn)

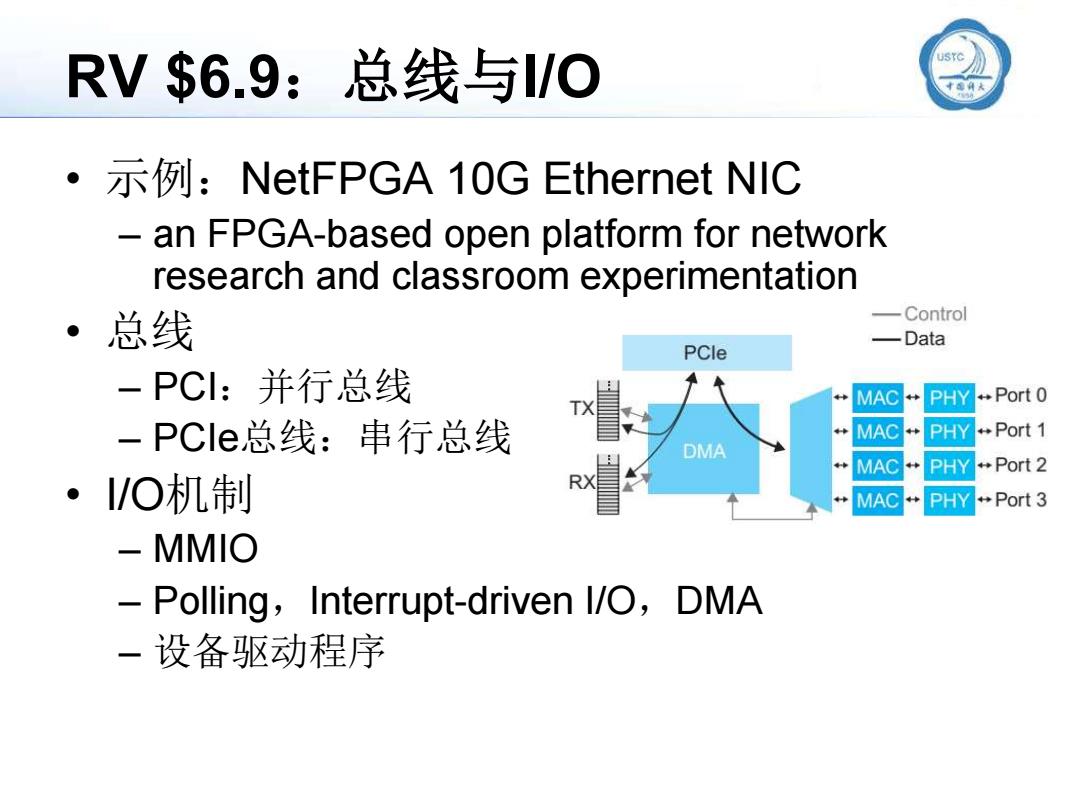

RV$6.9:总线与Vo 》 ·示例:NetFPGA1 OG Ethernet NIC an FPGA-based open platform for network research and classroom experimentation ·总线 —Control -Data PCle -PCI:并行总线 MAC PHY +Port 0 -PCIe总线:串行总线 PHY +Port 1 MA PHY +Port 2 ·VO机制 MAC PHY +Port 3 MMIO Polling,Interrupt-driven I/O,DMA 一设备驱动程序

RV $6.9:总线与I/O • 示例:NetFPGA 10G Ethernet NIC – an FPGA-based open platform for network research and classroom experimentation • 总线 – PCI:并行总线 – PCIe总线:串行总线 • I/O机制 – MMIO – Polling,Interrupt-driven I/O,DMA – 设备驱动程序

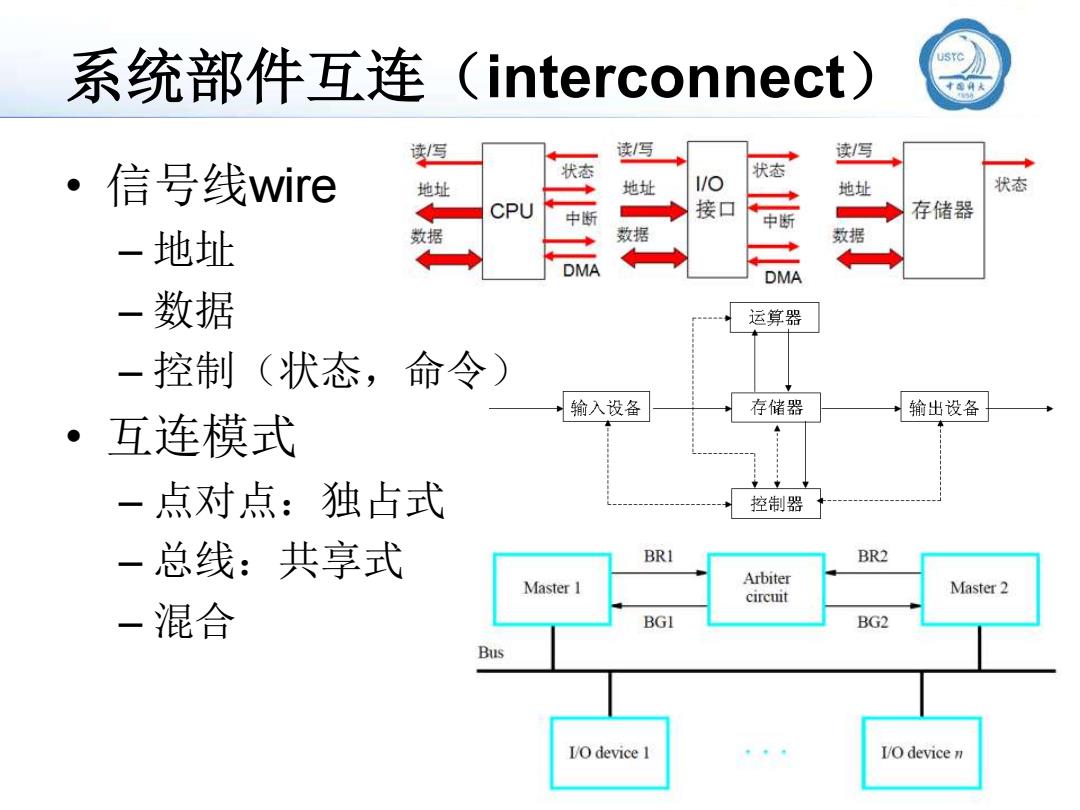

系统部件互连(interconnect) 读/写 读/写 ·信号线wire 状态 状态 地址 地址 地址 状态 CPU 中断 接口 中断 存储器 一地址 数据 数据 数据 DMA DMA 一 数据 运算器 -控制(状态,命令) 输入设备 存储器 输出设备 。 互连模式 一点对点:独占式 控制器 一总线:共享式 BR1 BR2 Master 1 Arbiter circuit Master 2 一混合 BG1 BG2 Bus IO device 1 I/O device n

• 信号线wire – 地址 – 数据 – 控制(状态,命令) • 互连模式 – 点对点:独占式 – 总线:共享式 – 混合 系统部件互连(interconnect)

"hello,world n" e》 片内总线 CPU 片外总线 寄存器文件 内部总线:系统总线,O总线 PC ALU 外围总线:外设总线 系统总线 存储器总线 主存 “he11o, world\n" 总线接可 储器 he11o代码 I/O总线 000 扩展槽,留待 USB 图形 网络适配器一 磁盘 控制器 类的设备使用 适配器 控制器 鼠标 键盘 显示器 “hello,world\n” 磁盘 存储在磁盘上的he11o 可执行文件

"hello, world\n" 片内总线 片外总线 内部总线:系统总线,I/O总线 外围总线:外设总线

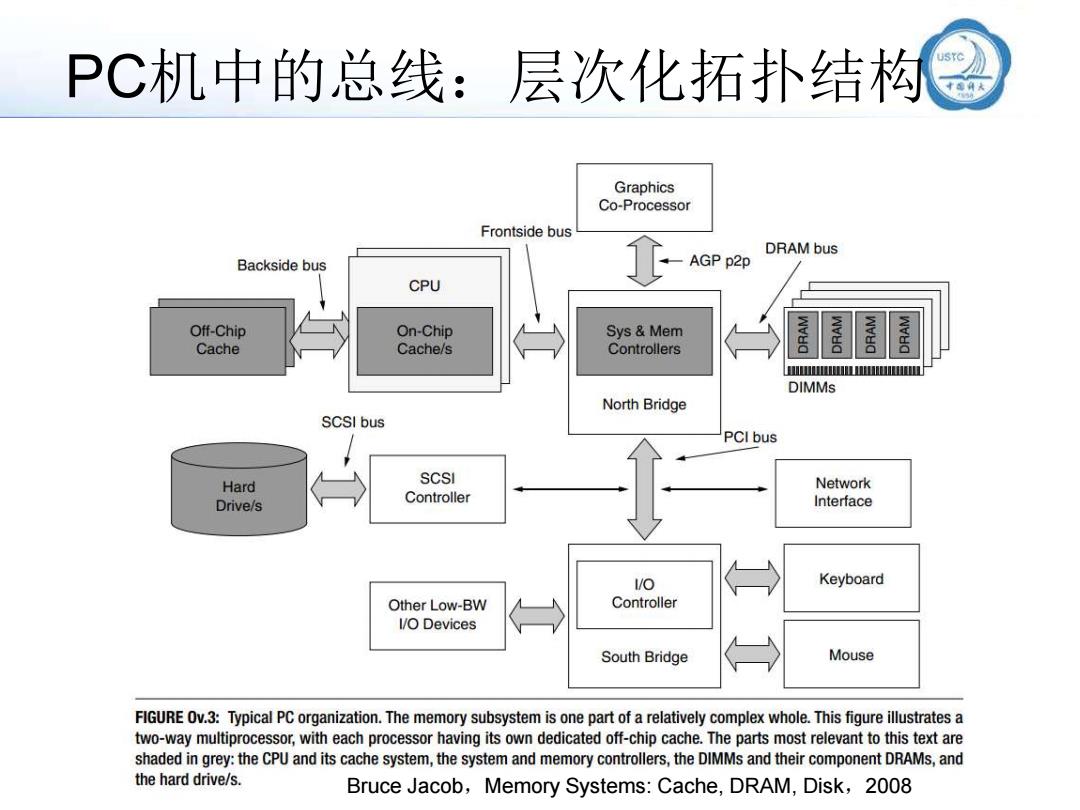

PC机中的总线:层次化拓扑结构 Graphics Co-Processor Frontside bus DRAM bus Backside bus AGP p2p CPU Off-Chip On-Chip Sys Mem Cache Cache/s Controllers DIMMs North Bridge SCSI bus PCI bus Hard SCSI Network Drive/s Controller Interface 1/O Keyboard Other Low-BW Controller 1/O Devices South Bridge Mouse FIGURE Ov.3:Typical PC organization.The memory subsystem is one part of a relatively complex whole.This figure illustrates a two-way multiprocessor,with each processor having its own dedicated off-chip cache.The parts most relevant to this text are shaded in grey:the CPU and its cache system,the system and memory controllers,the DIMMs and their component DRAMs,and the hard drive/s. Bruce Jacob,Memory Systems:Cache,DRAM,Disk,2008

PC机中的总线:层次化拓扑结构 Bruce Jacob,Memory Systems: Cache, DRAM, Disk,2008