内容提要 。流水线技术原理:4.5 。RV的五级流水线实现:4.6 。Hazard问题:4.5.2 一结构冲突:哈佛结构 -数据依赖:4.7 ·编译技术:插入nop,指令重排,寄存器重命名 ·forwarding技术:RAW 。Interlock技术:Stall -控制相关:4.8 ·编译技术:延迟分支 ·硬件优化:提前完成,投机,预测 。多发射技术:4.10 ·硬件多线程:6.4

内容提要 • 流水线技术原理:4.5 • RV的五级流水线实现:4.6 • Hazard问题:4.5.2 – 结构冲突:哈佛结构 – 数据依赖:4.7 • 编译技术:插入nop,指令重排,寄存器重命名 • forwarding技术:RAW • Interlock技术:Stall – 控制相关:4.8 • 编译技术:延迟分支 • 硬件优化:提前完成,投机,预测 • 多发射技术:4.10 • 硬件多线程:6.4

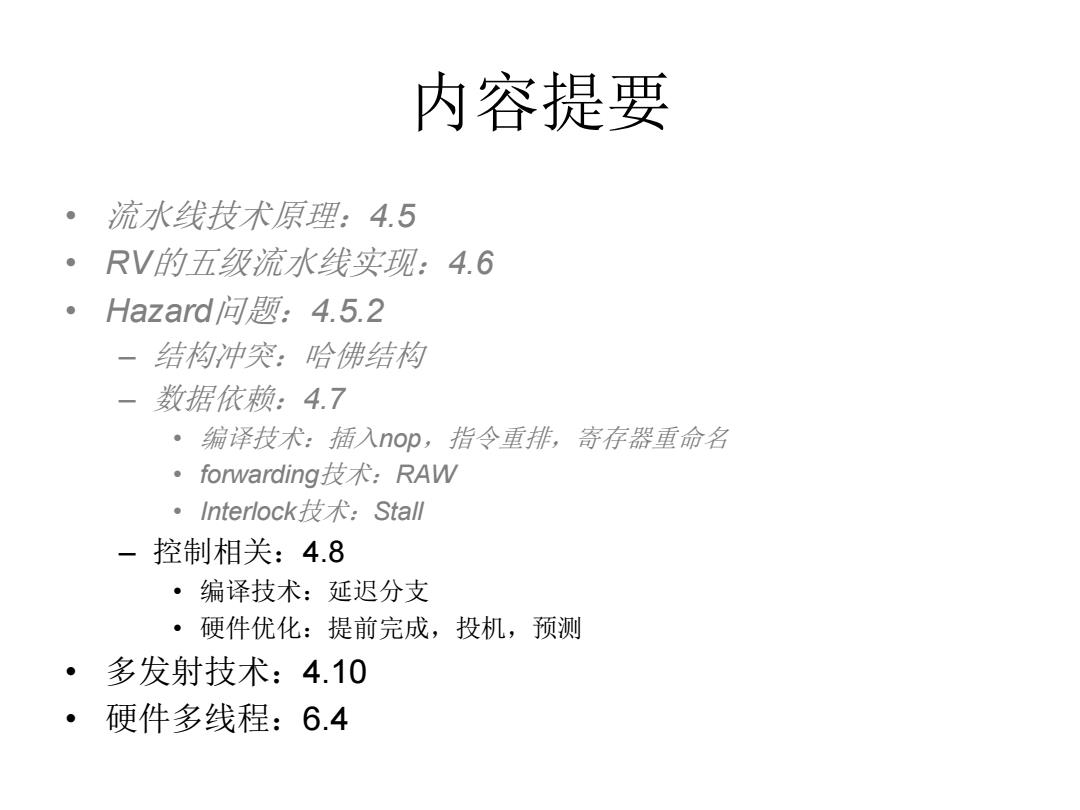

beq taken? Program Time (in clock cycles) execution CC 1 CC2 CC3 CC 5 C C6 CC 7 CC 8 CC9 order (in instructions) 40beq$1,$3,72 Reg 44and$12,$2,$5 Reg Reg 480r$13,s6,$2 IM eg DM Reg 52add$14,s2,$2 IM Reg Reg 72lw$4,50(s7) 图4-59 Reg llxx@ustc.edu.cn 3

llxx@ustc.edu.cn 3 beq taken? R e g R e g C C 1 T im e (in c lo c k c y c le s ) 4 0 b e q $ 1 , $ 3 , 72 P ro g ra m e x e c u tio n o rd e r (in in s tru c tio n s ) IM R e g IM D M IM D M IM D M D M D M R e g R e g R e g R e g R e g IM R e g 4 4 a n d $ 1 2 , $ 2 , $ 5 4 8 o r $ 1 3 , $ 6 , $ 2 5 2 a d d $ 1 4 , $ 2 , $ 2 7 2 lw $ 4 , 5 0 ($ 7 ) C C 2 C C 3 C C 4 C C 5 C C 6 C C 7 C C 8 C C 9 R e g 图4-59

Scep R-Type IRMemlPCI PC=PC+4 D A=ReI25-21 B=e2IH2015 beq指令完成时间? ALUOut .PC+(SEDR[15-0]1 <<2) EX ALUCut=Aop B ALLOu If (A==B)PC=PC[31-28] A+5夏0则15-00 PCALU0t时25-02 MEM Reg IR|15-111= MDR=Mem[ALUOut] ALUOu MemALUOut■B wB RegfiR[20-16]]=MDR ·以哪一条指令为基址? ·能否在EXE完成? PCSre IFAD ID/EX EXMEM NEMWB AddSu Shift left 1 Address MemWrite Read ALUSre Instruction register 2 Add ALU Read memory resul data dntn 2 Data memory data Instruction 31-q网 32 imm 64 Inetruction [30,14-12 ALU ont 图4-44 Instruction 11- ALUOp

beq指令完成时间? • 以哪一条指令为基址? • 能否在EXE完成? 图4-44

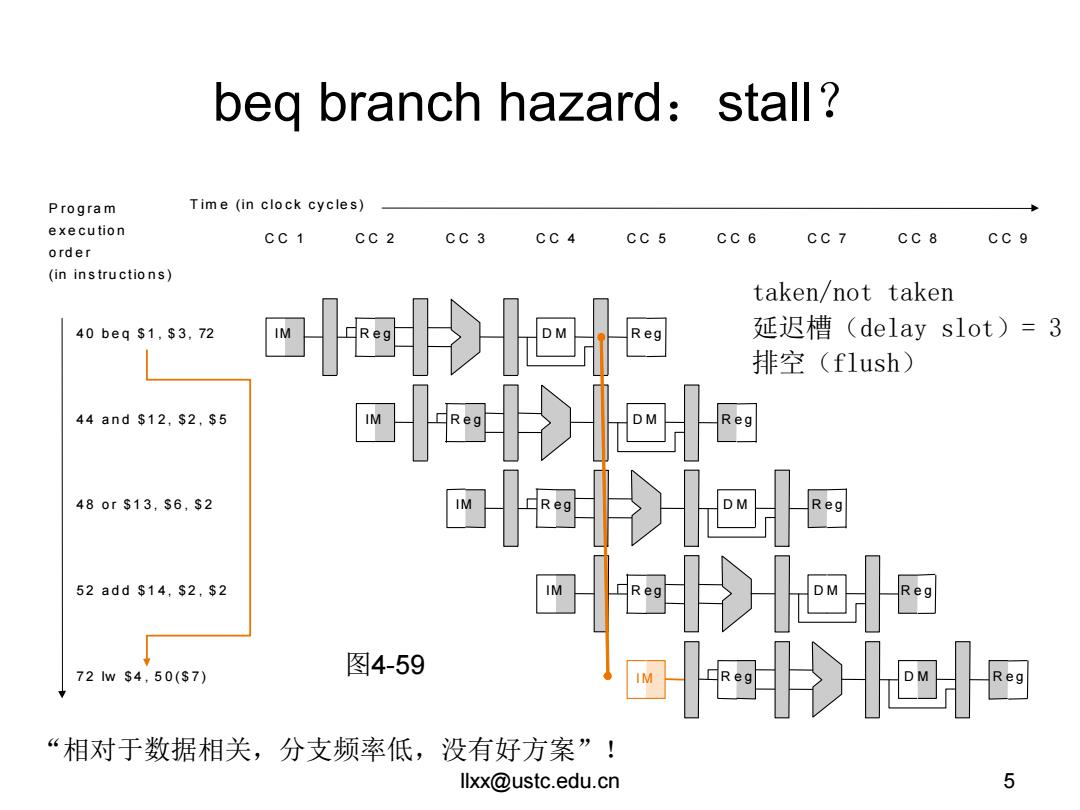

beg branch hazard:stall? Program Time (in clock cycles) execution CC 1 CC2 CC3 CC 5 CC 6 CC 7 CC 8 CC9 order (in instructions) taken/not taken 40beq$1,$3,72 Reg 延迟槽(delay slot)=3 排空(flush) 44and$12,$2,$5 Reg M Reg 480r$13,s6,$2 M Reg 52add$14,s2,$2 Reg 72Iw$4,50(s7) 图4-59 R 1 “相对于数据相关,分支频率低,没有好方案”! llxx@ustc.edu.cn 5

llxx@ustc.edu.cn 5 beq branch hazard:stall? R e g R e g C C 1 T im e (in c lo c k c y c le s ) 4 0 b e q $ 1 , $ 3 , 72 P ro g ra m e x e c u tio n o rd e r (in in s tru c tio n s ) IM R e g IM D M IM D M IM D M D M D M R e g R e g R e g R e g R e g IM R e g 4 4 a n d $ 1 2 , $ 2 , $ 5 4 8 o r $ 1 3 , $ 6 , $ 2 5 2 a d d $ 1 4 , $ 2 , $ 2 7 2 lw $ 4 , 5 0 ($ 7 ) C C 2 C C 3 C C 4 C C 5 C C 6 C C 7 C C 8 C C 9 R e g taken/not taken 延迟槽(delay slot)= 3 排空(flush) “相对于数据相关,分支频率低,没有好方案”! 图4-59

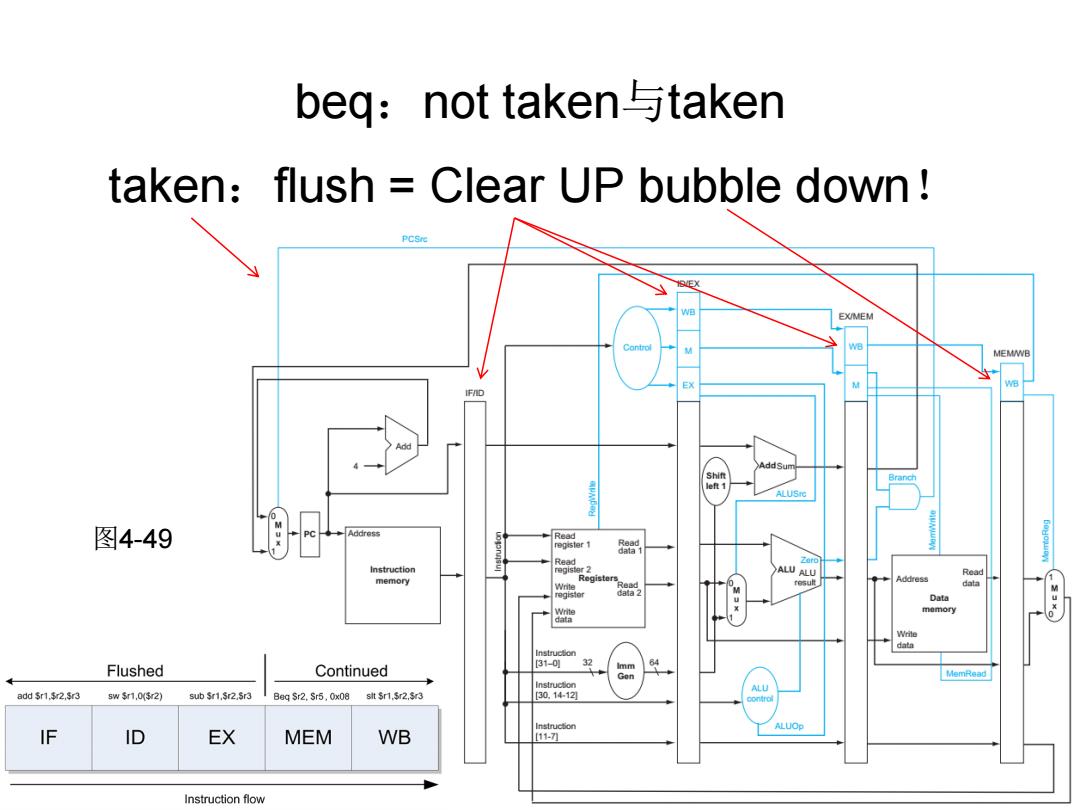

beq:not taken与taken taken:flush Clear UP bubble down PCSre EX/MEM Control MEMMB EX IFAD Shin Branch left 1 ALUSre 图4-49 Address Instruction ALU ALU Read memory Reaister Address Write result data u Data memory Write data Instruction 31-0 32 Flushed Continued 64 MemRead ALU add $r1.$r2,$r3 sw Sr1,0($r2) sub $r1,$r2.Sr3 Beg Sr2,Sr5,0x08 sit Sr1,$r2,Sr3 D141 Instruction ALUOp IF ID EX MEM WB 111-7刀 Instruction flow

6 beq:not taken与taken 图4-49 taken:flush = Clear UP bubble down!