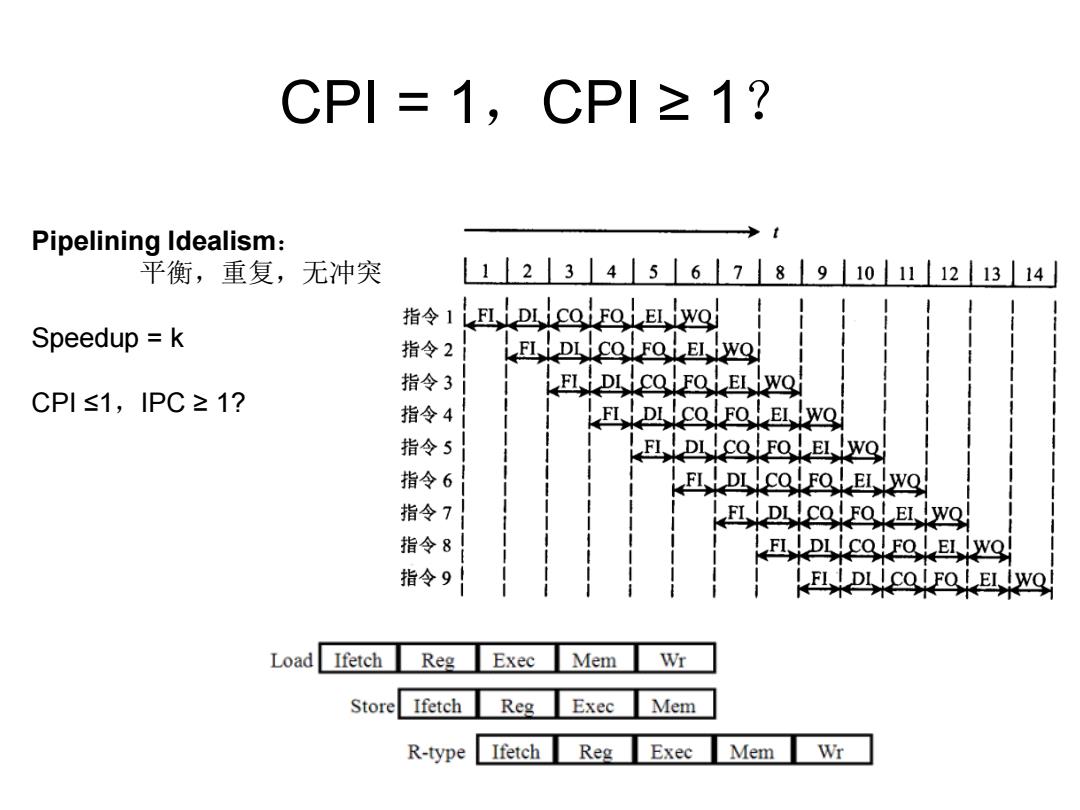

CP1=1,CPI≥1? Pipelining Idealism: 平衡,重复,无冲突 L1⊥23456⊥7891011⊥121314 指令1,pool,lwo Speedup =k 指令2 FL L DL ICOLFO LELWO 指令3 FLDL ICO FOLEL WO CPI≤1,IPC≥1? 指令4 FLDLCOFO卧hw9 指令5 FL DL CO FOL EL WO 指令6 FL DI ICO FO EL WO 指令7 4PL9404巴w9 指令8 1P449404马y9 指令9 Load Ifetch Reg Exec Mem Wr Store Ifetch Reg Exec Mem R-type Ifetch Reg Exec Mem Wr

CPI = 1,CPI ≥ 1? Pipelining Idealism: 平衡,重复,无冲突 Speedup = k CPI ≤1,IPC ≥ 1?

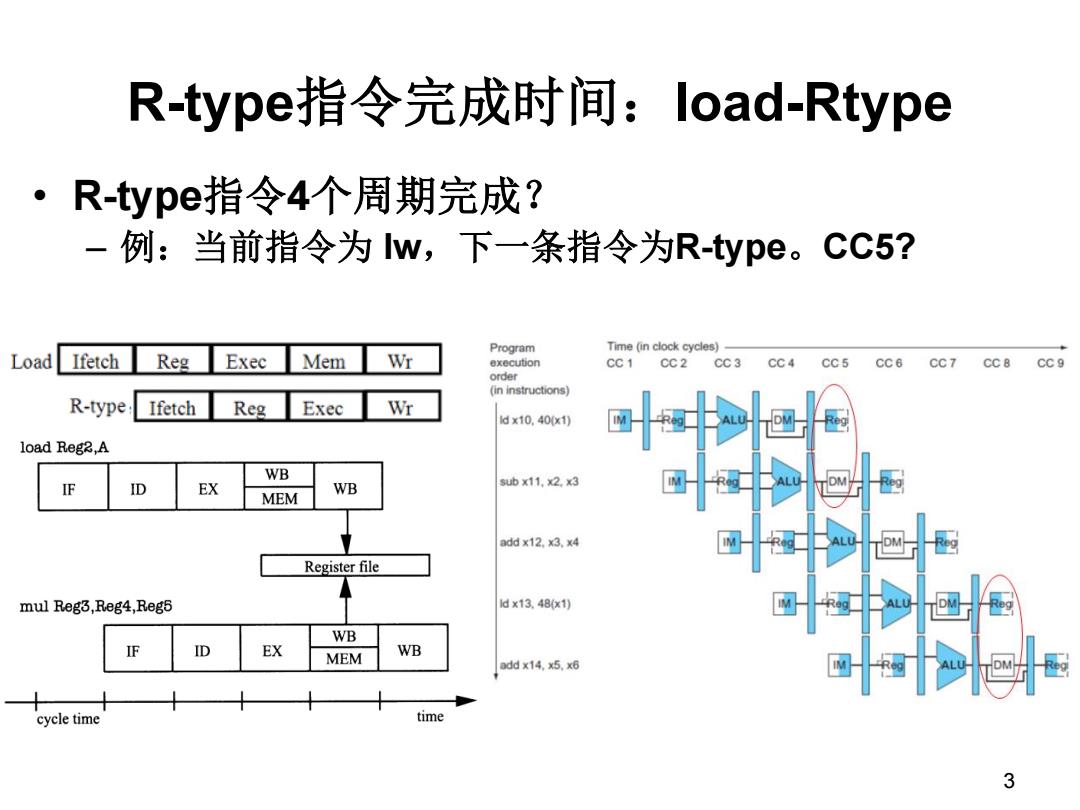

R-type指令完成时间:load-Rtype R-type指令4个周期完成? -例:当前指令为w,下一条指令为R-type。( CC5? Program Time (in clock cycles)- Load Ifetch Reg Exec Mem Wr execution CC1 CC2 CC3 CC4 CC5 CC6 CC7 CC8 CC9 order (in instructions) R-type Ifetch Reg Exec W dx10,400x1) load Reg2,A WB F ID EX WB sub x11.x2.x3 MEM add x12.x3.x4 Register file mul Reg3,Reg4,Reg5 1dx13.48(x1) WB F ID EX MEM WB add x14,x5.x6 cycle time time 3

3 R-type指令完成时间:load-Rtype • R-type指令4个周期完成? – 例:当前指令为 lw,下一条指令为R-type。CC5?

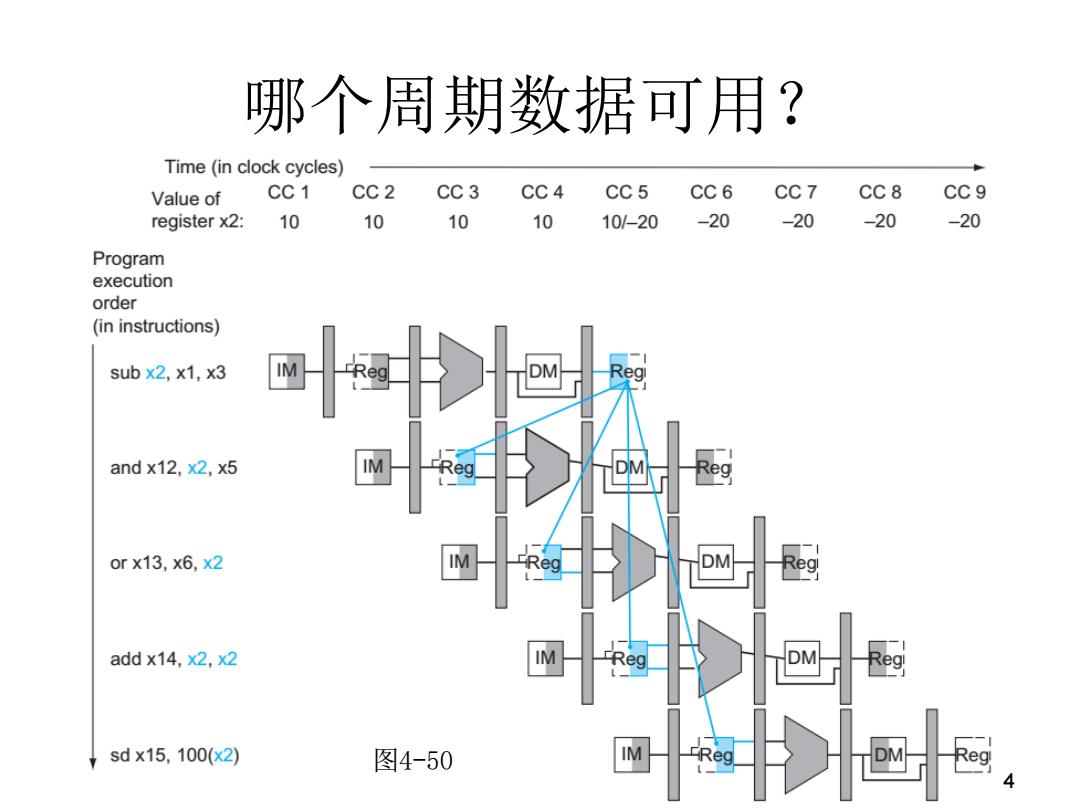

哪个周期数据可用? Time(in clock cycles) Value of CC1 CC2 CC3 CC4 CC5 CC6 CC7 CC8 CC 9 register x2: 10 10 10 10 10/-20 -20 -20 -20 -20 Program execution order (in instructions) sub x2,x1,x3 and x12,x2,x5 or x13,x6,x2 add x14,x2,x2 sd×15,100(x2) 图4-50 Reg eg

4 哪个周期数据可用? 图4-50

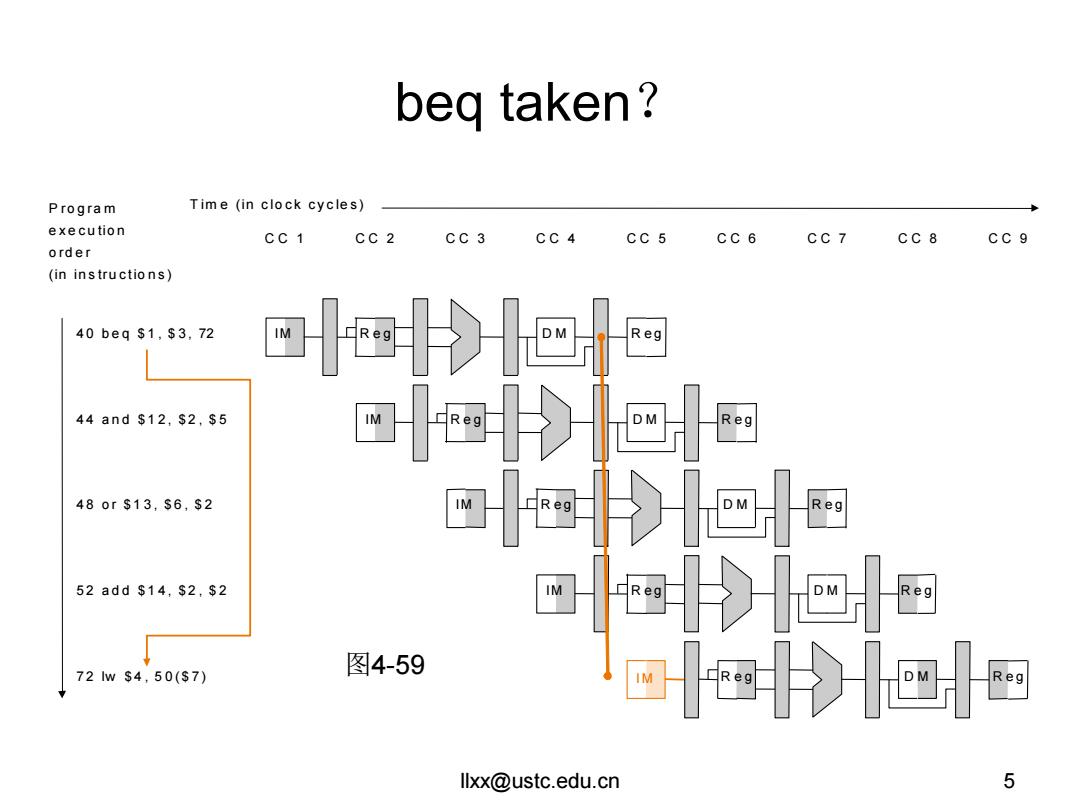

beq taken? Program Time (in clock cycles) execution CC 1 CC2 CC3 CC 5 C C6 CC 7 CC 8 CC9 order (in instructions) 40beq$1,$3,72 Reg 44and$12,$2,$5 Reg Reg 480r$13,s6,$2 IM eg DM Reg 52add$14,s2,$2 IM Reg Reg 72lw$4,50(s7) 图4-59 Reg llxx@ustc.edu.cn 5

llxx@ustc.edu.cn 5 beq taken? R e g R e g C C 1 T im e (in c lo c k c y c le s ) 4 0 b e q $ 1 , $ 3 , 72 P ro g ra m e x e c u tio n o rd e r (in in s tru c tio n s ) IM R e g IM D M IM D M IM D M D M D M R e g R e g R e g R e g R e g IM R e g 4 4 a n d $ 1 2 , $ 2 , $ 5 4 8 o r $ 1 3 , $ 6 , $ 2 5 2 a d d $ 1 4 , $ 2 , $ 2 7 2 lw $ 4 , 5 0 ($ 7 ) C C 2 C C 3 C C 4 C C 5 C C 6 C C 7 C C 8 C C 9 R e g 图4-59

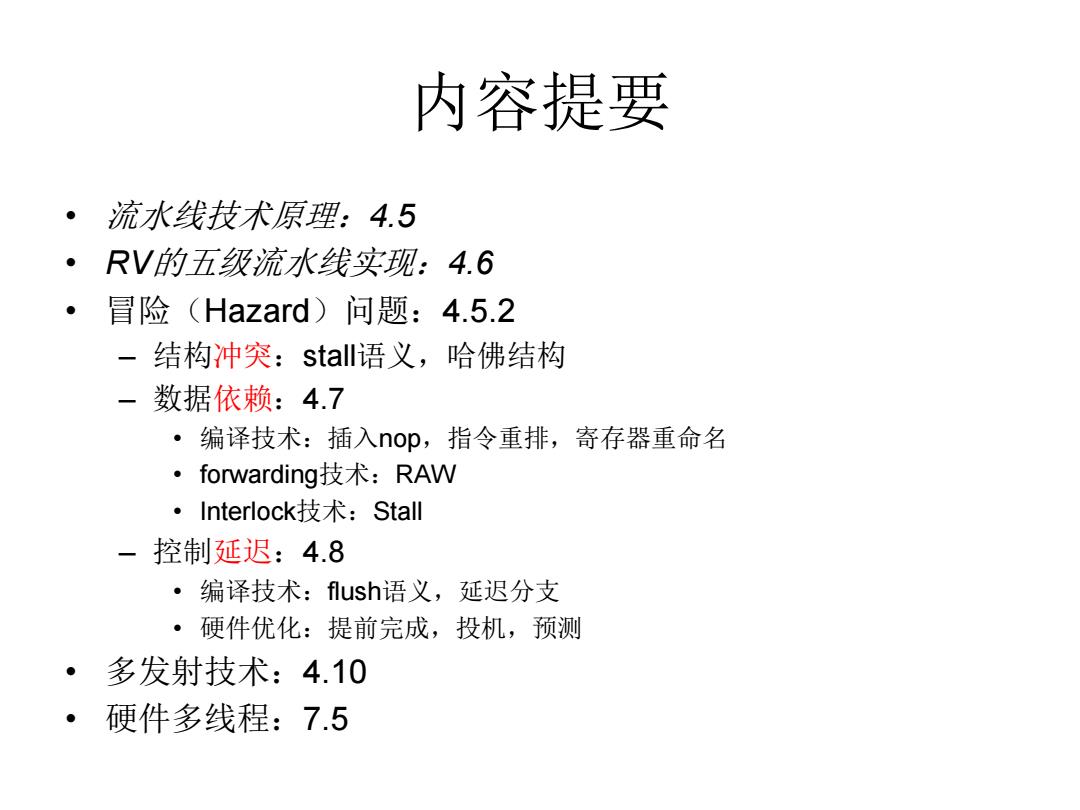

内容提要 ·流水线技术原理:4.5 。 RV的五级流水线实现:4.6 ● 冒险(Hazard)问题:4.5.2 -结构冲突:stall语义,哈佛结构 -数据依赖:4.7 ·编译技术:插入nop,指令重排,寄存器重命名 ·forwarding技术:RAW ·Interlock技术:Stall -控制延迟:4.8 ·编译技术:fush语义,延迟分支 ·硬件优化:提前完成,投机,预测 。多发射技术:4.10 ·硬件多线程:7.5

内容提要 • 流水线技术原理:4.5 • RV的五级流水线实现:4.6 • 冒险(Hazard)问题:4.5.2 – 结构冲突:stall语义,哈佛结构 – 数据依赖:4.7 • 编译技术:插入nop,指令重排,寄存器重命名 • forwarding技术:RAW • Interlock技术:Stall – 控制延迟:4.8 • 编译技术:flush语义,延迟分支 • 硬件优化:提前完成,投机,预测 • 多发射技术:4.10 • 硬件多线程:7.5