第五章时序逻辑电路 波形图 S R R S 3.特性表和特性方程 4.基本RS触发器主要特 RS n+1 点 保持 1.优点:结构简单, 0 1 置1 具有置0、置1、保持功能 1 0 置0 11 不用 不许 2.问题:输入电平直接控制输 m+1=S+R 出状态,使用不便,抗干扰能 RS=0约束条件 力差;R、S之间有约束

第五章 时序逻辑电路 S R Q Q 3. 特性表和特性方程 R S Q n+1 0 0 0 1 1 0 1 1 Q n 保持 置 1 置 0 不许 1 0 不用 Q n+1 = S + RQ n RS = 0 约束条件 4.基本 RS 触发器主要特 点 1. 优点:结构简单, 具有置 0、置 1、保持功能。 2. 问题:输入电平直接控制输 出状态,使用不便,抗干扰能 力差;R、S 之间有约束。 G2 Q G1 R S Q >1 >1 波 形 图

第五章时序逻辑电路 五.集成基本触发器 1.CMOS集成基本触发器 1).由与非门组成:CC4044 +Vcc 6 EN? 1Q TG 74279 EN K55R5R58 74LS279 3Q EN 4S ENo EN 内含4个基本RS触发器 2).由或非门组成:CC4043(略)

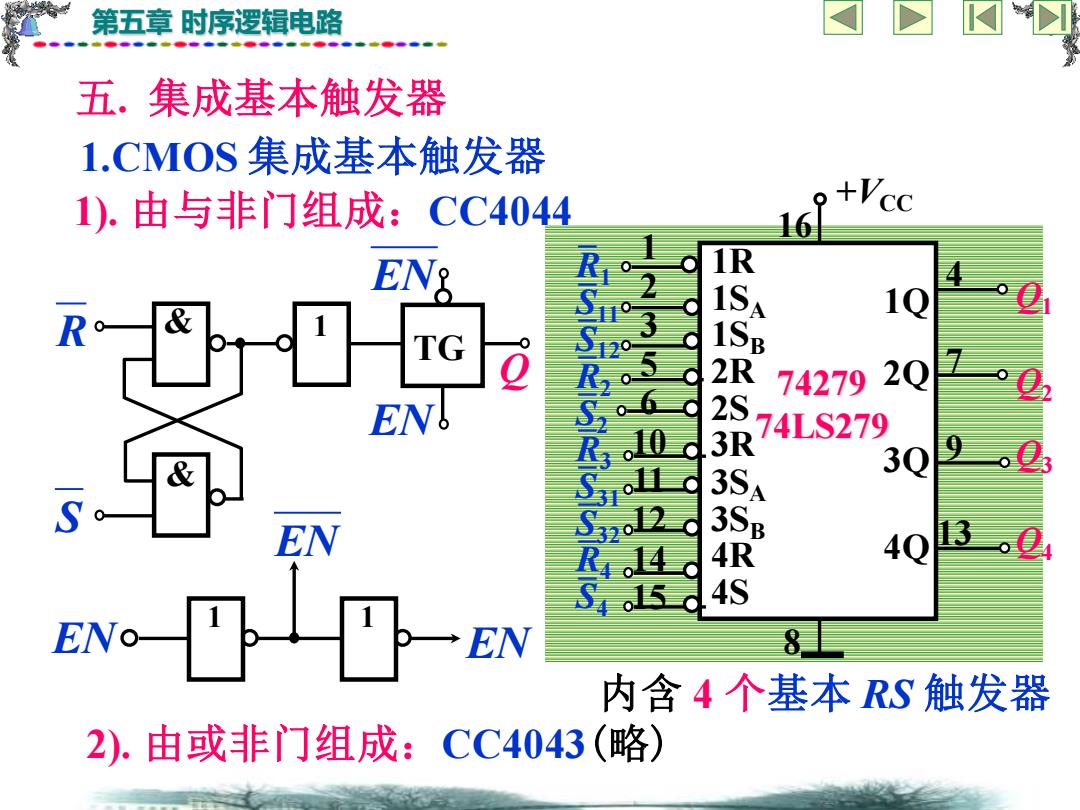

第五章 时序逻辑电路 五. 集成基本触发器 1.CMOS 集成基本触发器 1). 由与非门组成:CC4044 & & 1 R TG S ENEN Q 1 1 EN EN EN 三态 RS 锁存触发器特性表 R S EN Q n+1 注 0 Z 高阻态 0 0 1 0 1 1 1 0 1 1 1 1 Q n 保 持 置 1 置 0 不允许 1 0 不用 内含 4 个基本 RS 触发器 2). 由或非门组成:CC4043(略) +VCC 1R 1SA 1SB 2R 2S 3R 3SA 3SB 4R 4S 1Q 2Q 3Q 4Q 1 2 3 5 6 10 11 12 14 15 4 7 9 13 Q1 Q2 Q3 Q4 8 16 74279 74LS279 R1 S11 S12 R2 S2 R3 S31 S32 R4 S4 – – – – – – – – – –

第五章时序逻辑电路 2.TTL集成基本触发器 74279、74LS279 +Vcc 16 R 1Q 74279 2Q 22 R 74LS279 3Q 9 23 & 403 c 8 S1 S2

第五章 时序逻辑电路 2.TTL 集成基本触发器 74279、74LS279 Q R & & S Q R & & S1 S2 +VCC 1R 1SA 1SB 2R 2S 3R 3SA 3SB 4R 4S 1Q 2Q 3Q 4Q 1 2 3 5 6 10 11 12 14 15 4 7 9 13 Q1 Q2 Q3 Q4 8 16 74279 74LS279 R1 S11 S12 R2 S2 R3 S31 S32 R4 S4 – – – – – – – – – –

第五章时序逻辑电路 5.2.2钟控触发器 5.2.2.1同步RS触发器 同步触发器:触发器的工作状态不仅受输入端(R、S) 控制,而且还受时钟脉冲(CP)的控制。 CP(Clock Pulse):等周期、等幅的脉冲串。 基本RS触发器:S一直接置位端; (不受CP控制) R一直接复位端。 同步触发器: 同步RS触发器 同步D触发器

第五章 时序逻辑电路 同步触发器:触发器的工作状态不仅受输入端 (R、S) 控制,而且还受时钟脉冲(CP) 的控制。 CP (Clock Pulse): 等周期、等幅的脉冲串。 基本 RS 触发器:S — 直接置位端; R — 直接复位端。 (不受 CP 控制) 同步触发器: 同步 RS 触发器 同步 D 触发器 5.2.2 钟控触发器 5.2.2.1 同步 RS 触发器

第五章时序逻辑电路 一、电路组成及工作原理 1.电路及逻辑符号 & SCPR SC1R R & S CP R S CP R R 曾用符号 国标符号 2.工作原理 当CP=0S=R=1 2+1=Q” 保持 当CP=1SCP=S.1=S RCP=R.1-R 与基本RS触发器功能相同

第五章 时序逻辑电路 一、电路组成及工作原理 1. 电路及逻辑符号 Q G1 R & & S Q G3 R & & S G2 G4 CP 曾用符号 Q Q S R S CP R CP 国标符号 Q Q S R S CP R C1 2. 工作原理 当 CP = 0 S = R = 1 n n Q = Q +1 保持 当 CP = 1 S CP = S 1 = S 与基本 RS 触发器功能相同 RCP = R1 = R