5.5可编程逻辑器件和时序逻辑电路 的VHDL及其仿真 5.5.1可编程逻辑器件(PLD) (Programmable Logic Device) 一、 PLD的基本结构和分类 1.基本结构 输 输 输入项 积项 武 或项 电 阵 阵 输出电 出 列 A PLD的输入缓冲电路

5.5.1 可编程逻辑器件 (PLD) (Programmable Logic Device) 一、PLD的基本结构和分类 1. 基本结构 输 入 电 路 与 门 阵 列 或 门 阵 列 输 出 电 路 • • • • • • 输 入 输入项 积项 或项 输 出 1 A A A A A A PLD的输入缓冲电路 5.5 可编程逻辑器件和时序逻辑电路 的VHDL及其仿真

✉D冈I 2.分类 ()按可编程情况分 分类 与阵列 或阵列 输出电路 出现年代 PROM 固定 可编程 固定 70年代初 PLA 可编程 可编程 固定 70年代中 PAL 可编程 固定 固定 70年代末 GAL 可编程 固定 可组态 80年代初

2. 分类 (1) 按可编程情况分 分 类 与阵列 或阵列 输出电路 出现年代 PROM 固定 可编程 固定 70年代初 PLA 可编程 可编程 固定 70年代中 PAL 可编程 固定 固定 70年代末 GAL 可编程 固定 可组态 80年代初

PROM 可编程只读存储器 (Programmable Read Only Memory) 2110 或阵列 可编程) 缺点: ·只能实现标准 与或式 ·芯片面积大 ·利用率低,不经济 用途: ·存储器 ·函数表 与阵列 显示译码电路 (固定)

● PROM — 可编程只读存储器 I2 I1 I0 O2 O1 O 0 与阵列 (固定) 或阵列 (可编程) 缺点: • 只能实现标准 与或式 • 芯片面积大 • 利用率低,不经济 用途: • 存储器 • 函数表 • 显示译码电路 (Programmable Read Only Memory)

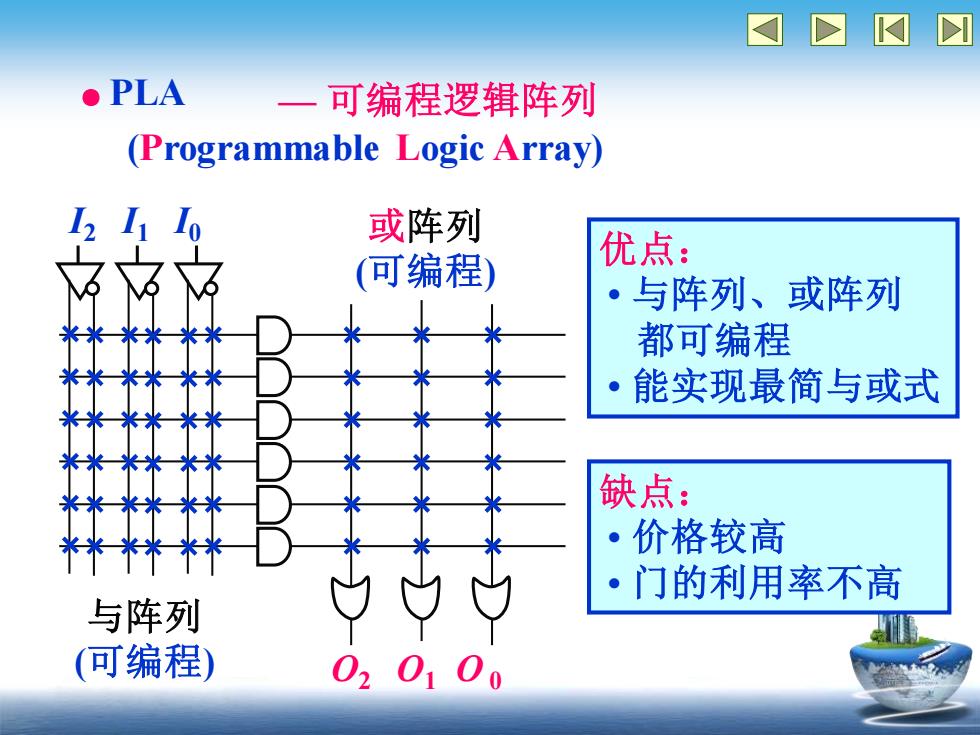

●PLA 可编程逻辑阵列 (Programmable Logic Array) 或阵列 (可编程) 优点: ·与阵列、或阵列 米米 都可编程 能实现最简与或式 缺点: 。 价格较高 ·门的利用率不高 与阵列 (可编程) 020100

● PLA — 可编程逻辑阵列 I2 I1 I0 O2 O1 O 0 与阵列 (可编程) 或阵列 (可编程) 优点: • 与阵列、或阵列 都可编程 • 能实现最简与或式 缺点: • 价格较高 • 门的利用率不高 (Programmable Logic Array)

●PAL - 可编程阵列逻辑 (Programmable Array Logic) 2I10 或阵列 优点: (固定) ·速度高 米米米米米 ·价格低 ·采用编程器现场 编程 缺点: •输出方式固定 与阵列 一次编程 (可编程) 020100

● PAL — 可编程阵列逻辑 I2 I1 I0 O2 O1 O 0 与阵列 (可编程) 或阵列 (固定) 优点: • 速度高 • 价格低 • 采用编程器现场 编程 缺点: • 输出方式固定 一次编程 (Programmable Array Logic)