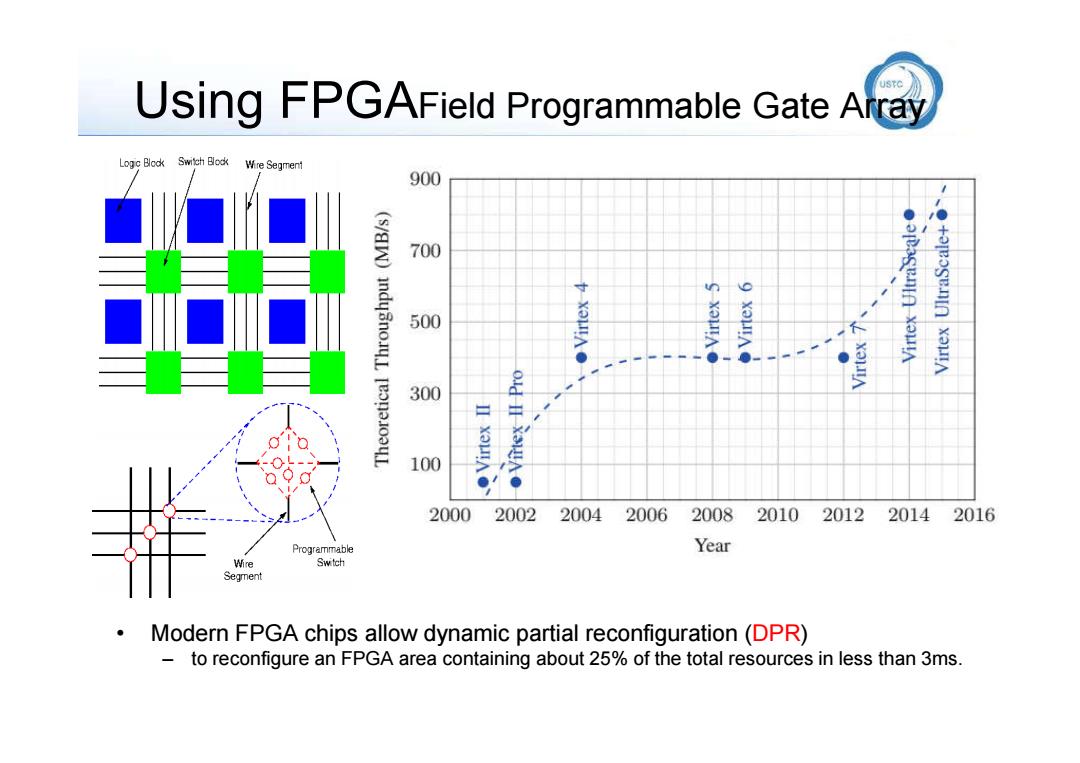

Using FPGAField Programmable Gate Array Logc Bleck Switch Block Wire Segment 900 700 (s/gW)indy3noyL [eonaoayL 500 300 100 2000 2002 2004 2006 2008 2010 201220142016 Programmable Year Wire Switch Segment 。 Modern FPGA chips allow dynamic partial reconfiguration(DPR) to reconfigure an FPGA area containing about 25%of the total resources in less than 3ms

Using FPGAField Programmable Gate Array • Modern FPGA chips allow dynamic partial reconfiguration (DPR) – to reconfigure an FPGA area containing about 25% of the total resources in less than 3ms

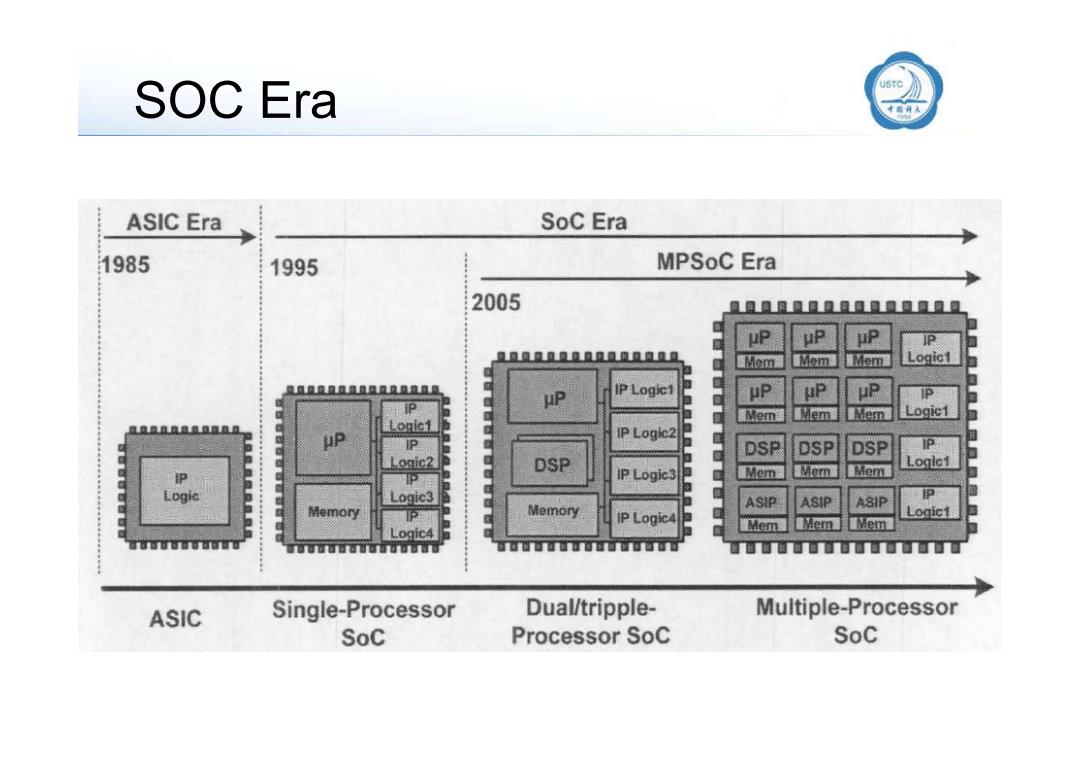

SOC Era ASIC Era SoC Era 1985 1995 MPSoC Era 2005 且R具且■员且员具原级且且夏 Mem aMnAnnmnnnnnnnn P Mem Mem Logic1 息an且n且直狼LLA Logict IP Logic2 P DSP DSP DSP DSP P IP Logic3 Mem Mern Mem Logic Logic3 ASIP Memory Memory ASIP IP Logic4 Logic1 Logic4 Mem ASIC Single-Processor Dual/tripple- Multiple-Processor SoC Processor SoC SoC

SOC Era

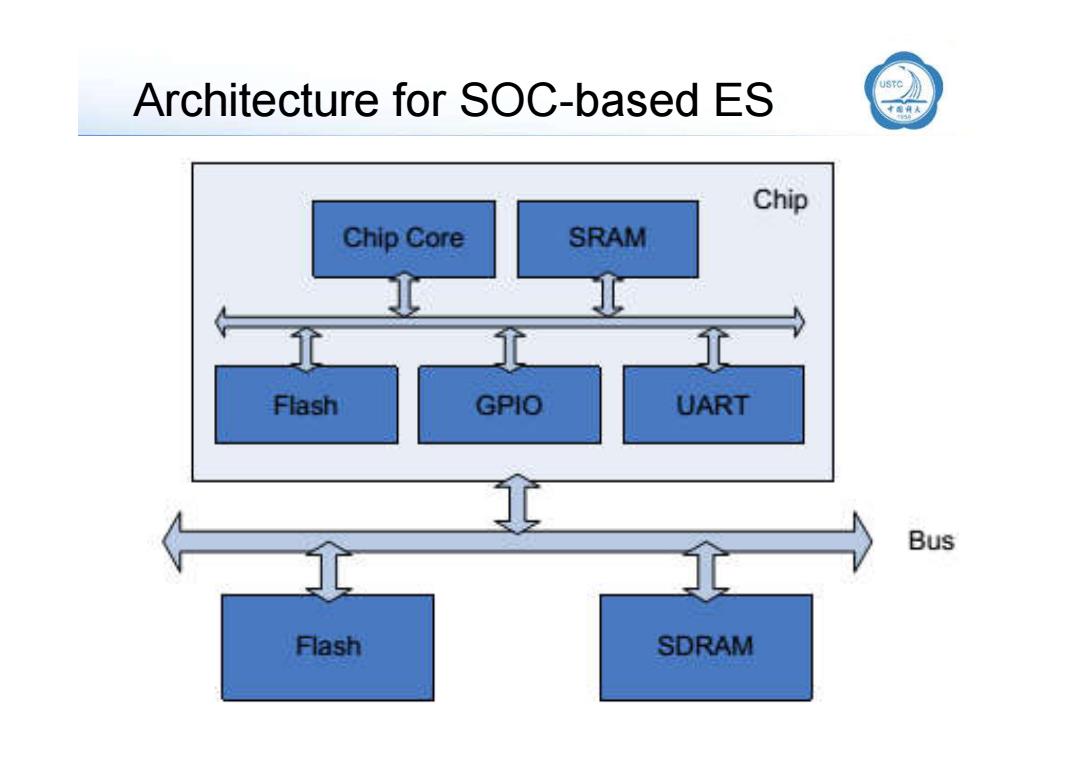

Architecture for SOC-based ES Chip Chip Core SRAM 0 Flash GPIO UART Bus Flash SDRAM

Architecture for SOC-based ES

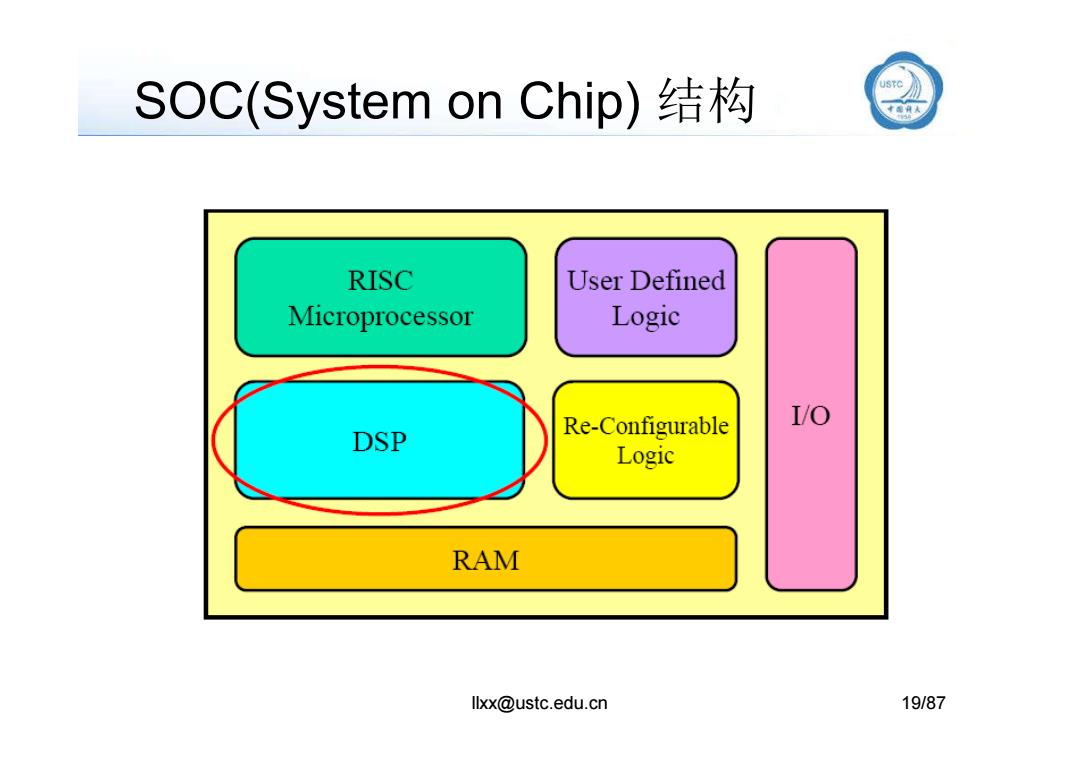

SOC(System on Chip)结构 RISC User Defined Microprocessor Logic Re-Configurable I/O DSP Logic RAM llxx@ustc.edu.cn 19/87

SOC(System on Chip) 结构 llxx@ustc.edu.cn 19/87

DSP v.s.DSP ! o Digital Signal Processing Mathematical manipulation of digitally represented signals Digital Signal Processor Microprocessors designed to perform Digital Signal Processing Real-time performance Short time-to-market Upgradable solutions Move Hardware Design (ASIC)to Software Design (Programming) Offer the key to SOC integration llxx@ustc.edu.cn 20/87

DSP v.s. DSP !? • Digital Signal Processing – Mathematical manipulation of digitally represented signals • Digital Signal Processor – Microprocessors designed to perform Digital Signal Processing llxx@ustc.edu.cn 20/87 • Real-time performance • Short time-to-market • Upgradable solutions – Move Hardware Design (ASIC) to Software Design (Programming) – Offer the key to SOC integration