y(n)=x(Mn) n三-00~00 M=3 y(0)=x(0) y1①=x(3) y(2)=x(6 y(3)=x(9) 舍弃了(M-1)M部分的数据

y(n) x(Mn) n ~ M 3 y(0) x(0) y(1) x(3) y(2) x(6) y(3) x(9) 舍弃了(M-1)/M部分的数据 . . .

抽取的实现 抽取的实现 ()串行数据抽取的实现 (2)并行数据抽取的实现 -非均匀抽取产生的原因 一均匀抽取的实现

抽取的实现 抽取的实现 ⑴串行数据抽取的实现 ⑵并行数据抽取的实现 -非均匀抽取产生的原因 -均匀抽取的实现

串行数据抽取的实现 采用控制FIFO写使能的方式进行抽点 ADC 输出数据 ①X2X3X4X⑤X6X⑦X8X9X0X2X3X4X151617X18 FIFO 写使能 FIFO 实际存储 1 10 13 16 数据

串行数据抽取的实现 采用控制FIFO写使能的方式进行抽点 ADC 输出数据 FIFO 写使能 FIFO 实际存储 数据 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 ... 1 4 7 10 13 16

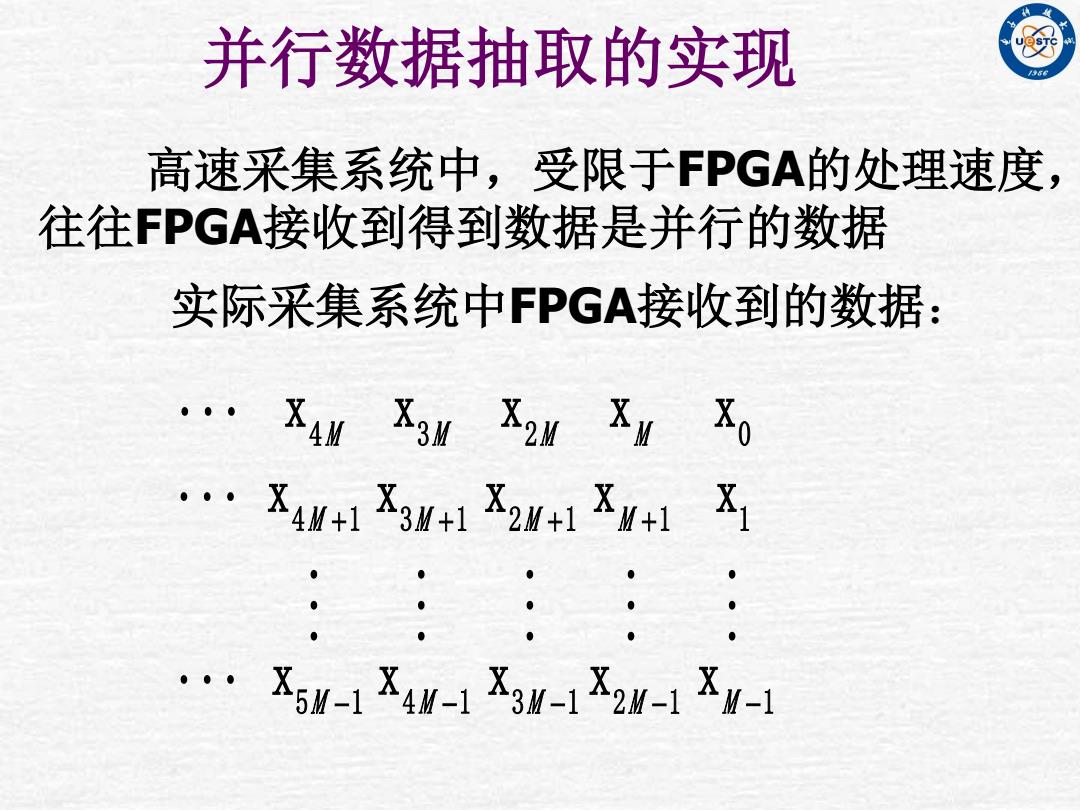

并行数据抽取的实现 高速采集系统中,受限于FPGA的处理速度, 往往FPGA接收到得到数据是并行的数据 实际采集系统中FPGA接收到的数据: X2M Xo ·X4W+1X3M+1X2M+1XM+181 ·: : -1X4M-1X3M-1X2M-1XM-1

高速采集系统中,受限于FPGA的处理速度, 往往FPGA接收到得到数据是并行的数据 实际采集系统中FPGA接收到的数据: 0 x x 2 M x 3 M x 4 M x M ... 1 x 1 x 2 1 M x 3 1 M x 4 1 M x M ... ... ... ... ... ... 1 x 2 1 M x 3 1 M x 4 1 M x 5 1 M x M ... 并行数据抽取的实现

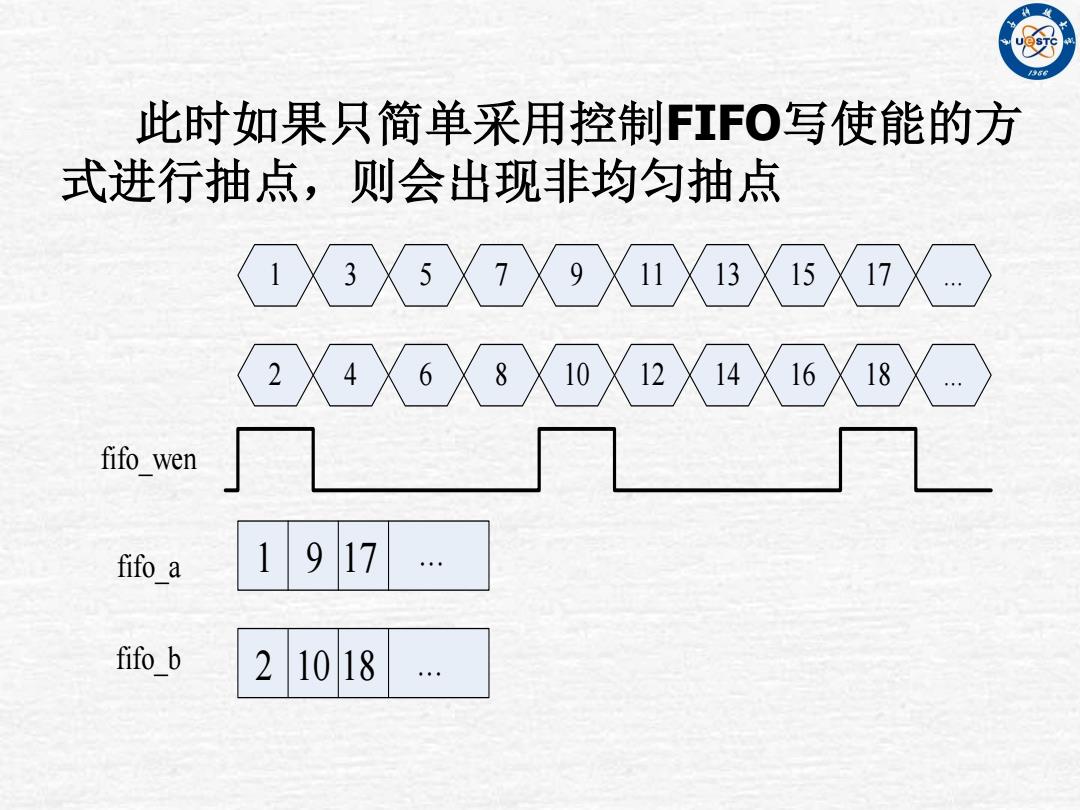

此时如果只简单采用控制FIFO写使能的方 式进行抽点,则会出现非均匀抽点 ①X3X5X⑦X9 XHB 17 2X4 8 10 12 14 16 18 fifo wen fifo a 1917 fifo b 21018

此时如果只简单采用控制FIFO写使能的方 式进行抽点,则会出现非均匀抽点 1 3 5 7 9 11 13 15 2 4 6 8 10 12 14 16 1 9 2 10 17 18 ... ... 17 18 ... ... fifo_wen fifo_a fifo_b