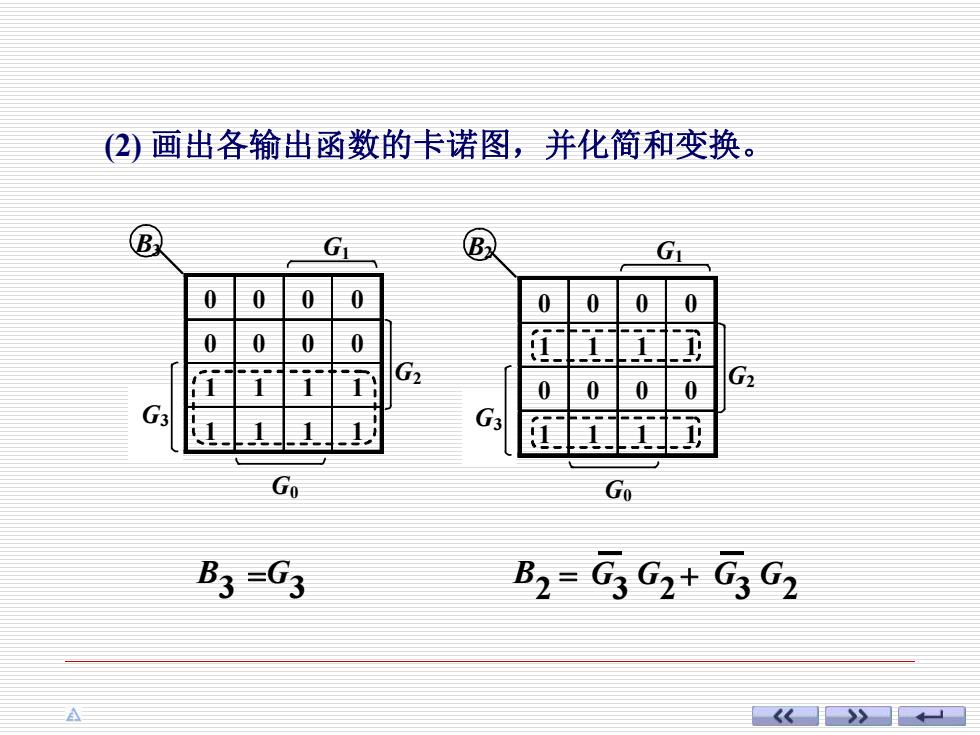

2)画出各输出函数的卡诺图,并化简和变换。 G ⑧ 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 G3 Go Go B3=G3 B2=G3 G2+G3 G2

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B3 G0 G2 G3 G1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B2 G0 G2 G3 G1 (2) 画出各输出函数的卡诺图,并化简和变换。 3 3 B G 2 B 2 G3 G 2 G3 G

⑧ ⑧ 0 0 0 1 0 0 0 0 0 0 0 G2 0 0 G G3 0 0 G3 0 0 B Go B1-G3G2G1+G3G2G1+G3G2G1+G3G2G1 (G,02+GGG1+G02+G3G,G1 = G3⊕G2⊕G B0=G9G2⊕G1⊕G0 《□》☐☐

G3 G2 1 B 1 G 2 G3 G 1 G 2 G3 G 1 G 2 G3 G 1 G ( 2 G3 G ) 2 G3 G 1 G 2 G3 G ) 2 G3 G 1 G 3 G 2 G 1 G 0 B 3 G 2 G 1 G 0 G 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 B1 B0 G2 G3 G1 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 B0 G0 G2 G3 G1

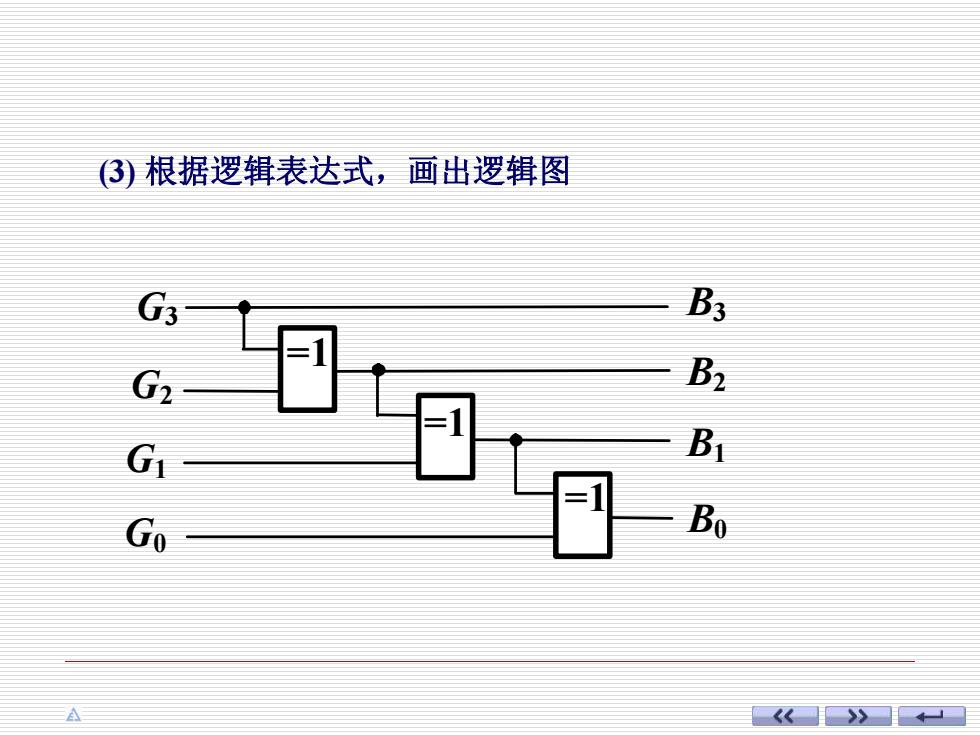

3)根据逻辑表达式,画出逻辑图 G666 =1 五五B5

(3) 根据逻辑表达式,画出逻辑图 =1 B0 B1 B2 B3 G0 G1 G2 G3 =1 =1

©庭人是 43组合逻辑电路中的竞争冒险 43.1产生的竞争冒险的原 因 43.2消去竞争冒险的方法 《☐》☐☐

4.3 组合逻辑电路中的竞争冒险 4.3.1 产生的竞争冒险的原 因 4.3.2 消去竞争冒险的方法

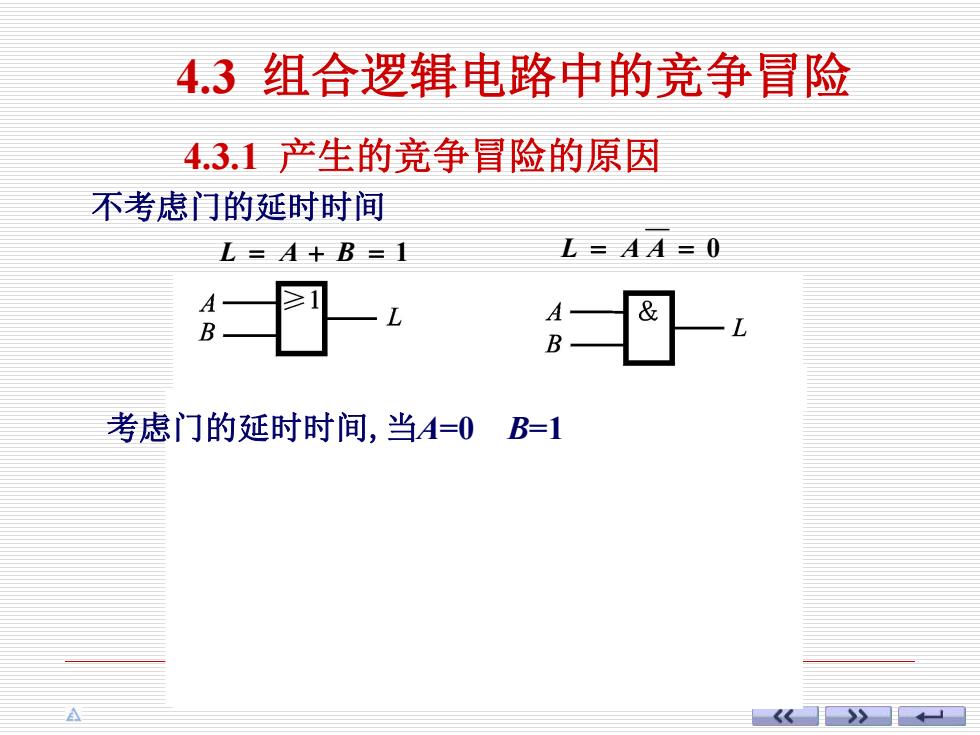

43组合逻辑电路中的竞争冒险 4.31产生的竞争冒险的原因 不考虑门的延时时间 =A+B=1 L=AA=0 -D & 考虑门的延时时间,当A=0B=1

4.3 组合逻辑电路中的竞争冒险 不考虑门的延时时间 考虑门的延时时间,当A=0 B=1 L A B 1 L A A 0 4.3.1 产生的竞争冒险的原因