第六章 时序墅辑电路 二、双4位锁存器(门4116① Latch 一)引脚排列图和逻辑功能示意图 6c202D,202D22012D12002D.2LE2LL2CR 9.Q.Q,四数码并僧输出 24 23 2221 16 15 1413 送数 控制正Ro 之74116 CR 异步清零 9 10 1112 CR ILEAILER1D0 1001D11Q1D2 IO2 1Ds 10 二)逻辑功能 清零 CR=0 03020120=0000 送数 CR=1 LEA+LEB=0 00000=43ll1d0 保持 CR=1 LEA+LEB =1 Q0010不变

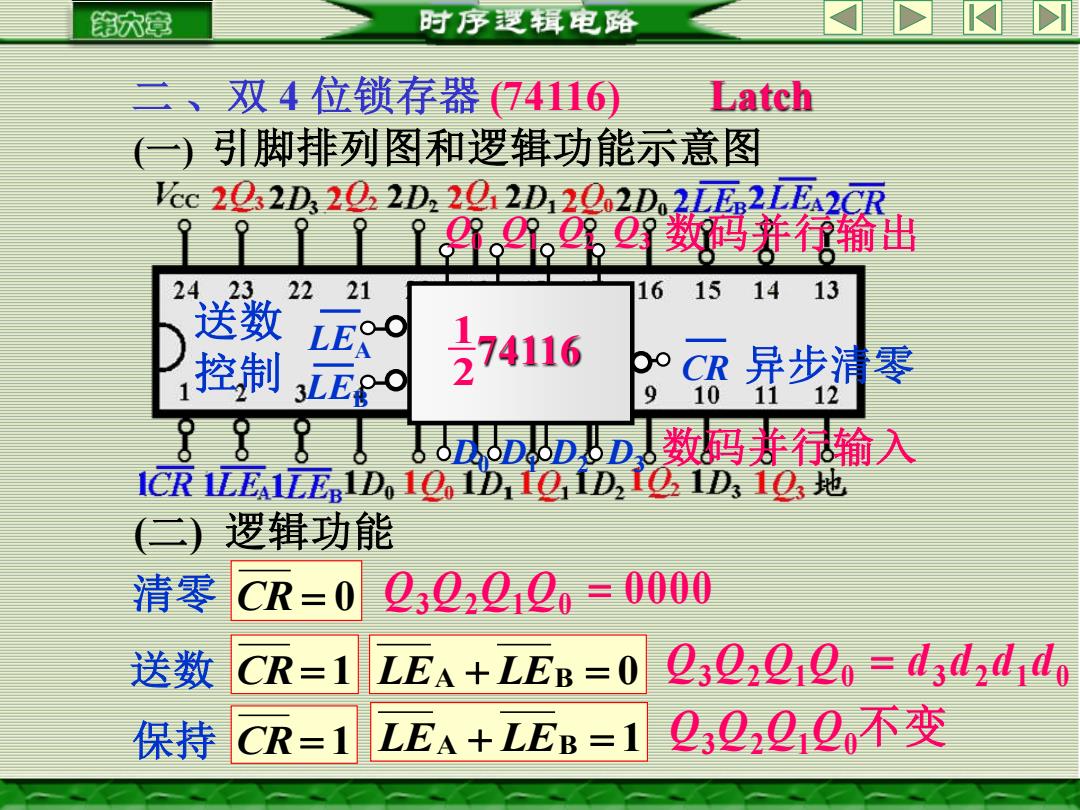

二 、双 4 位锁存器 (74116) Latch (一) 引脚排列图和逻辑功能示意图 74116 Q0 Q1 Q2 Q3 CR LEA D0 D1 D2 D3 LEB 2 1 异步清零 送数 控制 数码并行输入 数码并行输出 (二) 逻辑功能 清零 CR = 0 送数 0000 Q3 Q2 Q1 Q0 = CR= 1 LEA + LEB = 0 3 2 1 0 3 2 1 0 Q Q Q Q = d d d d 保持 CR= 1 LEA + LEB = 1 Q3 Q2 Q1 Q0 不 变

第六章 时序逻辑电路 三、4×4寄存器阵列(门470、74LS170) ()脚排列图和逻辑功能示意图 数码输山 06010210 16151413 121110 9 74170 74170 RO 23 45 6 78 ENR D1D,D3ARo凸2地 Do DI D2 D3 并行数码输入 Awo.Aw 地址码输入端 ENw 读写使能端 ARO.ARI ENR

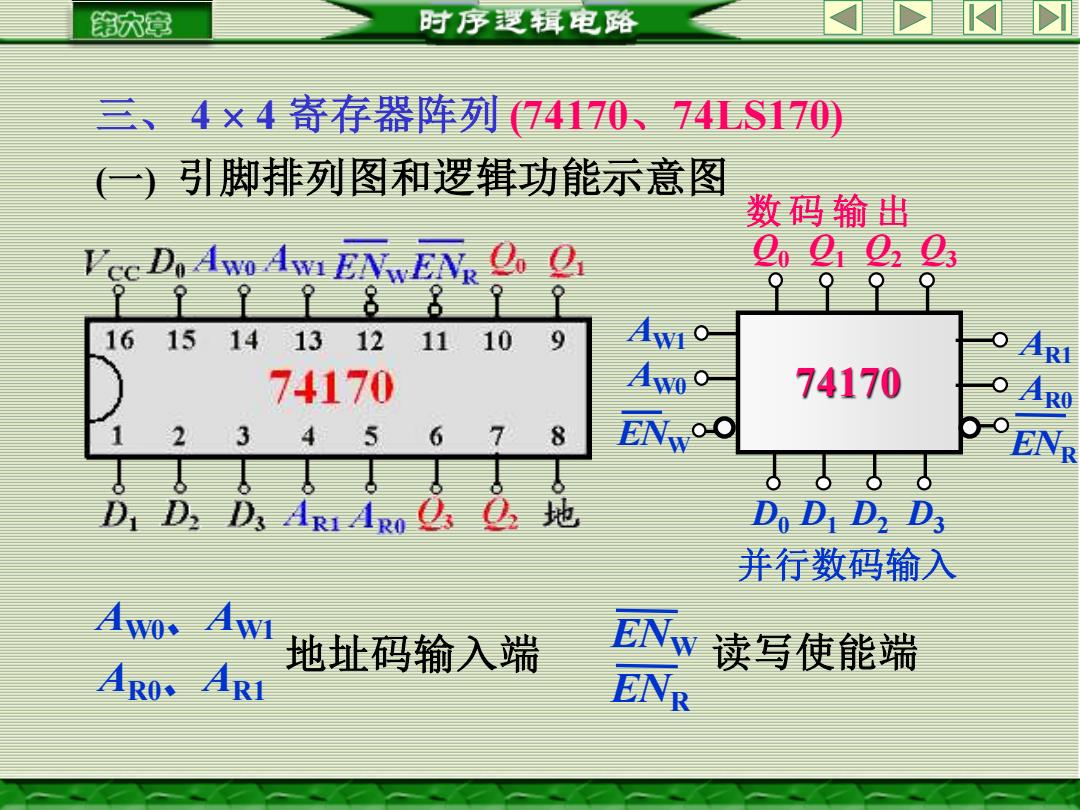

三、 4 4 寄存器阵列 (74170、74LS170) (一) 引脚排列图和逻辑功能示意图 74170 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 并行数码输入 数 码 输 出 AW0、AW1 AR0、AR1 地址码输入端 ENW ENR 读写使能端

第六章 时序遐辑电路 (二)逻辑功能 能存熾存器:W构成东储想阵W3 0 0 1 Aw 0 0 1 0 ARI × Awo × 1 0 E不w ENR 1 0 0 0 Do 特点:读写独立,可同时进行;集电极开路输出

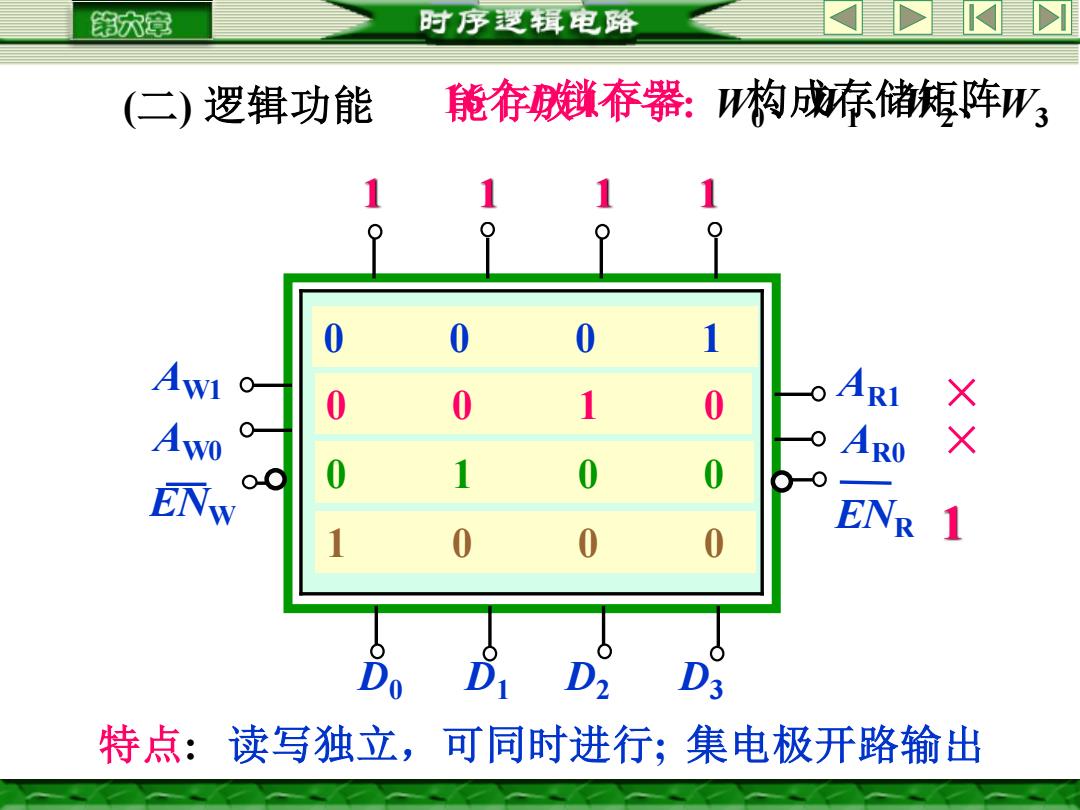

(二) 逻辑功能 16能存放个D锁存器 4个字: W构成存储矩阵 0、W1、W2、W3 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 FF00 FF01 FF02 FF03 FF10 FF11 FF12 FF13 FF20 FF21 FF22 FF23 FF30 FF31 FF32 FF33 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 1 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 0 1 0 0 0 1 × × 写 入 禁 止 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 × × 1 1 1 1 特点: 读写独立,可同时进行; 集电极开路输出

第六章 时序遐辑电路 633移位寄存器 、单向移位寄存器 (同一边沿触发器;同步时序电路) 右移寄存器 FFo 069 029 0 1D 1D C1 C1 C1 C1 时钟方程 CR=CP=CP=C卫3=CP 状态方程 Q1=D,Q1=Q6,Q1=Q,Q+1=Q 0

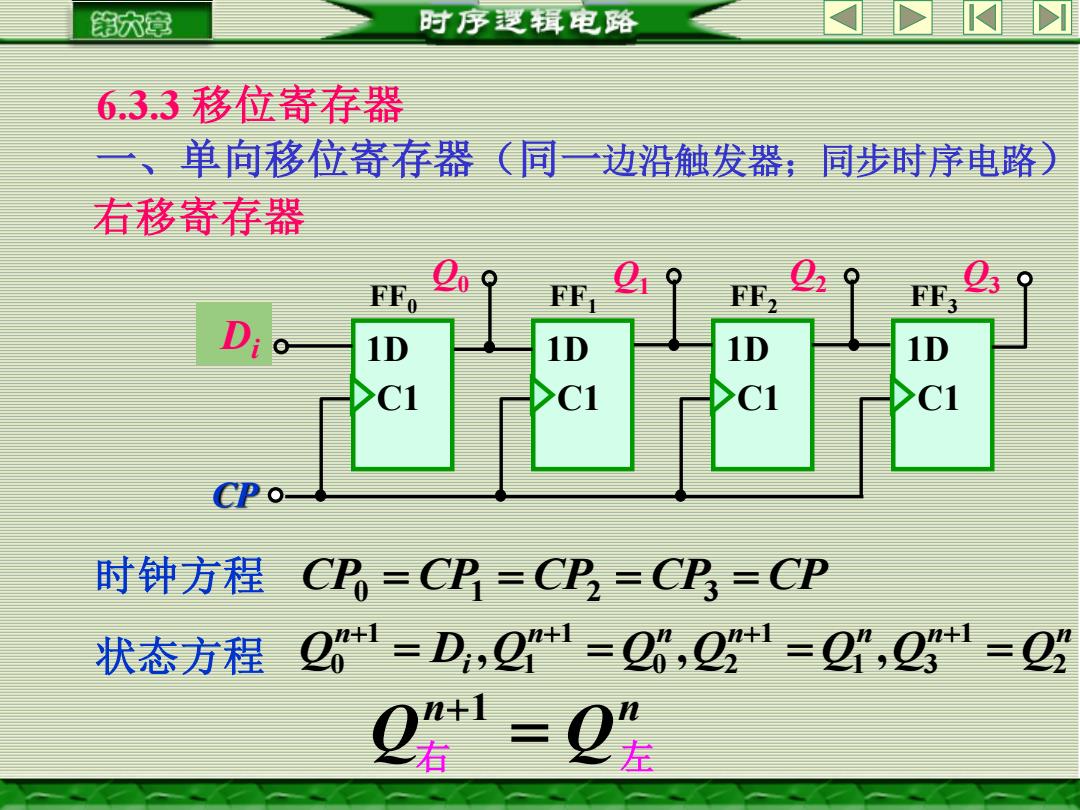

6.3.3 移位寄存器 一、单向移位寄存器(同一边沿触发器;同步时序电路) 右移寄存器 Q0 Q1 Q2 Q3 C1 1D FF0 CP C1 1D FF1 C1 1D FF2 C1 1D FF3 时钟方程 CP0 = CP1 = CP2 = CP3 = CP 状态方程 n n n n n n i n Q D Q Q Q Q Q Q2 1 1 3 1 0 2 1 1 1 0 = , = , = , = + + + + Di n n 1 Q Q + = 右 左