实训四组合逻辑电路 一、实训目的 1.掌握组合逻辑电路的设计与测试方法。 2.掌握半加器、全加器的工作原理。 二、实训电路 1.使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计组合电路的一般 步骤如图22-1所示。 设计要求 真值表 逻辑表达式 卡诺图 简化逻辑表达式 图4-1组合逻趣电路诊计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化 简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根据简化后的逻 辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实训来验证设计的正确性。 2.组合逻辑电路设计举例 用“与非门设计一个表决电路。当四个输入端中有三个或四个为“1时,输出端才为1”。 设计步骤:根据题意列出真值表如表4-1所示,再填入表4-2中。 表4-1 0 0 0 0 0 0 表4-2 DA 00 01 11 10 BC 00 01 1 11 1 1 1 10 1 由卡诺图得出逻辑表达式,并演化成“与非的形式 9

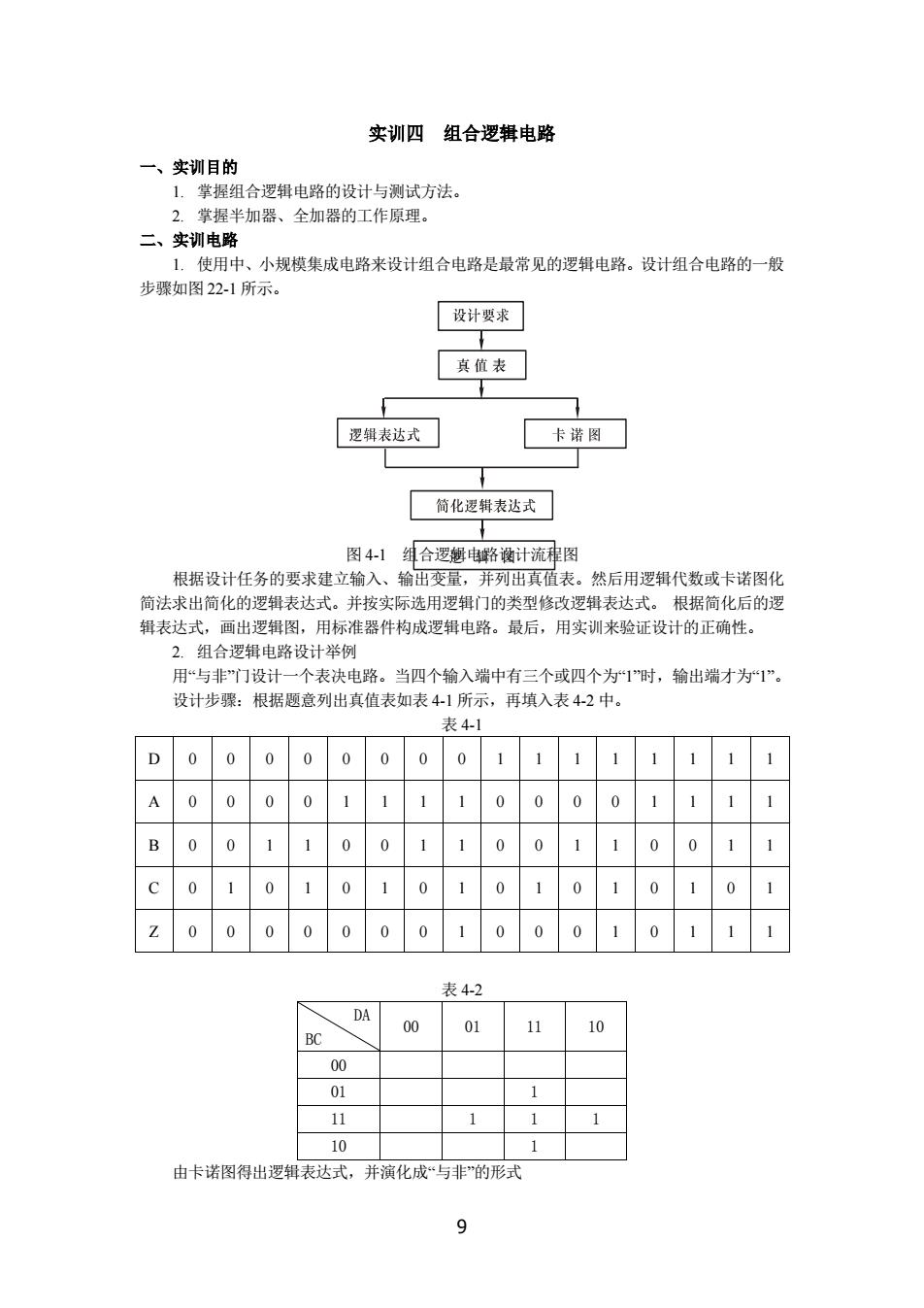

9 实训四 组合逻辑电路 一、实训目的 1. 掌握组合逻辑电路的设计与测试方法。 2. 掌握半加器、全加器的工作原理。 二、实训电路 1. 使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计组合电路的一般 步骤如图 22-1 所示。 图 4-1 组合逻辑电路设计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化 简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。 根据简化后的逻 辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实训来验证设计的正确性。 2. 组合逻辑电路设计举例 用“与非”门设计一个表决电路。当四个输入端中有三个或四个为“1”时,输出端才为“1”。 设计步骤:根据题意列出真值表如表 4-1 所示,再填入表 4-2 中。 表 4-1 D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Z 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 1 表 4-2 DA BC 00 01 11 10 00 01 1 11 1 1 1 10 1 由卡诺图得出逻辑表达式,并演化成“与非”的形式

Z=ABC+BCD+ACD+ABD=ABC.BCD·ACD·ABC 根据逻辑表达式画出用“与非门”构成的逻辑电路如图22-2所示。 & A & D A & 圉2表快电路逻辑图 用实训验证逻辑功能,在实训装置适当位置选定三个14P插座,按照集成块定位标记插 好集成块CC4012。 按图22-2接线,输入端A、B、C、D接至逻辑开关输出插口,输出端Z接逻辑电平显 示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功 能,与表22-1进行比较,验证所设计的逻辑电路是否符合要求。 3.半加器与全加器电路 异或门 异或门 4030「 4030 4030 S(和) =1 S(和) 4011 异或门 4011 4081 4011 与非门 & & C(进位) C(进位) 与门 与非门 与非门 图4-3半加器电路 图4-4全加器电路 三、实训设备与器件 序号 名称 型号与规格 数量 备注 直流稳压电源 +5V 1路 实训台 2 直流数字电压表 1只 实训台 3 逻辑电平输出 DDZ-22 4 逻辑电平显示 DDZ-22 5 14P芯片插座 3个 DDZ-22 6 集成芯片 CC4011 1片 > 集成芯片 CC4030 1片 f 集成芯片 CC4081 1片 四、实训内容与步骤 1. 半加器电路 (1)在实训装置的合适位置选取两个14P插座。插入异或门CC4030和与门CC4081,用 10

10 Z=ABC+BCD+ACD+ABD=ABC BCD ACD ABC 根据逻辑表达式画出用“与非门”构成的逻辑电路如图 22-2 所示。 图 4-2 表决电路逻辑图 用实训验证逻辑功能,在实训装置适当位置选定三个 14P 插座,按照集成块定位标记插 好集成块 CC4012。 按图 22-2 接线,输入端 A、B、C、D 接至逻辑开关输出插口,输出端 Z 接逻辑电平显 示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功 能,与表 22-1 进行比较,验证所设计的逻辑电路是否符合要求。 3. 半加器与全加器电路 图 4-3 半加器电路 图 4-4 全加器电路 三、实训设备与器件 序 号 名 称 型号与规格 数 量 备 注 1 直流稳压电源 +5V 1 路 实训台 2 直流数字电压表 1 只 实训台 3 逻辑电平输出 DDZ-22 4 逻辑电平显示 DDZ-22 5 14P 芯片插座 3 个 DDZ-22 6 集成芯片 CC4011 1 片 7 集成芯片 CC4030 1 片 8 集成芯片 CC4081 1 片 四、实训内容与步骤 1. 半加器电路 (1) 在实训装置的合适位置选取两个 14P 插座。插入异或门 CC4030 和与门 CC4081,用

实训导线按照图43,连接实训电路。 (2)输入端A、B接至逻辑电平输出插口,输出端S和C接逻辑电平显示输入插口,按下 表要求,逐次改变输入变量A、B,测量相应的输出值并记录,验证逻辑功能。 输入 理论输出 实际输出 A b C(进位) S(和) C(进位) S(和) 0 0 0 1 1 0 1 2. 全加器电路 (1)在实训装置的合适位置选取两个14P插座。插入异或门CC4030和与门CC4011,用 实训导线按照图4-4,连接实训电路。 (2)输入端A、B、C接至逻辑电平输出插口,输出端S和C接逻辑电平显示输入插口, 按下表要求,逐次改变输入变量A、B、C,测量相应的输出值并记录,验证逻辑功能。 输入 理论输出 实际输出 A B C C(进位) S(和) C(进位)S(和) 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 0 1 1 1 五、实训总结 1.掌握实训用各集成电路引脚功能。 2.列写实训任务的设计过程,画出设计的电路图。 3.对所设计的电路进行实训测试,记录测试结果。 11

11 实训导线按照图 4-3,连接实训电路。 (2) 输入端 A、B 接至逻辑电平输出插口,输出端 S 和 C 接逻辑电平显示输入插口,按下 表要求,逐次改变输入变量 A、B,测量相应的输出值并记录,验证逻辑功能。 输 入 理论输出 实际输出 A B C(进位) S(和) C(进位) S(和) 0 0 0 1 1 0 1 1 2. 全加器电路 (1) 在实训装置的合适位置选取两个 14P 插座。插入异或门 CC4030 和与门 CC4011,用 实训导线按照图 4-4,连接实训电路。 (2) 输入端 A、B、C 接至逻辑电平输出插口,输出端 S 和 C 接逻辑电平显示输入插口, 按下表要求,逐次改变输入变量 A、B、C,测量相应的输出值并记录,验证逻辑功能。 输 入 理论输出 实际输出 A B C C(进位) S(和) C(进位) S(和) 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 五、实训总结 1. 掌握实训用各集成电路引脚功能。 2. 列写实训任务的设计过程,画出设计的电路图。 3. 对所设计的电路进行实训测试,记录测试结果

实训五译码器 一、实训目的 1.掌握译码器的工作原理和特点。 2.掌握中规模常用集成译码器的逻辑功能和使用方法。 二、实训线路 Yo 9+5V 16 49 15 3 Y 32 Y Yo 9 6 GND S1S,5 Ao A2 8 图5-13线-8线译码器74LS138逻辑图及引脚排列 三、实训设备与器件 序号 名称 型号与规格 数量 备注 直流稳压电源 +5V 1路 实训台 2 直流数字电压表 1只 实训台 3 逻辑电平输出 DDZ-22 4 逻辑电平显示 DDZ-22 5 16P芯片插座 1个 DDZ-22 6 集成芯片 74LS138 1片 四、实训内容与步骤 1.3-8线译码器 用实训连接线将实训台上+5V电源和地连入实训挂箱DDZ-22。实训用集成芯片的管脚 图见图5-1。 (1)在DDZ-22上选取一个16P插座,按定位标记插好74LS138集成块。 (2)根据图23-1的管脚图,将实训挂箱上+5V直流电源接74LS138的16脚,地接8脚。 (3)用实训连接线将译码器地址端Ao、A1、A2(即1、2、3脚)和使能端S1、S2、S;(即 6、4、5脚)分别接至逻辑电平开关输出口,八个输出端接逻辑电平显示的输入口。 (4)按下表在A0、A1、A2三输入端输入高、低电平,检测并记录输出端的电平。 输入 输出 S S2+S: A2 Al A0 Yo Y 72 3 Va Yo V 0 0 0 0 12

12 实训五 译码器 一、实训目的 1. 掌握译码器的工作原理和特点。 2. 掌握中规模常用集成译码器的逻辑功能和使用方法。 二、实训线路 图 5-1 3 线-8 线译码器 74LS138 逻辑图及引脚排列 三、实训设备与器件 序 号 名 称 型号与规格 数 量 备 注 1 直流稳压电源 +5V 1 路 实训台 2 直流数字电压表 1 只 实训台 3 逻辑电平输出 DDZ-22 4 逻辑电平显示 DDZ-22 5 16P 芯片插座 1 个 DDZ-22 6 集成芯片 74LS138 1 片 四、实训内容与步骤 1. 3-8 线译码器 用实训连接线将实训台上+5V 电源和地连入实训挂箱 DDZ-22。实训用集成芯片的管脚 图见图 5-1。 (1) 在 DDZ-22 上选取一个 16P 插座,按定位标记插好 74LS138 集成块。 (2) 根据图 23-1 的管脚图,将实训挂箱上+5V 直流电源接 74LS138 的 16 脚,地接 8 脚。 (3) 用实训连接线将译码器地址端 A0、A1、A2(即 1、2、3 脚)和使能端 S1、S2 、S3 (即 6、4、5 脚)分别接至逻辑电平开关输出口,八个输出端接逻辑电平显示的输入口。 (4) 按下表在 A0、A1、A2三输入端输入高、低电平,检测并记录输出端的电平。 输 入 输 出 S1 S2 + S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 1 0 0 0 0

1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 0 1 0 0 1 0 1 0 1 0 1 1 1 五、实训总结 1.掌握实训用集成电路引脚功能。 2.列写实训任务的设计过程,画出设计的电路图。 13

13 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 五、实训总结 1. 掌握实训用集成电路引脚功能。 2. 列写实训任务的设计过程,画出设计的电路图