复旦大学博士学位论文 图w→r Divider N Divider Divider Divider +M 个 个 Channel selectio Channel selection (a) (6) 图2.9双环路频率综合器的拓扑结构 M M o=N(hn)=Non+ (2-4) 因此频率分辨率为NXf2。选择较小N和较大X,可以使得fe2较大从而使子环路 获得很好的相位噪声,而主环路的速度可以通过改变来进行调节。同样,对于 图2.9(b)[Kan],它的输出频率为: .M oNonov (2-5) 频率分辨率为Ife2,通过提高X来降低子环路的相位噪声,增加fen和降低N来 提高主环路的速度并降低相位噪声。通过2.3节的噪声传输函数的分析,可以知道, 图2.9b)可能比()的噪声性能更好,因为由于在主环路中的噪声注入点的不同,(b) 中主环路对子环路的噪声没有放大作用,而()中主环路对子环路的噪声还要放大N 倍。但是值得注意的是,对于()结构而言,混频器的设计难度要比(b)低得多,所以 在N不大的情况下,结构()也值得考虑。无论如何,两种结构的双环路频率综合器 都能获得很好的性能,但是由于使用了两个频率综合器,这将占用很大的芯片面积, 所以多环路结构的频率综合器只有在其他结构都失效的情况下才值得考虑。 2.5DVB-T系统中的频率综合器结构 2.5.1DVB-T调谐器的结构 ETSI(Europe Telecommunication Standards Institute)在DVB-T协议中并没有明确 的规定频段范围,但是ITU(International Telecommunication Union)己经明确了地面 无线电视广播的频段范围,DVBT的广播也应该在这些频段内。地面无线电视广播 频段被分配在了VHF和UHF频段,在中国涵盖了三个子频段:54~108MHz、 174223MHz、470-890MHz. 22

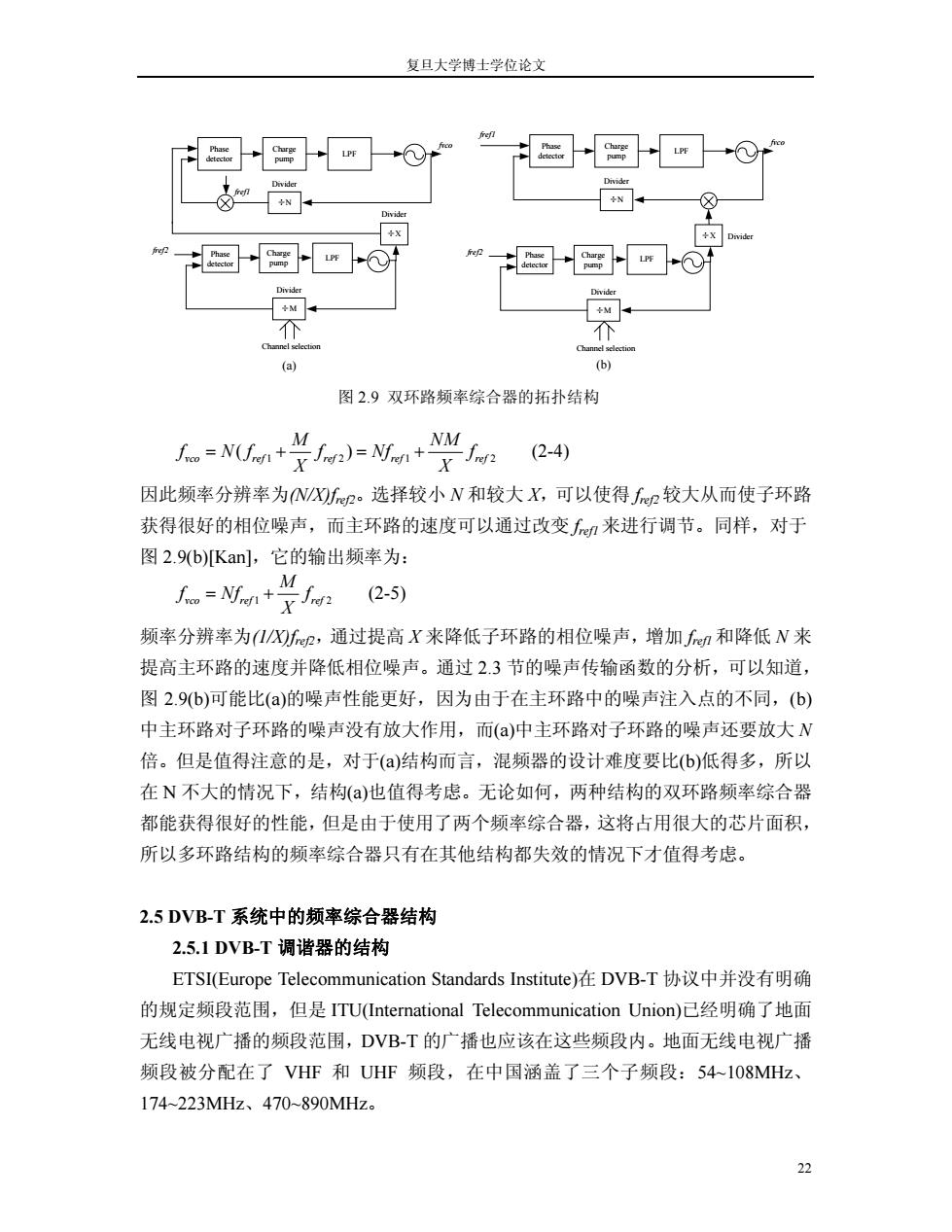

复旦大学博士学位论文 22 1 21 2 ( ) vco ref ref ref ref M NM f N f f Nf f X X = + =+ (2-4) 因此频率分辨率为(N/X)fref2。选择较小 N 和较大 X,可以使得 fref2 较大从而使子环路 获得很好的相位噪声,而主环路的速度可以通过改变 fref1 来进行调节。同样,对于 图 2.9(b)[Kan],它的输出频率为: vco ref ref 1 2 M f Nf f X = + (2-5) 频率分辨率为(1/X)fref2,通过提高 X 来降低子环路的相位噪声,增加 fref1 和降低 N 来 提高主环路的速度并降低相位噪声。通过 2.3 节的噪声传输函数的分析,可以知道, 图 2.9(b)可能比(a)的噪声性能更好,因为由于在主环路中的噪声注入点的不同,(b) 中主环路对子环路的噪声没有放大作用,而(a)中主环路对子环路的噪声还要放大 N 倍。但是值得注意的是,对于(a)结构而言,混频器的设计难度要比(b)低得多,所以 在 N 不大的情况下,结构(a)也值得考虑。无论如何,两种结构的双环路频率综合器 都能获得很好的性能,但是由于使用了两个频率综合器,这将占用很大的芯片面积, 所以多环路结构的频率综合器只有在其他结构都失效的情况下才值得考虑。 2.5 DVB-T 系统中的频率综合器结构 2.5.1 DVB-T 调谐器的结构 ETSI(Europe Telecommunication Standards Institute)在 DVB-T 协议中并没有明确 的规定频段范围,但是 ITU(International Telecommunication Union)已经明确了地面 无线电视广播的频段范围,DVB-T 的广播也应该在这些频段内。地面无线电视广播 频段被分配在了 VHF 和 UHF 频段,在中国涵盖了三个子频段:54~108MHz、 174~223MHz、470~890MHz。 Phase detector Charge pump LPF ÷N Divider fref1 fvco Divider Phase detector Charge pump LPF ÷N Divider fvco fref1 Phase detector Charge pump LPF ÷M Divider fref2 ÷X Channel selection Divider (a) (b) Phase detector Charge pump LPF ÷M Divider fref2 ÷X Channel selection 图 2.9 双环路频率综合器的拓扑结构

第二章频率综合器的结构 由于很难实现调频范围从54MHz到890MHz的振荡器,传统的电视接收机往往 会采用三组振荡器和混频器来处理不同频段的信号[16][17刀,如图2.10(),将接收频 道信号下变频到输出中频(36MHz到46MHz)。同时不同组的模块由于频率和增益也 存在差异,这也导致了处理信号的不均匀性。文献18]提出了二次变频的结构:先 将所有的频道都先上变频到一个高中频,然后再下混频到输出中频。二次变频结构 能够将三组振荡器和混频器减少为两个振荡器和一个混频器,并且也解决了信号处 理不均匀性给基带处理带来的问题。目前集成的电视接收调谐器已经越来越多的采 用这种结构[19][20][21],如图2.10(b)。由于振荡器的频率变高,所以在集成的时候 占用的芯片面积也小:同样由于信号处理频率的升高,往往采用声表面滤波器(SAW) 进行高中频的滤波。 Band pass filters Preamplifiers Antenna ow ban IF filter IF output 4-108MH2 36-46MHz ADC 54890MHz Middle band 74-223MH7 High band 470-890MHz High band Middle band Low band 480-940MHz200-478MHz84-192MH2 (a) Band pass filters Preamplifiers Antenna High IF 亚 SAW filter IF filter IF output 4-108MHU 36-46MHz ADC 54890MHz Middle band 174-223MH 1.12GH2 High band 470-890MH 四 Up-conversion ose Down-conversion osc. 1175-1975MHz 1064-1176MH2 (b) 图2.10电视调谐器的结构图 23

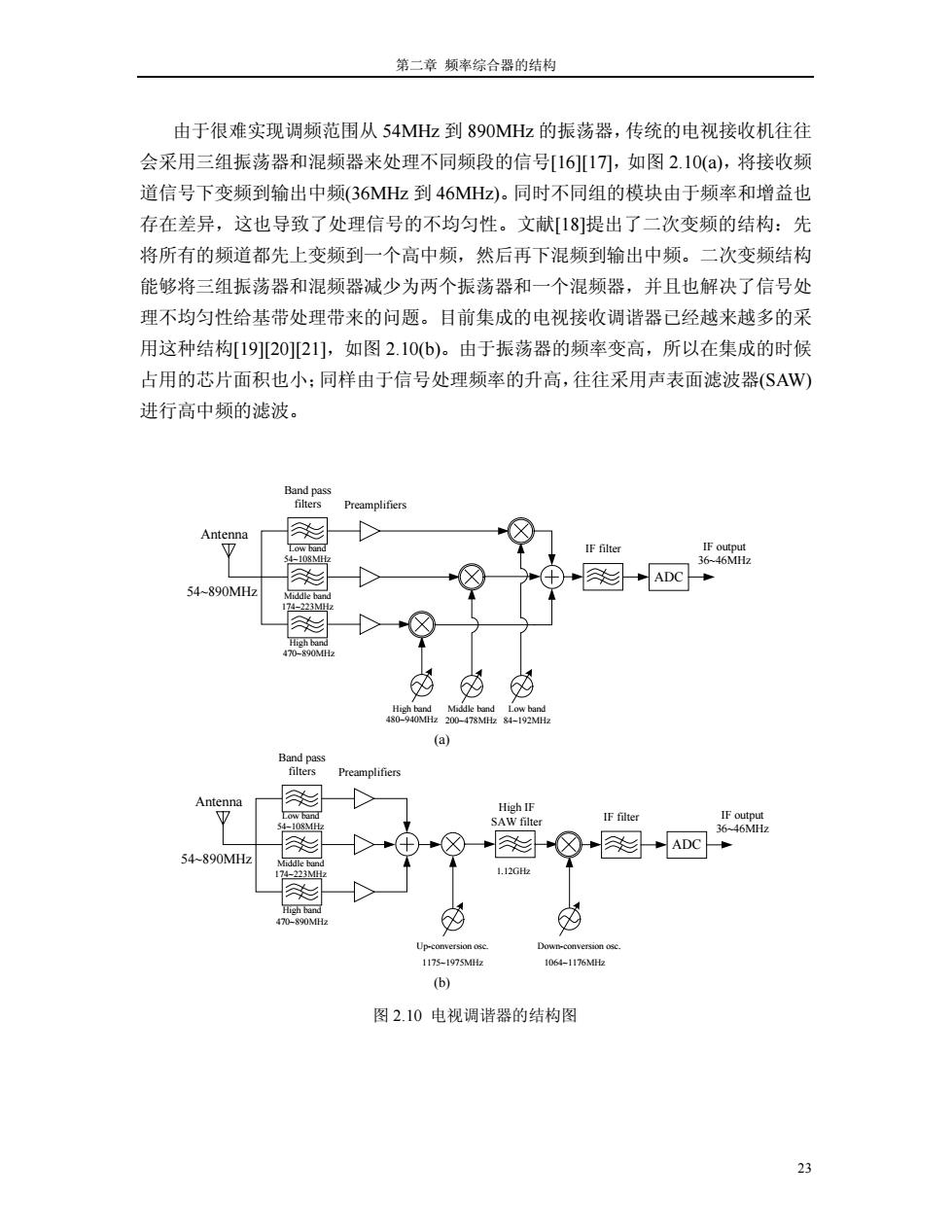

第二章 频率综合器的结构 23 由于很难实现调频范围从 54MHz 到 890MHz 的振荡器,传统的电视接收机往往 会采用三组振荡器和混频器来处理不同频段的信号[16][17],如图 2.10(a),将接收频 道信号下变频到输出中频(36MHz 到 46MHz)。同时不同组的模块由于频率和增益也 存在差异,这也导致了处理信号的不均匀性。文献[18]提出了二次变频的结构:先 将所有的频道都先上变频到一个高中频,然后再下混频到输出中频。二次变频结构 能够将三组振荡器和混频器减少为两个振荡器和一个混频器,并且也解决了信号处 理不均匀性给基带处理带来的问题。目前集成的电视接收调谐器已经越来越多的采 用这种结构[19][20][21],如图 2.10(b)。由于振荡器的频率变高,所以在集成的时候 占用的芯片面积也小;同样由于信号处理频率的升高,往往采用声表面滤波器(SAW) 进行高中频的滤波。 ADC Low band 54~108MHz Middle band 174~223MHz High band 470~890MHz Band pass filters Low band 84~192MHz Middle band 200~478MHz High band 480~940MHz Preamplifiers Antenna IF filter IF output 36~46MHz 54~890MHz ADC Band pass filters Preamplifiers Antenna IF filter IF output 36~46MHz 54~890MHz High IF SAW filter 1.12GHz Up-conversion osc. Down-conversion osc. 1175~1975MHz 1064~1176MHz (a) (b) Low band 54~108MHz Middle band 174~223MHz High band 470~890MHz 图 2.10 电视调谐器的结构图

复旦大学博士学位论文 2.5.2频率综合器的结构 传统的模拟电视广播的信号分为图像信号和声音信号,这些信号离中心频率都 有整数加上250kHz的频偏,所以频率综合器的分辨率至少需要250kHz[19]:另外 由于振荡器之间的频率误差,高性能的频率综合器需要提供小于250kHz的分辨率, 如50kHz[19][20]。因此无论用何种结构的频率综合器,要用CMOS工艺来实现就 存在很大的困难,所以到目前为止调谐器还是以BiCMOS工艺实现,这样就很难与 大规模的基带电路集成在一起。但是数字电视DVB-T的OFDM信号的中心频率和 信道是吻合的,所以不需要有250kHz的分辨率;而振荡器的频率误差也可以在数 字域进行矫正[22],这样降低了频率综合器设计的难度。这样,只要选择合适的中 心频率,就能采用整数分频的频率综合器。但是,为了在实际应用中能兼容数字和 模拟电视,250kHz的分辩率还是需要的,因此本论文还是采用了250kHz作为分辩 率的整数分频频率综合器进行研究,这样会使研究的结果更具意义。 对于第2.41节中介绍的整数分频结构,采用较大的分频比,会对分频器、电荷 泵及环路滤波器的噪声引入较大的增益,这样会恶化整个环路的相位噪声。因此有 必要对整个环路进行优化,包括基于环路稳定性的参数设计,以及相位噪声的估计 和优化。这就是后面几章将要涉及的问题。 参考文献 [1]Floyd M.Gardner.Charge-Pump Phase-Lock Loops.IEEE Trans.on Communications, 1980,28(11)1849~1858 [2]Pavan Kumar Hanumolu,et al.Analysis of Charge-Pump Phase-Locked Loops.IEEE Trans.on Circuits Systems-I:Regular Papers,2004,51(9):1665~1674 [3]Hamid R.Rategh,et al.A CMOS Frequency Synthesizer with an Injection-Locked Frequency Divider for a 5-GHz Wireless LAN Receiver.IEEE J.of Solid-State Circuits, 2000,35(5):780-787 [4]B.Razavi.RF Microelectronics,Prentice Hall,2000. [5]Tom A.D.Riley,Miles A.Copeland,etc."Delta-Sigma Modulation in Fractional-N Frequency Synthesis".IEEE J.of Solid-State Circuit,1993,28(5):553-559. [6]Brian Miller,Robert J.Conley."A Multiple Modulator Fractional Divider".IEEE Trans.on Instrumentation and Measurement,1991,40(3):578-583 [7]W.Rhee,B.S.Song,Akbar Ali."A 1.1GHz CMOS Fractional-N Frequency Synthesizer with a 3-b Third-Order A>Modulator".IEEE J.of Solid-State Circuits,2000, 24

复旦大学博士学位论文 24 2.5.2 频率综合器的结构 传统的模拟电视广播的信号分为图像信号和声音信号,这些信号离中心频率都 有整数加上 250kHz 的频偏,所以频率综合器的分辨率至少需要 250kHz [19];另外 由于振荡器之间的频率误差,高性能的频率综合器需要提供小于 250kHz 的分辨率, 如 50kHz[19][20]。因此无论用何种结构的频率综合器,要用 CMOS 工艺来实现就 存在很大的困难,所以到目前为止调谐器还是以 BiCMOS 工艺实现,这样就很难与 大规模的基带电路集成在一起。但是数字电视 DVB-T 的 OFDM 信号的中心频率和 信道是吻合的,所以不需要有 250kHz 的分辨率;而振荡器的频率误差也可以在数 字域进行矫正[22],这样降低了频率综合器设计的难度。这样,只要选择合适的中 心频率,就能采用整数分频的频率综合器。但是,为了在实际应用中能兼容数字和 模拟电视,250kHz 的分辩率还是需要的,因此本论文还是采用了 250kHz 作为分辩 率的整数分频频率综合器进行研究,这样会使研究的结果更具意义。 对于第 2.4.1 节中介绍的整数分频结构,采用较大的分频比,会对分频器、电荷 泵及环路滤波器的噪声引入较大的增益,这样会恶化整个环路的相位噪声。因此有 必要对整个环路进行优化,包括基于环路稳定性的参数设计,以及相位噪声的估计 和优化。这就是后面几章将要涉及的问题。 参考文献 [1]Floyd M. Gardner. Charge-Pump Phase-Lock Loops. IEEE Trans. on Communications, 1980, 28(11):1849~1858. [2] Pavan Kumar Hanumolu, et al. Analysis of Charge-Pump Phase-Locked Loops. IEEE Trans. on Circuits & Systems-I: Regular Papers, 2004, 51(9):1665~1674. [3] Hamid R. Rategh, et al. A CMOS Frequency Synthesizer with an Injection-Locked Frequency Divider for a 5-GHz Wireless LAN Receiver. IEEE J. of Solid-State Circuits, 2000, 35(5):780~787. [4] B. Razavi. RF Microelectronics, Prentice Hall, 2000. [5] Tom A.D. Riley, Miles A. Copeland, etc. “Delta-Sigma Modulation in Fractional-N Frequency Synthesis”. IEEE J. of Solid-State Circuit, 1993, 28(5):553~559. [6] Brian Miller, Robert J. Conley. “A Multiple Modulator Fractional Divider”. IEEE Trans. on Instrumentation and Measurement, 1991, 40(3):578~583. [7] W. Rhee, B.S. Song, Akbar Ali. “A 1.1GHz CMOS Fractional-N Frequency Synthesizer with a 3-b Third-Order ∆Σ Modulator”. IEEE J. of Solid-State Circuits, 2000

第二章频率综合器的结构 35(10):1453~1460 [8]B.D.Muer,M.S.J.Steyaert."A CMOS Monilithic A-Controlled Fractional-N Frequency Synthesizer for DCS-1800".IEEE J.of Solid-State Circuits,2002, 37(7):835-844. [9]Y.Matsuya,et al."A 16-bit oversampling A/D Conversion Technology Using Triple Integration Noise Shaping".IEEE J.of Solid-State Circuit,1987,22(12):921~929 [10]M.H.Perrott,M.D.Trott,Charles Sodini."A Modeling Approach for Ax Fractional-N Frequency Synthesizers Allowing Straightforward Noise Analysis".IEEEJ. of Solid-State Circuit,2002,37(8):1028~1038. [11]Emad Hegazi,A.A.Abidi."A 17mW Transmitter and Frequency Synthesizer for 900-MHz GSM Fully Integrated in 0.35um CMOS".IEEE J.of Solid-State Circuit,2003,38(5):782~792. [12]R.Ahola,K.Halonen.A 1.76GHz 22.6mW AZ Fractional-N Frequency Synthesizer. IEEE J.of Solid-State Circuits,2003,38(1):138~140. [13]Chun-Huat Heng,Bang-Sup Song."A 1.8GHz CMOS Fractional-N Frequency Synthesizer With Randomized Multiphase VCO".IEEE J.of Solid-State Circuits,2003, 38(6):848-854 [14]W.S.T.Yan,H.C.Luong."A 2-V 900MHz Monolithic CMOS Dual-Loop Frequency Synthesizer for GSM Receivers".IEEE J.of Solid-State Circuit,2001,36(2):204~216. [15]Toby K.K.Kan,Gerry C.T.Leung,H.C.Luong."A 2-V 1.8GHz Fully Integrated CMOS Dual-Loop Frequency Synthesizer".IEEE J.of Solid-State Circuit,2002, 37(8):1012~1020. [16]TUA 6030/6032/6034,Data Sheet.Infineon AG,http://www.infineon.com. [17]SL2610,Data Sheet.Zarlink Semiconductor Inc.,http://www.zarlink.com. [18]G.M.Maier,et al.Double Conversion Tuner:A Must For The Future?"IEEE Trans.on Consumer Electronics,1992,38(3):384-~388. [19]MC44C800/MC44C801 Silicon Tuner.Freescale Semiconductor,Inc.http://www. freescale.com. [20]TDA6650TT/TDA6651TT.Philips Semiconductors.http://www.semiconductor. philips.com. [21]MT8871C Reference Kit.Microtune Inc.http://www.microtune.com. [22]TDA827x,Silicon Tuner Family.Philips Semiconductors.http://www.semiconductor. 25

第二章 频率综合器的结构 25 35(10):1453~1460. [8] B.D. Muer, M.S.J. Steyaert. “A CMOS Monilithic ∆Σ-Controlled Fractional-N Frequency Synthesizer for DCS-1800”. IEEE J. of Solid-State Circuits, 2002, 37(7):835~844. [9] Y. Matsuya, et al. “A 16-bit oversampling A/D Conversion Technology Using Triple Integration Noise Shaping”. IEEE J. of Solid-State Circuit, 1987, 22(12):921~929. [10] M.H. Perrott, M.D. Trott, Charles Sodini. “A Modeling Approach for ∆Σ Fractional-N Frequency Synthesizers Allowing Straightforward Noise Analysis”. IEEE J. of Solid-State Circuit, 2002, 37(8):1028~1038. [11] Emad Hegazi, A.A. Abidi. “A 17mW Transmitter and Frequency Synthesizer for 900-MHz GSM Fully Integrated in 0.35um CMOS”. IEEE J. of Solid-State Circuit,2003,38(5):782~792. [12] R. Ahola, K. Halonen. A 1.76GHz 22.6mW ∆Σ Fractional-N Frequency Synthesizer. IEEE J. of Solid-State Circuits, 2003, 38(1):138~140. [13] Chun-Huat Heng, Bang-Sup Song. “A 1.8GHz CMOS Fractional-N Frequency Synthesizer With Randomized Multiphase VCO”. IEEE J. of Solid-State Circuits, 2003, 38(6):848~854. [14] W.S.T. Yan, H.C. Luong. “A 2-V 900MHz Monolithic CMOS Dual-Loop Frequency Synthesizer for GSM Receivers”. IEEE J. of Solid-State Circuit, 2001,36(2):204~216. [15] Toby K.K. Kan, Gerry C.T. Leung, H.C. Luong. “A 2-V 1.8GHz Fully Integrated CMOS Dual-Loop Frequency Synthesizer”. IEEE J. of Solid-State Circuit, 2002, 37(8):1012~1020. [16] TUA 6030/6032/6034, Data Sheet. Infineon AG, http://www.infineon.com. [17] SL2610, Data Sheet. Zarlink Semiconductor Inc., http://www.zarlink.com. [18] G. M. Maier, et al. “ Double Conversion Tuner: A Must For The Future?” IEEE Trans. on Consumer Electronics, 1992, 38(3):384~388. [19] MC44C800/MC44C801 Silicon Tuner. Freescale Semiconductor, Inc. http: //www. freescale.com. [20] TDA6650TT/TDA6651TT. Philips Semiconductors. http://www.semiconductor. philips.com. [21] MT8871C Reference Kit. Microtune Inc. http://www.microtune.com. [22] TDA827x, Silicon Tuner Family. Philips Semiconductors. http://www.semiconductor

复旦大学博士学位论文 philips.com. [23]Jan Craninckx,M.Steyaert.A Fully Integrated CMOS DCS-1800 Frequency Synthesizer.IEEE J.of Solid-State Circuits,1998,33(12):2054~2065. [24]Adrian Maxim,Baker Scott,Edmund M.Schneider,et al "A Low-Jitter 25~1250 MHz Process-Independent and Ripple-Poleless 0.18um CMOS PLL Based on a Sample Reset Loop Filter".IEEE J.of Solid-State Circuits,2001,36(11):1673~1683. 26

复旦大学博士学位论文 26 philips.com. [23] Jan Craninckx, M. Steyaert. A Fully Integrated CMOS DCS-1800 Frequency Synthesizer. IEEE J. of Solid-State Circuits, 1998, 33(12):2054~2065. [24] Adrian Maxim, Baker Scott, Edmund M. Schneider, et al “A Low-Jitter 25~1250 MHz Process-Independent and Ripple- Poleless 0.18µm CMOS PLL Based on a Sample Reset Loop Filter”. IEEE J. of Solid-State Circuits, 2001, 36(11):1673~1683