减小beq损失:单周期分支,ID段完成 Flushed Continued add Sr1.5r2,5r3 sw$1,0r2) sUb51,5r2,33 wsr1.05r2) slt $r1,5r2.$r3 Flushed Continued IF ID EX MEM WB add Sr1.$r2.Sr3 Beg Sr2.Sr5.0x08 sw Sr1,0(Sr2) sub Sr1.,Sr2.Sr3 sit Sr1.Sr2,Sr3 ←---Flushed---- Add Sr1,$r2,Sr4 Add Sr2 Sr2,Sr3 Beq Sr2.Sr5 Lw Sr2.0x04(Sr0)Lw Sr4.Ox0d(Sro) IF EX MEM WB IF ID EX MEM WB Instruction flow Instruction flow Program execution 200 400 600 800 1000 1200 1400 Time order (in instructions) 图4-29,设D段完成, add x4,x5,x6 Instruction fetch Reg ALU Data access Reg 则只需Stall-一个cc! beq x1,x0,40 Instruction Data 200ps fetch Reg ALU access Reg bubble bubble bubble bubble bubble 0 or x7,x8,x9 Instruction 400ps fetch Reg ALU Data access Reg

减小beq损失:单周期分支,ID段完成 图4-29,设ID段完成, 则只需Stall一个cc!

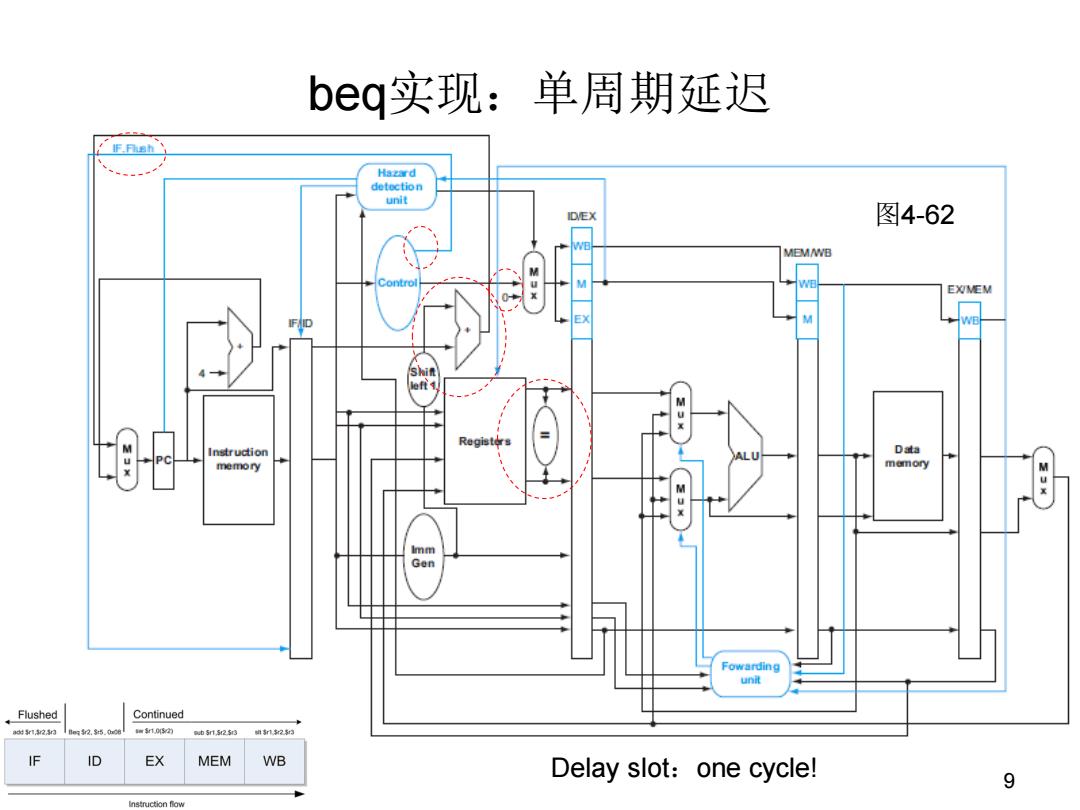

单周期分支实现 ·将beq完成时间从MEM提前到lD -将加法器挪到ID段,计算nPC 一在D段增加一个比较器,判断分支条件 ·针对“简单条件判断”:相等(按位xor,再or) ·不适于“复杂条件判断”:需要ALU计算 一假设分支不发生!!! ·分支发生:只需更新PC和flush IF段 -clear up:增加IF.Flush,清空FID(图4-62) ·“由controler控制1F.Fush”:应该与比较器联合控制吧? -bubble down:向ID/EX送“0” Flushed Continued w132na0阳32,5,0a08 sw Sr1.0(5r2) sub Sr1,Sr2.Sr3 t51.23 ·损失一个周期 IF 0 EX MEM WB Instruction flow

单周期分支实现 • 将beq完成时间从MEM提前到ID – 将加法器挪到ID段,计算nPC – 在ID段增加一个比较器,判断分支条件 • 针对“简单条件判断”:相等(按位xor,再or) • 不适于“复杂条件判断”:需要ALU计算 – 假设分支不发生!!! • 分支发生:只需更新PC和flush IF段 – clear up:增加IF.Flush,清空IF/ID(图4-62) • “由controler控制 IF.Flush” :应该与比较器联合控制吧? – bubble down:向ID/EX送“0” • 损失一个周期

beq实现:单周期延迟 IF.Fhsh Hazard detoction unit ID/EX 图4-62 MEMNB Contro WE EXMEM M Dsts memory memory imm Gen Fowarding unit Flushed Continued ad时5r12n 2.5.000 m$105的 eub Sr1.5r2.5r3 1多2的 IF ID EX MEM WB Delay slot:one cycle! 9 ction fiow

9 beq实现:单周期延迟 图4-62 Delay slot:one cycle!

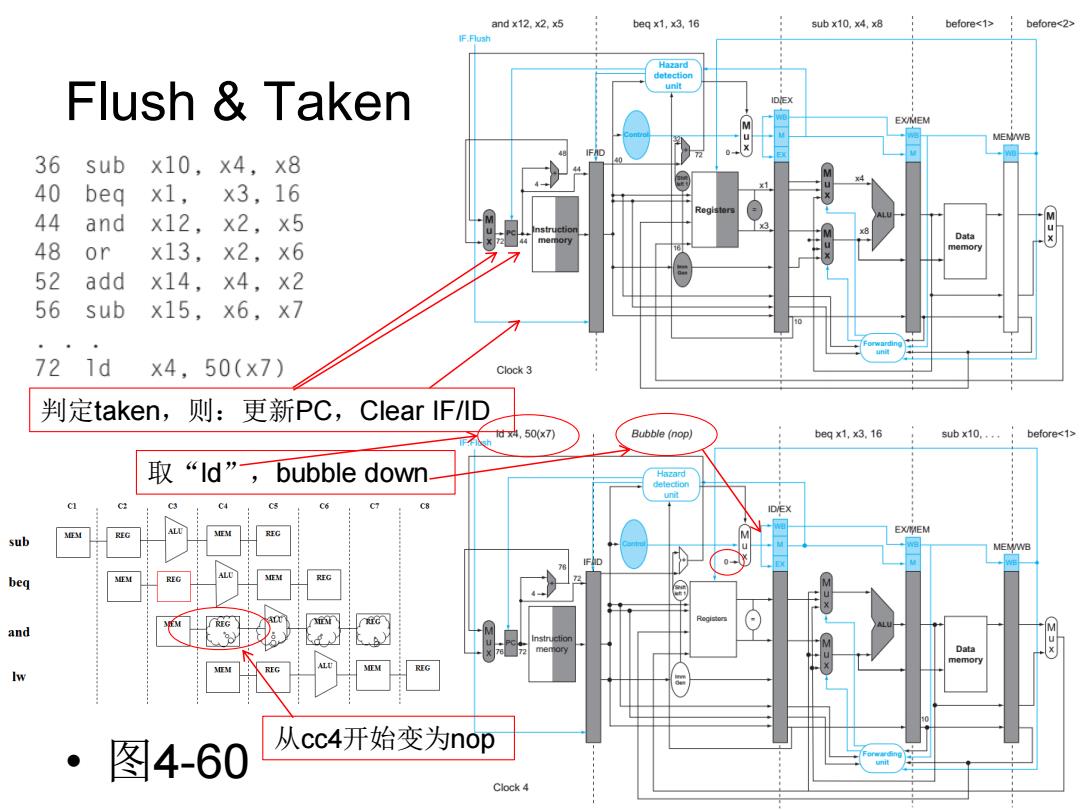

and x12,x2,x5 beq x1,x3,16 sub x10,x4,x8 before<1> before<2> Hazard detection unit Flush Taken EX/MEM MEMNWB 36 sub x10,X4,×8 40 beq ×1, ×3,16 44 and x12,x2,x5 memory Data M口X 48 or x13,x2,x6 memory 52 add x14, ×4,×2 56 sub x15, x6,x7 721d ×4,50(x7) Clock 3 判定taken,则: 更新PC,Clear IF/ID d对,50x7) Bubble(nop) beq x1,x3.16 5ubx10,.,+ before<1> 取“ld”,bubble down Hazard REG L REC EX/MEM sub MEMWB beq MEM REG and memory Data M Iw ·图4-60 从cc4开始变为nop Clock 4

Flush & Taken • 图4-60 判定taken,则:更新PC,Clear IF/ID 从cc4开始变为nop 取“ld”,bubble down

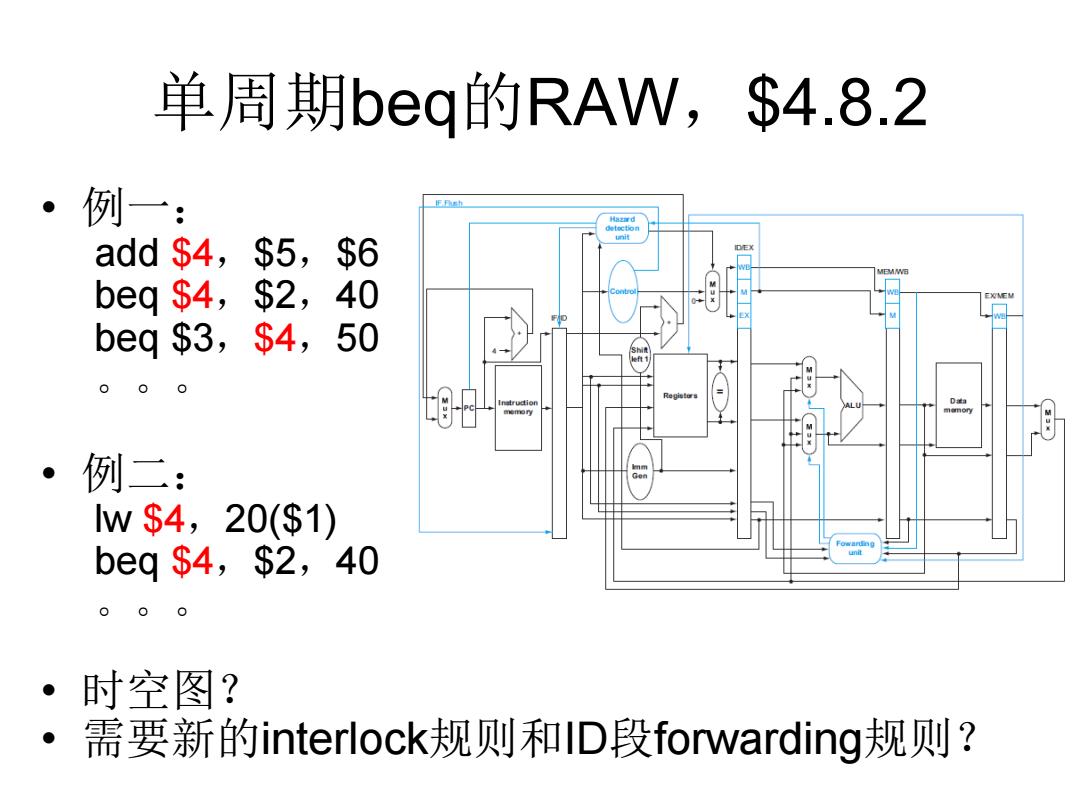

单周期beq的RAW,$4.8.2 例一: IF Fheh add$4,$5, $6 beq$4,$2,40 beq $3,s $4,50 00 D ·例二: w$4,20($1) beq$4,$2,40 00 o 时空图? 需要新的interlock规则和ID段forwarding规则?

单周期beq的RAW,$4.8.2 • 例一: add $4,$5,$6 beq $4,$2,40 beq $3,$4,50 。。。 • 例二: lw $4,20($1) beq $4,$2,40 。。。 • 时空图? • 需要新的interlock规则和ID段forwarding规则?