beq指令的性能,$4.5 ·单周期分支stal对性能的影响,例 -SPECINT2006中,条件分支占17%。设其他 指令CPI=1。 -单周期条件分支需stal一个周期,因此平均 CP=1.17,即性能下降1.17倍 一原始版本 (beq在MEM完成)的CPI=? addS4,$5,$6 Instruction Data fetch Reg ALU access Reg beq$1,$2,40 Instruction Reg ALU Data 200pS fetch access Reg bubble bubble. bubble bubble bubble 0 or$7,$8,$9 nstruction Data 400ps fetch Reg ALU access Reg

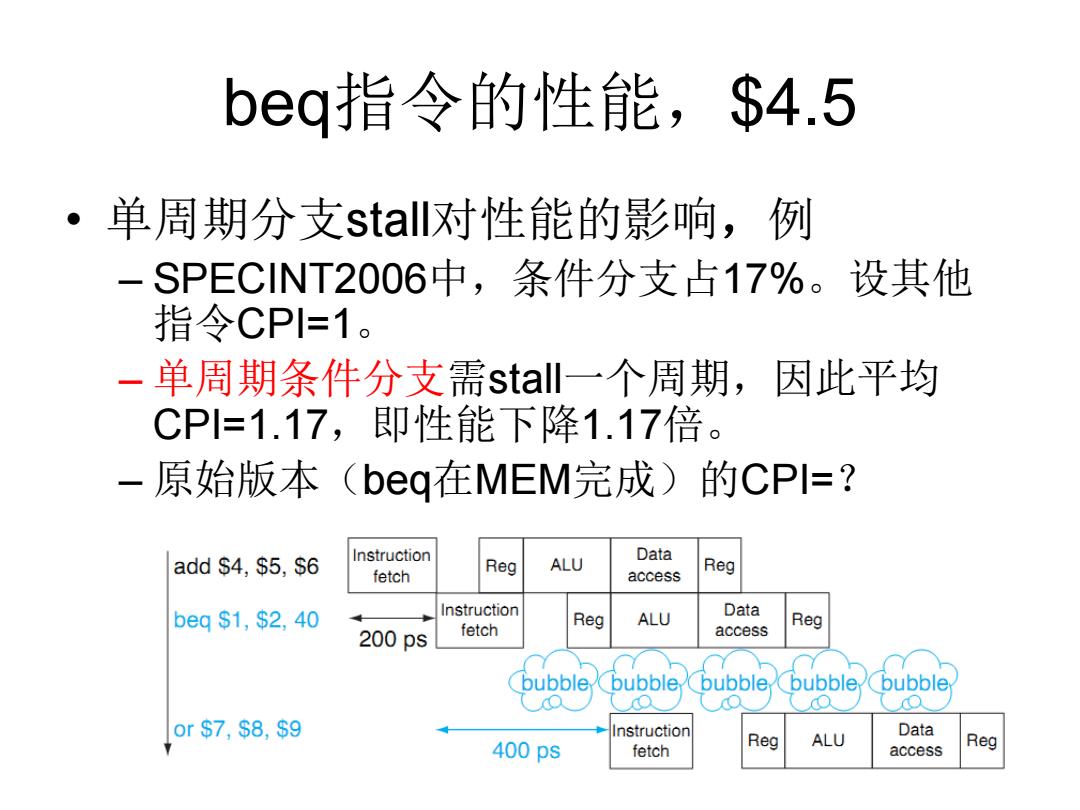

beq指令的性能,$4.5 • 单周期分支stall对性能的影响,例 – SPECINT2006中,条件分支占17%。设其他 指令CPI=1。 – 单周期条件分支需stall一个周期,因此平均 CPI=1.17,即性能下降1.17倍。 – 原始版本(beq在MEM完成)的CPI=?

Pipelining Hazards小结 “A hazard(相关,冒险)is a situation that prevents starting the next instruction in the next clock cycle"? -Structural hazard,结构冲突 A required resource is busy(e.g.needed in multiple stages) Can always solve a structural hazard by adding more hardware Memory Structural Hazards:separate instruction/data memories load/store (at most one memory access per instruction) RegFile Structural Hazards:single write-port load-ALU:ALU instruction passing MEM Data hazard,数据依赖 匹图 Data dependency between instructions Need to wait for previous instruction to complete its data write Forwarding:grab operand from Interstage-Buf,rather than RegFile. Multilevel Bypass:EX bypassing,Load/Store Bypassing,beq bypassing Can't solve all cases with forwarding:load-use-data need to Stall -WB stage:RegFile Double Pumping-一“内推” Control hazard,转移损失 Flow of execution depends on previous instruction Flushing:Single cycle branch Branch prediction:Zero cycle branch

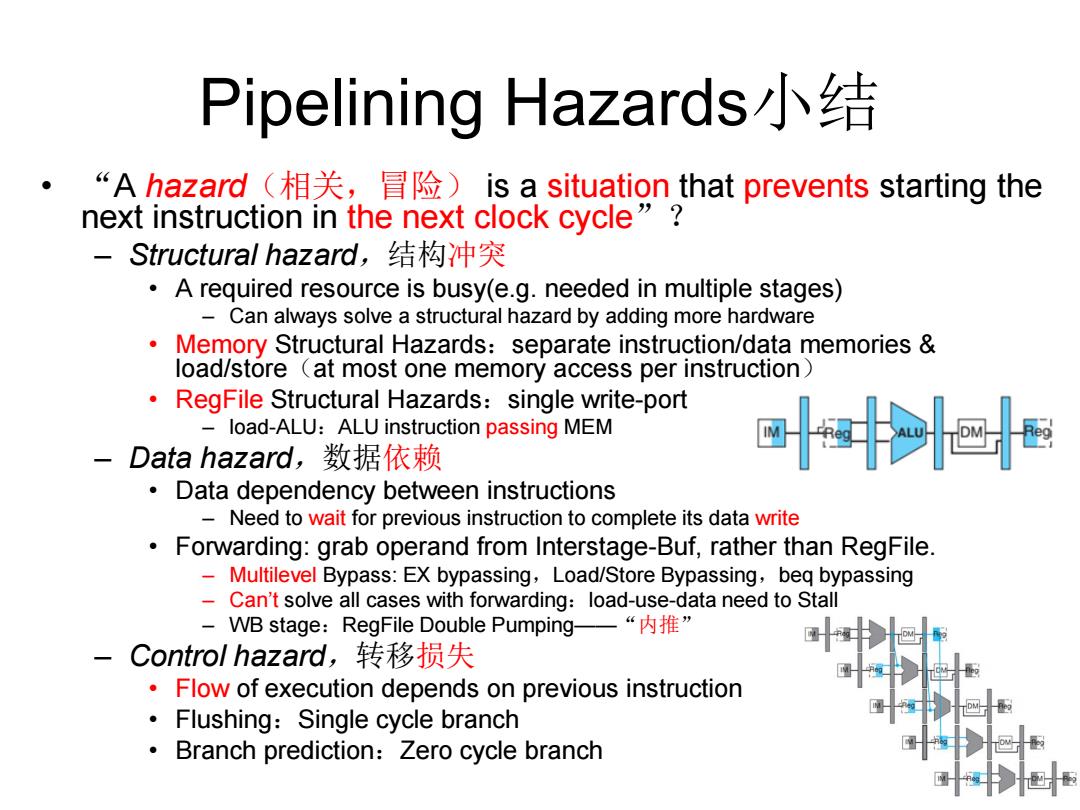

Pipelining Hazards小结 • “A hazard(相关,冒险) is a situation that prevents starting the next instruction in the next clock cycle”? – Structural hazard,结构冲突 • A required resource is busy(e.g. needed in multiple stages) – Can always solve a structural hazard by adding more hardware • Memory Structural Hazards:separate instruction/data memories & load/store(at most one memory access per instruction) • RegFile Structural Hazards:single write-port – load-ALU:ALU instruction passing MEM – Data hazard,数据依赖 • Data dependency between instructions – Need to wait for previous instruction to complete its data write • Forwarding: grab operand from Interstage-Buf, rather than RegFile. – Multilevel Bypass: EX bypassing,Load/Store Bypassing,beq bypassing – Can’t solve all cases with forwarding:load-use-data need to Stall – WB stage:RegFile Double Pumping——“内推” – Control hazard,转移损失 • Flow of execution depends on previous instruction • Flushing:Single cycle branch • Branch prediction:Zero cycle branch