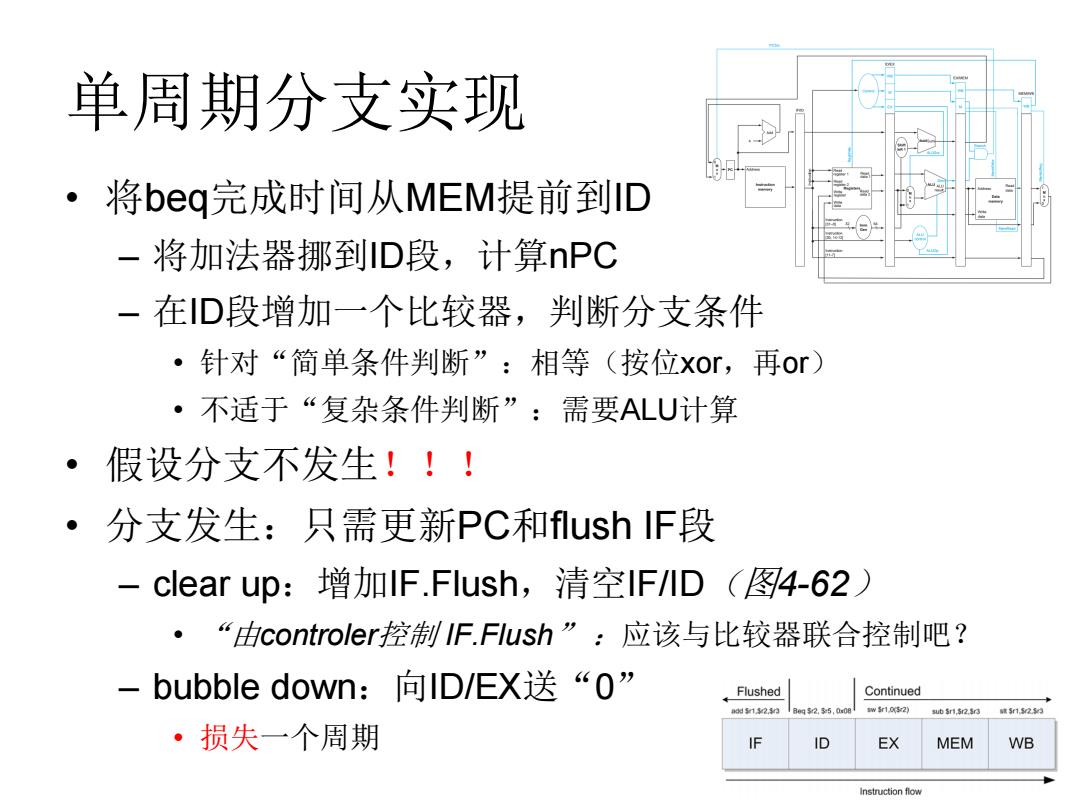

单周期分支实现 ·将beq完成时间从MEM提前到ID -将加法器挪到ID段,计算nPC 一在D段增加一个比较器,判断分支条件 ·针对“简单条件判断”:相等(按位xor,再or) ·不适于“复杂条件判断”:需要ALU计算 ·假设分支不发生!!! ·分支发生:只需更新PC和flush IF段 -clear up:增加IF.Flush,清空IFID(图4-62) ·“由controler挖制IF.Fush”:应该与比较器联合控制吧? -bubble down:向lD/EX送“0” Flushed Continued 4的132粉a0阳32.55,008 sw Sr1.0(5r2) sub Sr1,Sr2.Sr3 t51.23 ·损失一个周期 IF 0 EX MEM WB Instruction flow

单周期分支实现 • 将beq完成时间从MEM提前到ID – 将加法器挪到ID段,计算nPC – 在ID段增加一个比较器,判断分支条件 • 针对“简单条件判断”:相等(按位xor,再or) • 不适于“复杂条件判断”:需要ALU计算 • 假设分支不发生!!! • 分支发生:只需更新PC和flush IF段 – clear up:增加IF.Flush,清空IF/ID(图4-62) • “由controler控制 IF.Flush” :应该与比较器联合控制吧? – bubble down:向ID/EX送“0” • 损失一个周期

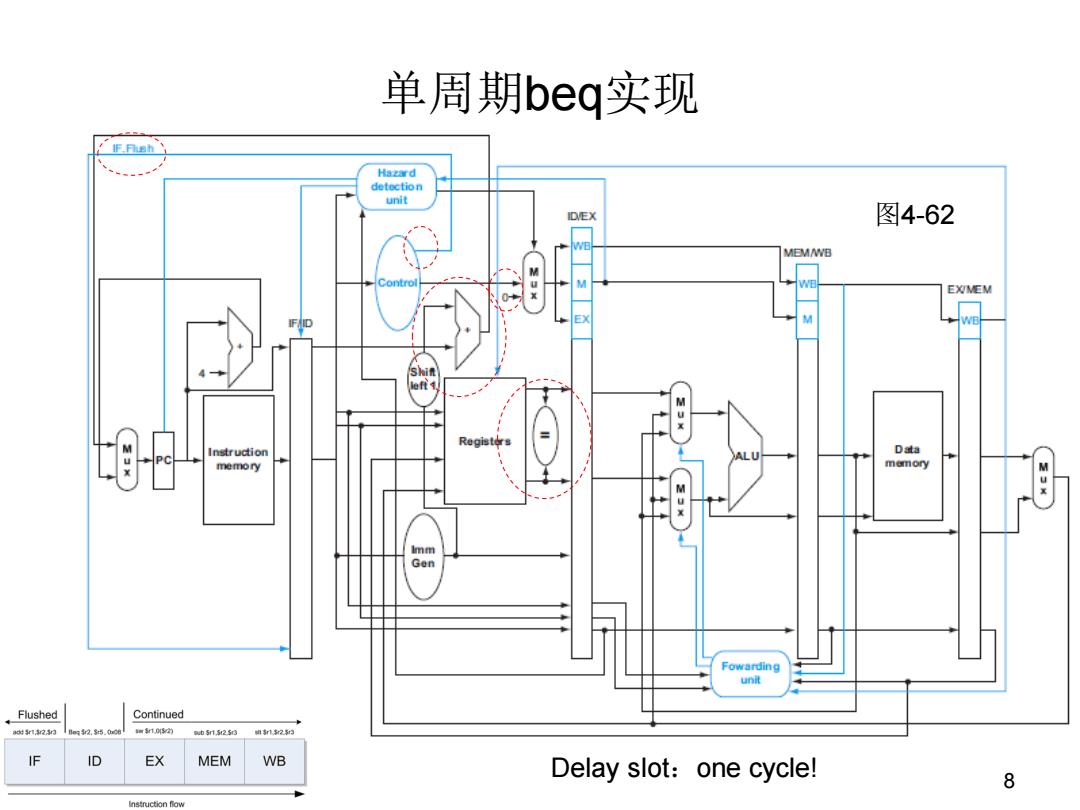

单周期beq实现 IF.Fhsh Hazard detoction unit ID/EX 图4-62 MEMNB M Contro WE EXMEM M Dsts memory memory imm Gen Fowarding unit Flushed Continued ad时5r12n 2.5.000 m$105的 eub Sr1.5r2.5r3 1多2的 F ID EX MEM WB Delay slot:one cycle! 8 n灯 ction fiow

8 单周期beq实现 图4-62 Delay slot:one cycle!

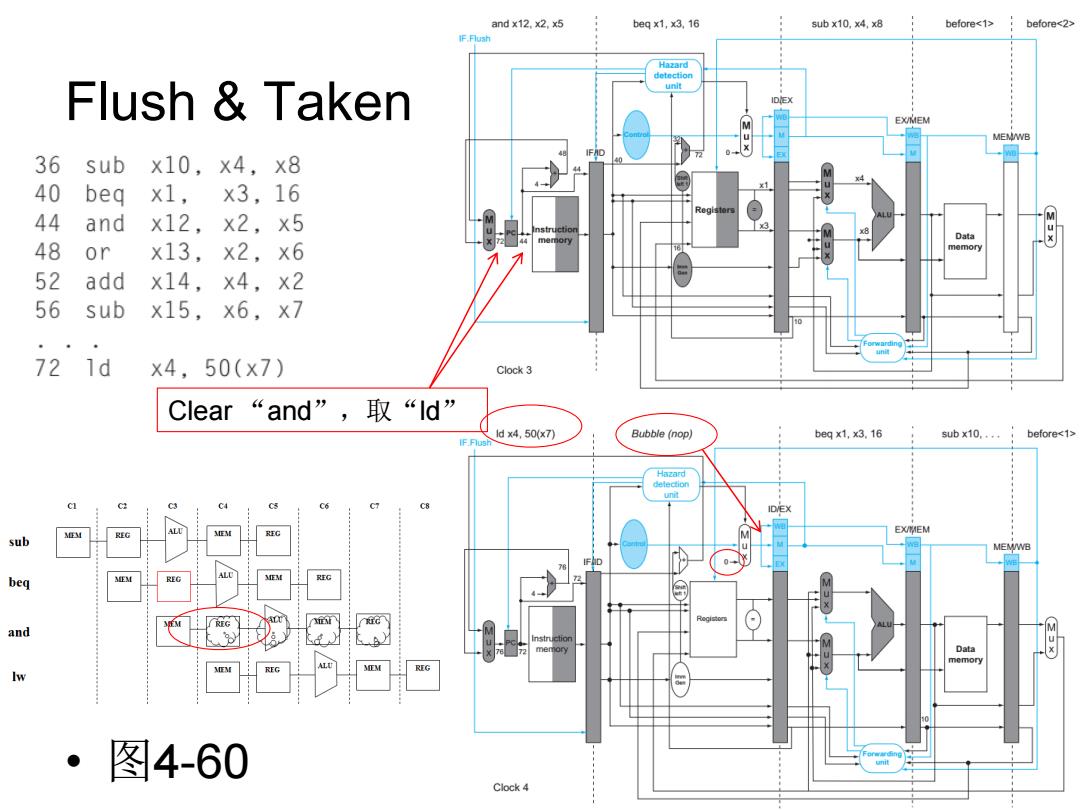

and x12,x2,x5 beq x1,x3,16 sub x10,x4,x8 before<1> before<2> F月ush Hazard detection unit Flush Taken EX/MEM MEMNWB 36 sub x10,X4,×8 40 beq ×1, ×3,16 44 and ×12,x2,x5 M memory Data 48 or x13,x2,x6 memory 52 add x14,×4,x2 56 sub x15,x6,x7 721d ×4, 50(×7) Clock 3 Clear“and”,取“ld” 1dx4,50(x7) Bubble(nop) beq x1,x3.16 5ubx10..,+; before<1> IF.Flus Hazard C3 C4 C8 EX/MEM REG sub MEMWB MEM REC beq M REG and 7 memory Data R正0 EM Iw ·图4-60 Clock 4

Flush & Taken • 图4-60 Clear “and”,取“ld

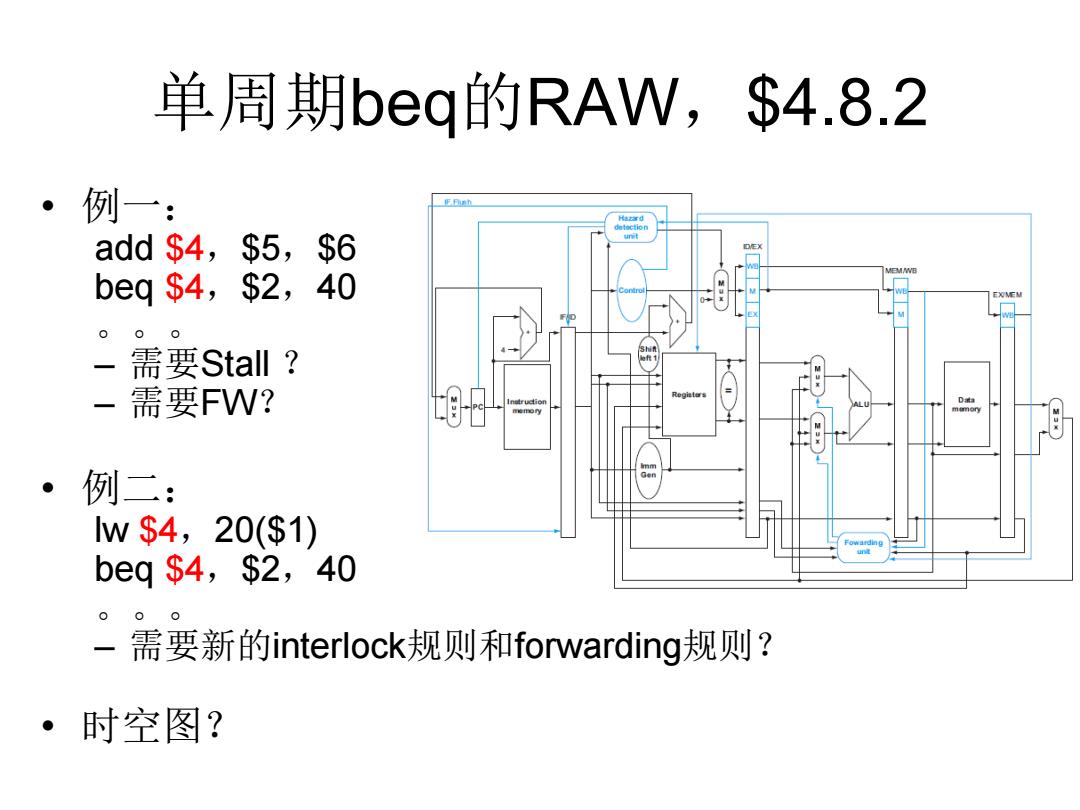

单周期beq的RAW,$4.8.2 ·例一: IF Pah add$4,$5,$6 beq$4,$2,40 0 需要Stall? -需要FW? D 例二: w$4,20($1) beq$4,$2,40 0 需要新的interlock规则和forwarding规则? ·时空图?

单周期beq的RAW,$4.8.2 • 例一: add $4,$5,$6 beq $4,$2,40 。。。 – 需要Stall ? – 需要FW? • 例二: lw $4,20($1) beq $4,$2,40 。。。 – 需要新的interlock规则和forwarding规则? • 时空图?

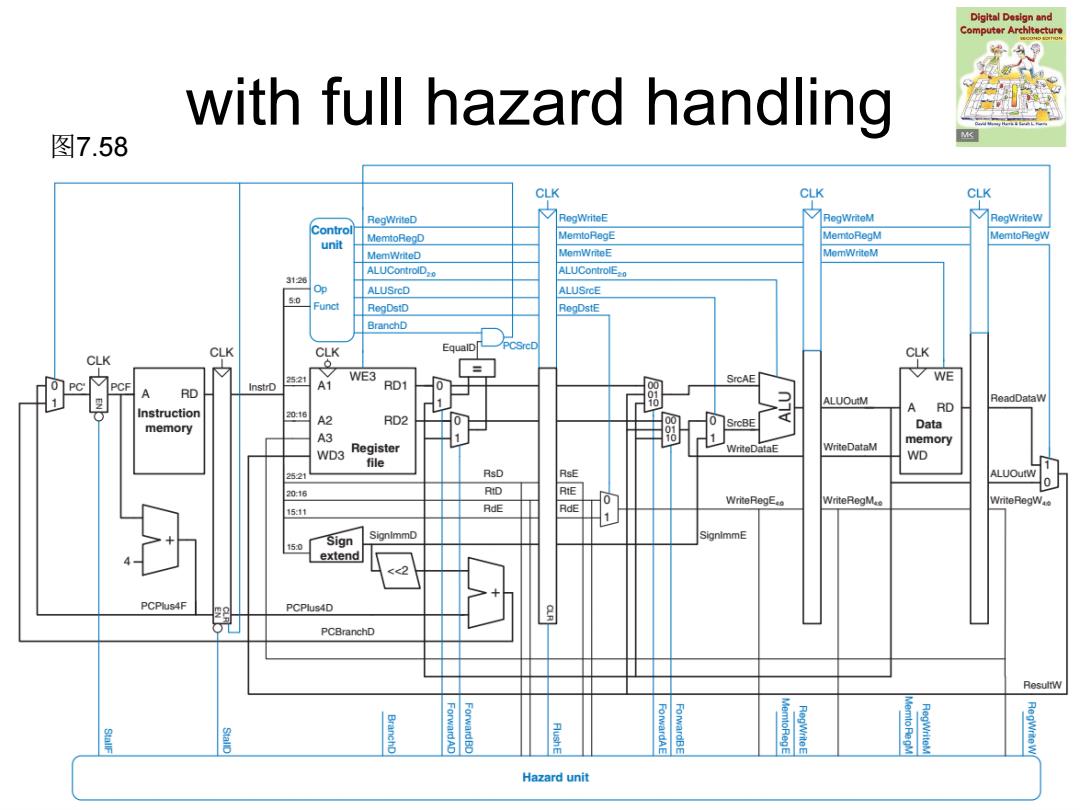

Digltal Design and Computer Architecture with full hazard handling 图7.58 CLK CLK CLK RegWriteD RegWriteE Control MemtoRegD MemtoRegE MemtoRegM MemtoRegW unit MemWriteD MemWriteE MemWriteM ALUControlDo ALUControlE2o 3120 Op ALUSrcD ALUSrcE 5:0 Funct RegDstD RegDstE BranchD CLK CLK EqualD CLK CLK 2521 WE3 WE RD Instro A1 RD1 1 ALUOutM ReadDataW Instruction A RD 20:16 memory A2 RD2 SrcBE Data A3 1 WD3 Register WriteDataE WriteDataM memory file WD 2521 RsD RsE ALUOutW 20:16 RtD RdE RdE WriteRegE WriteRegM. 1511 Sign SignlmmD 150 extend <<2 PCPlus4F PCPlus4D PCBranchD BranchD ForwardAD Forward BO ForwardAE ForwardBE MemtoRegE RegWriteE emto RegM Hazard unit

with full hazard handling 图7.58