内容提要 Digital Design and Computer Architecture ·流水线技术原理:4.5 ·RV的五级流水线实现:4.6 M< -Verilog行为级定义:4.13 MODERN PROCESSOR DESIGN 物 。Hazard问题:4.5.2 一结构冲突:哈佛结构 -数据依赖:4.7 ·编译技术:插入nop,指令重排,寄存器重命名 MIPS体系结构透 ·forwarding技术:RAW ·Interlock技术:Stall Run -控制相关:4.8 ·编译技术:延迟分支 ·硬件优化:提前完成,投机,预测 。多发射技术:4.10 Parallel Computer Organization 硬件多线程:6.4 and Design

内容提要 • 流水线技术原理:4.5 • RV的五级流水线实现:4.6 – Verilog行为级定义:4.13 • Hazard问题:4.5.2 – 结构冲突:哈佛结构 – 数据依赖:4.7 • 编译技术:插入nop,指令重排,寄存器重命名 • forwarding技术:RAW • Interlock技术:Stall – 控制相关:4.8 • 编译技术:延迟分支 • 硬件优化:提前完成,投机,预测 • 多发射技术:4.10 • 硬件多线程:6.4

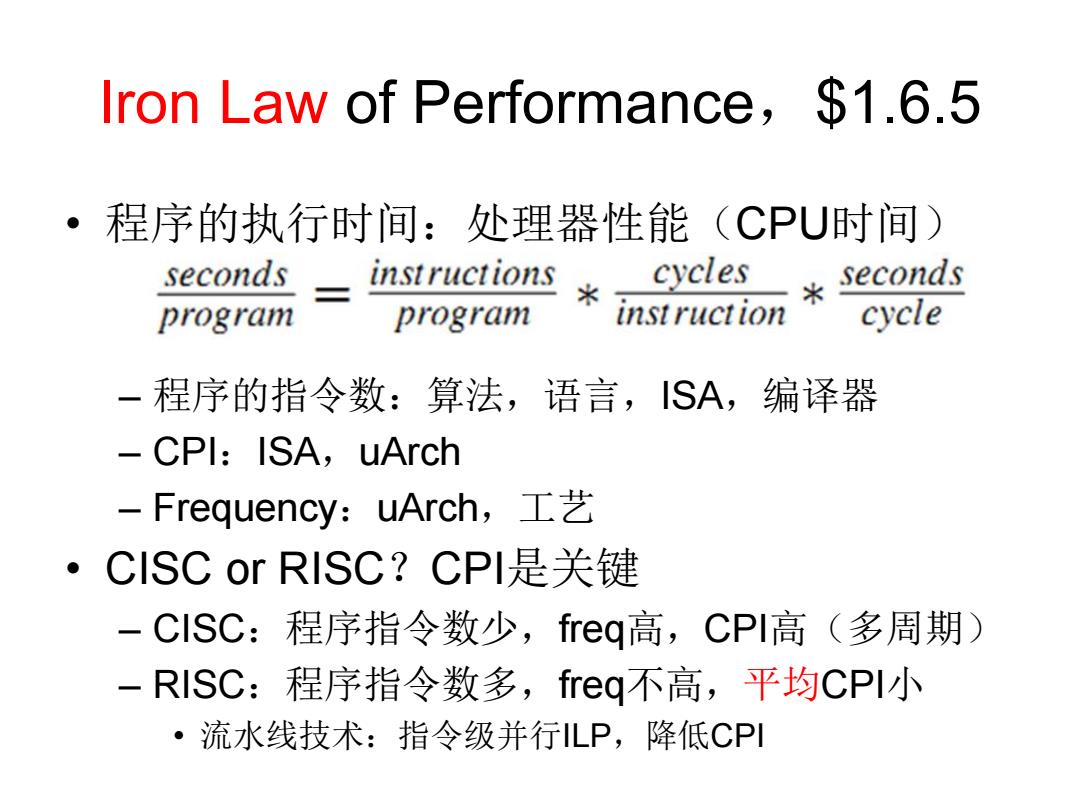

Iron Law of Performance,$1.6.5 ·程序的执行时间:处理器性能(CPU时间) seconds instructions cycles seconds program program inst ruction cycle 一程序的指令数:算法,语言,ISA,编译器 CPI:ISA,uArch -Frequency:uArch,工艺 ·CISC or RISC?CPI是关键 -CISC:程序指令数少,freq高,CPI高(多周期) -RISC:程序指令数多,freq不高,平均CPI小 ·流水线技术:指令级并行LP,降低CPI

Iron Law of Performance,$1.6.5 • 程序的执行时间:处理器性能(CPU时间) – 程序的指令数:算法,语言,ISA,编译器 – CPI:ISA,uArch – Frequency:uArch,工艺 • CISC or RISC?CPI是关键 – CISC:程序指令数少,freq高,CPI高(多周期) – RISC:程序指令数多,freq不高,平均CPI小 • 流水线技术:指令级并行ILP,降低CPI

Laundry Example 6 PM 7 8 9 10 11 Midnight 6PM 7 8 9 10 11 Midnight Time Time 304020304020304020304020 304040404020 T a 同 司¥ 6 6 同 e 6 4袋衣服:Wash(30),dry(40),fold(20) Sequential Laundry ·需要6小时:4x(30+40+20)=360分钟 Pipelined Laundry: ·需3.5小时:30+4x40+20=210分钟 ·1 前提:设备独立(单缸,双缸?),作业等时 流水线基于:提升“吞吐率”。CP=? -贪心—Start work ASAP!一袋衣服? CSC顺序模型,RISC指令级并行模型(ILP)

Laundry Example • 4 袋衣服:Wash(30), dry(40), fold(20) – Sequential Laundry • 需要 6 小时:4x(30+40+20)=360分钟 – Pipelined Laundry: • 需3.5小时:30+4x40+20=210分钟 • 前提:设备独立(单缸,双缸?),作业等时 • 流水线基于:提升“吞吐率”。CPI=? – 贪心——Start work ASAP!一袋衣服? • CISC顺序模型,RISC指令级并行模型(ILP)

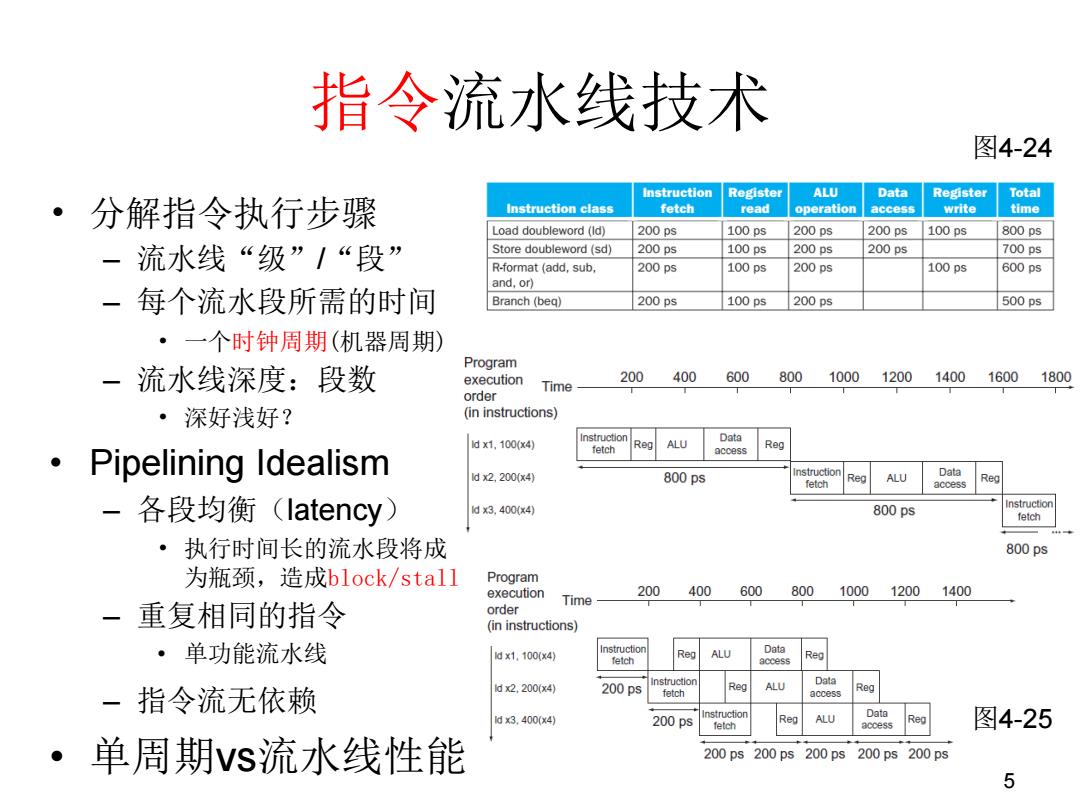

指令流水线技术 图4-24 Instruction Register ALU Data Register Total ·分解指令执行步骤 Instruction class fetch read operation access write time Load doubleword (ld) 200ps 100ps 200ps 200ps 100ps 800ps 一流水线“级”/“段” Store doubleword(sd) 200ps 100ps 200ps 200ps 700ps R-format(add,sub, 200pS 100ps 200ps 100ps 600ps and,or) 一每个流水段所需的时间 Branch (beq) 200ps 100ps 200ps 500ps ·一个时钟周期(机器周期) Program 一流水线深度:段数 execution 200 400600 800 1000120014001600 1800 Time order ·深好浅好? (in instructions) dx1,100(x4) Instruction Data fetch Reg ALU Reg access ·Pipelining Idealism 1dX2,200x4 800ps nstruction Data fetch Reg ALU Reg access -各段均衡(latency) 1dX3.400x4) Instruction 800ps fetch ·执行时间长的流水段将成 800ps 为瓶颈,造成block/stall Program execution 200 400 600 800 1000 12001400 Time 一重复相同的指令 order (in instructions) ·单功能流水线 1dx1.100(x4) Instructior Reg ALU Data fetch access Reg Instructior Reg ALU Data 一指令流无依赖 1dx2,200(x4) 200ps fetch access Reg Instruction Data dx3.400(x4) 200ps ALU fetch Reg access 图4-25 ·单周期VS流水线性能 200ps200ps200ps200ps200ps 5

5 指令流水线技术 • 分解指令执行步骤 – 流水线“级”/“段” – 每个流水段所需的时间 • 一个时钟周期(机器周期) – 流水线深度:段数 • 深好浅好? • Pipelining Idealism – 各段均衡(latency) • 执行时间长的流水段将成 为瓶颈,造成block/stall – 重复相同的指令 • 单功能流水线 – 指令流无依赖 • 单周期vs流水线性能 图4-25 图4-24

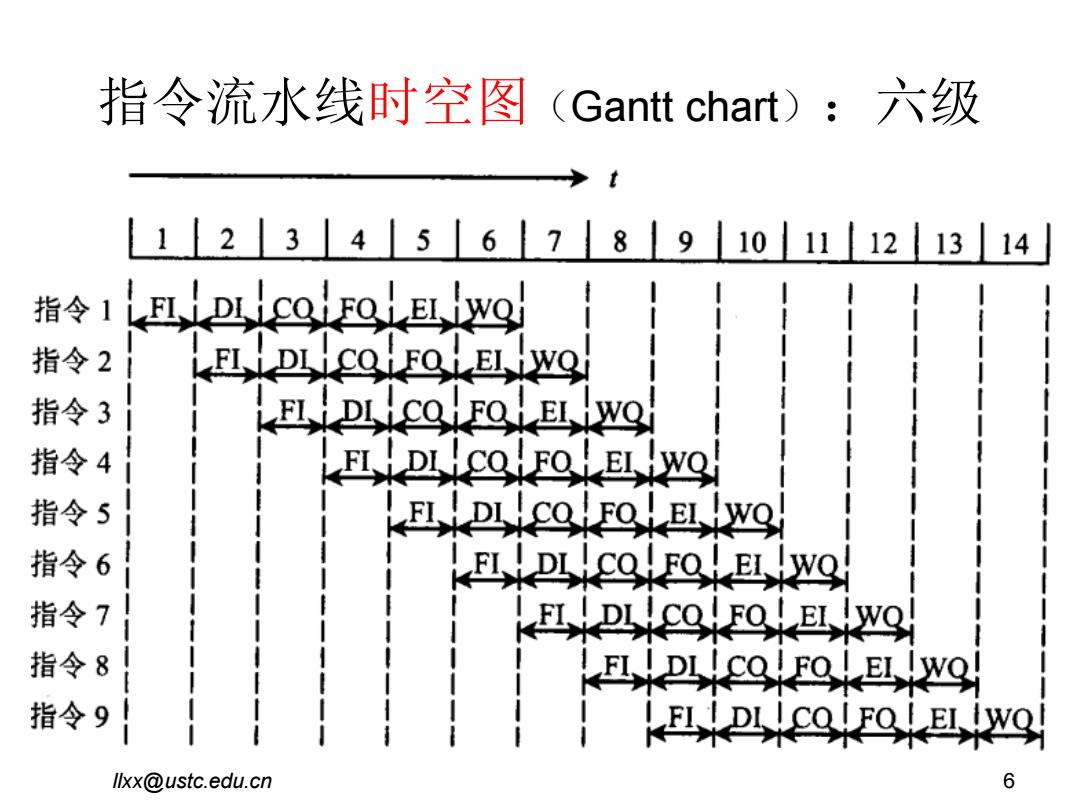

指令流水线时空图(Gantt chart):六级 1L234567891011121314 指令1巴,lp9 指令2 指令3 指令4 Lplc9FoE画wg 指令5 FI DI COFOL EL WO 指令6 E巴PLlC9ELwo 指令7 FL DIICOLFO EL WO 指令8 {D49马w9 指令9 4P449404马y llxx@ustc.edu.cn 6

llxx@ustc.edu.cn 6 指令流水线时空图(Gantt chart):六级