The Processor Implementation: Datapath Control “Computer Organization&Design” 第四章

The Processor Implementation: Datapath & Control “Computer Organization & Design ” 第四章

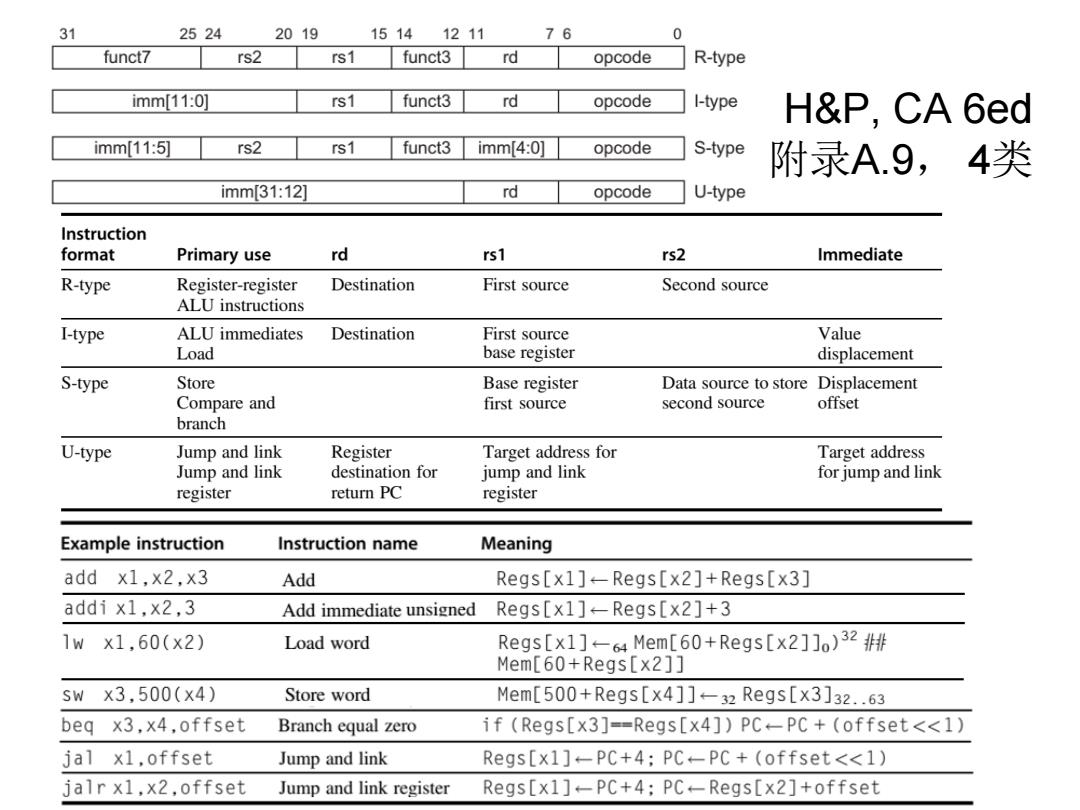

31 2524 2019 1514 1211 76 0 funct7 rs2 rs1 funct3 rd opcode R-type imm[11:0] rs1 funct3 rd opcode I-type H&P.CA 6ed imm[11:5可 rs2 rs1 funct3 imm[4:0] opcode S-type 附录A.9,4类 imm[31:12] rd opcode U-type Instruction format Primary use rd rs1 rs2 Immediate R-type Register-register Destination First source Second source ALU instructions I-type ALU immediates Destination First source Value Load base register displacement S-type Store Base register Data source to store Displacement Compare and first source second source offset branch U-type Jump and link Register Target address for Target address Jump and link destination for jump and link for jump and link register return PC register Example instruction Instruction name Meaning add x1,x2,x3 Add Regs[x1]-Regs[x2]+Regs[x3] addi x1,x2,3 Add immediate unsigned Regs[x1]-Regs[x2]+3 lw x1,60(x2) Load word Regs [x1]-64 Mem[60+Regs [x2]])32 Mem[60+Regs[x2]] swx3,500(x4) Store word Mem[500+Regs[x4]]-32Regs[x3]32.63 beq x3,x4,offset Branch equal zero if (Regs[x3]=-Regs[x4])PC--PC+(offset<<1) jal xl,offset Jump and link Regs[x1]-PC+4;PC-PC+(offset<<1) jalr x1.x2,offset Jump and link register Regs[x1]-PC+4:PC--Regs[x2]+offset

H&P, CA 6ed 附录A.9, 4类

微结构:数据通路,控制器 EPROM RAM Cs CS A9 A0-A8 A9 A0-A8 Address Bus n Data Bus m PROCESSOR RD WR Control Signals 内存,Io Data& Control Arithmetic Internal Unit Logic Unit data bus Addr Input Registers Instruction Op&BEN&mode Decoder 控制单元 数据通路 (执行单元) Control Signals Control Signals

微结构:数据通路,控制器

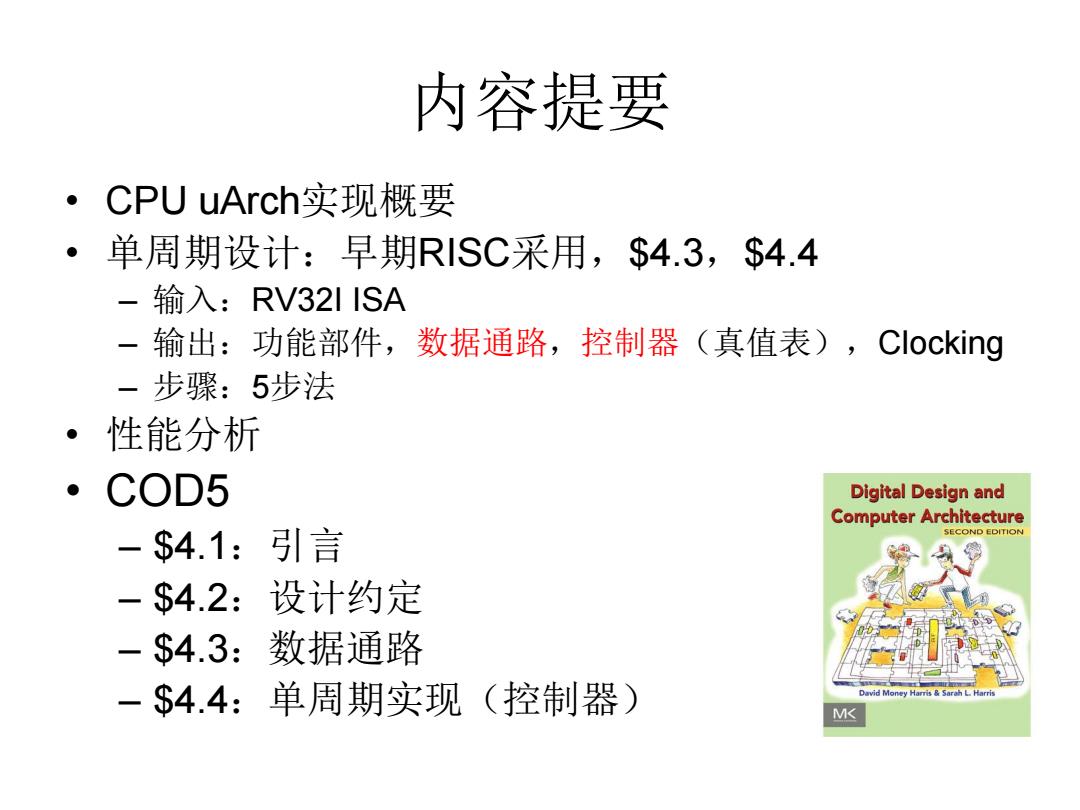

内容提要 ●( CPU uArch实现概要 ● 单周期设计:早期RISC采用,$4.3,$4.4 -输入:RV32IISA -输出:功能部件,数据通路,控制器(真值表),Clocking -步骤:5步法 性能分析 COD5 Digital Design and Computer Architecture -$4.1:引言 SECOND EDITION 一 $4.2:设计约定 一 $4.3:数据通路 一$4.4:单周期实现(控制器) M<

内容提要 • CPU uArch实现概要 • 单周期设计:早期RISC采用,$4.3,$4.4 – 输入:RV32I ISA – 输出:功能部件,数据通路,控制器(真值表),Clocking – 步骤:5步法 • 性能分析 • COD5 – $4.1:引言 – $4.2:设计约定 – $4.3:数据通路 – $4.4:单周期实现(控制器)

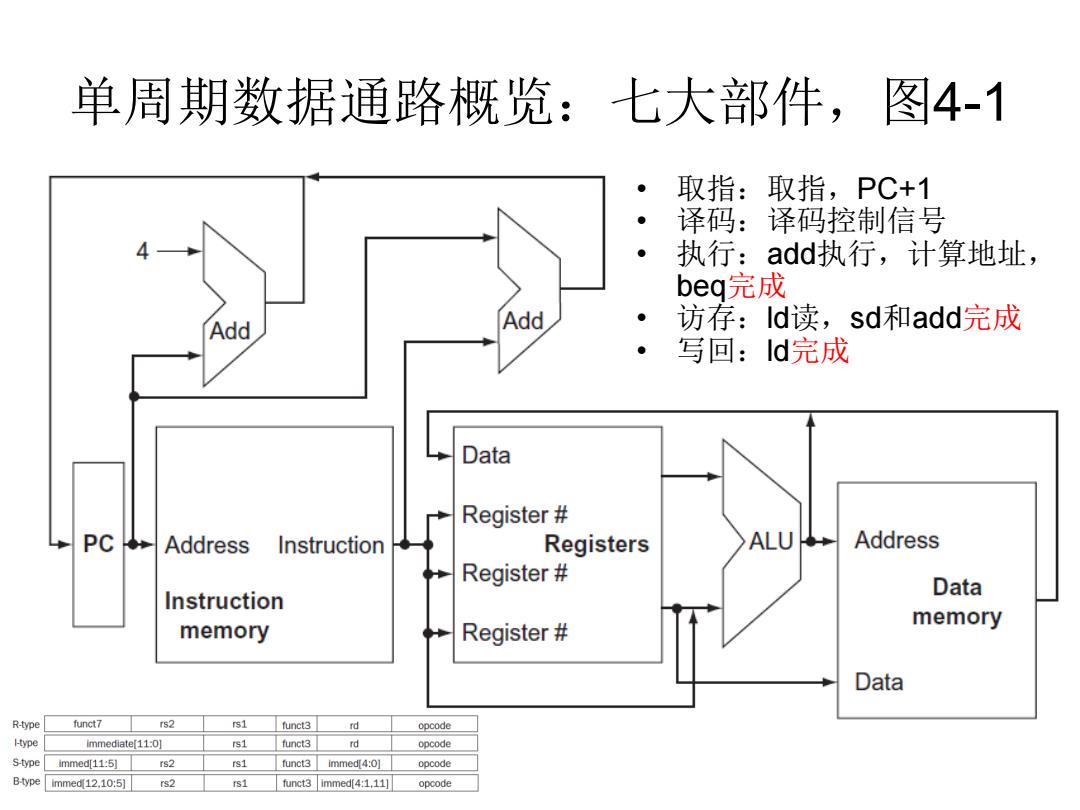

单周期数据通路概览:七大部件,图4-1 取指:取指,PC+1 译码:译码控制信号 执行:add执行,计算地址, beq完成 Add ● Add 访存:ld读,sd和add完成 写回:d完成 Data Register PC Address Instruction Registers ALU Address Register Data Instruction memory memory Register Data R-type funct7 r52 rs1 funct3 rd opcode I-type immediate[11:0] rs1 funct3 rd opcode S-type immed[11:5] rs2 rs1 funct3 immed[4:0] opcode B-type mmed12.10:5] rs2 rs1 funct3 immed(4:1,11] opcode

单周期数据通路概览:七大部件,图4-1 • 取指:取指,PC+1 • 译码:译码控制信号 • 执行:add执行,计算地址, beq完成 • 访存:ld读,sd和add完成 • 写回:ld完成