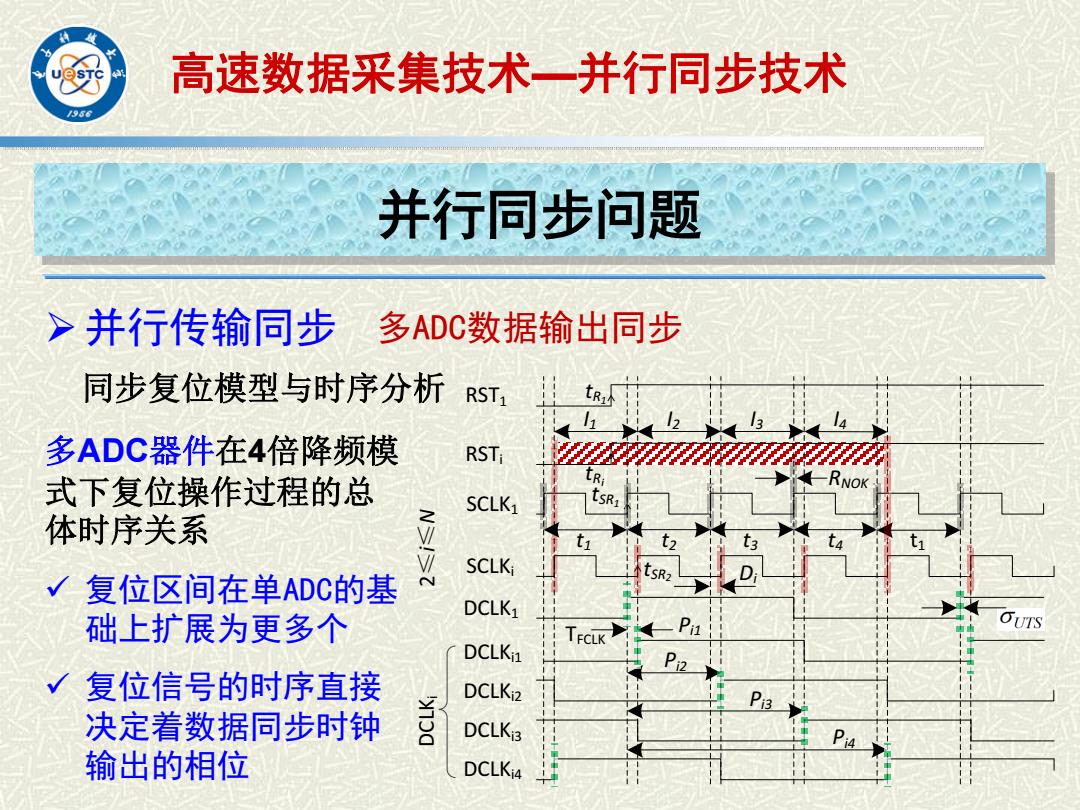

高速数据采集技术一并行同步技术 198 并行同步问题 >并行传输同步 多ADC数据输出同步 同步复位模型与时序分析 RST: 多ADC器件在4倍降频模 RSTi 弟我 式下复位操作过程的总 RNOK SCLK1 体时序关系 SCLKi √复位区间在单ADC的基 DCLK1 础上扩展为更多个 OUTS TFCLK DCLKin 复位信号的时序直接 DCLKi2 决定着数据同步时钟 DCLKi3 P 输出的相位 DCLKi4

并行同步问题 高速数据采集技术—并行同步技术 并行传输同步 多ADC数据输出同步 同步复位模型与时序分析 多ADC器件在4倍降频模 式下复位操作过程的总 体时序关系 复位区间在单ADC的基 础上扩展为更多个 复位信号的时序直接 决定着数据同步时钟 输出的相位 DCLK1 DCLKi1 RSTi tR tSR t2 t3 t4 t1 SCLK1 tSR SCLKi RNOK t1 I1 I2 I3 I4 Pi1 Pi2 Pi3 Pi4 TFCLK DCLKi2 DCLKi3 DCLKi4 DCLKi 2≤i≤N 1 2 RST1 tR1 i Di

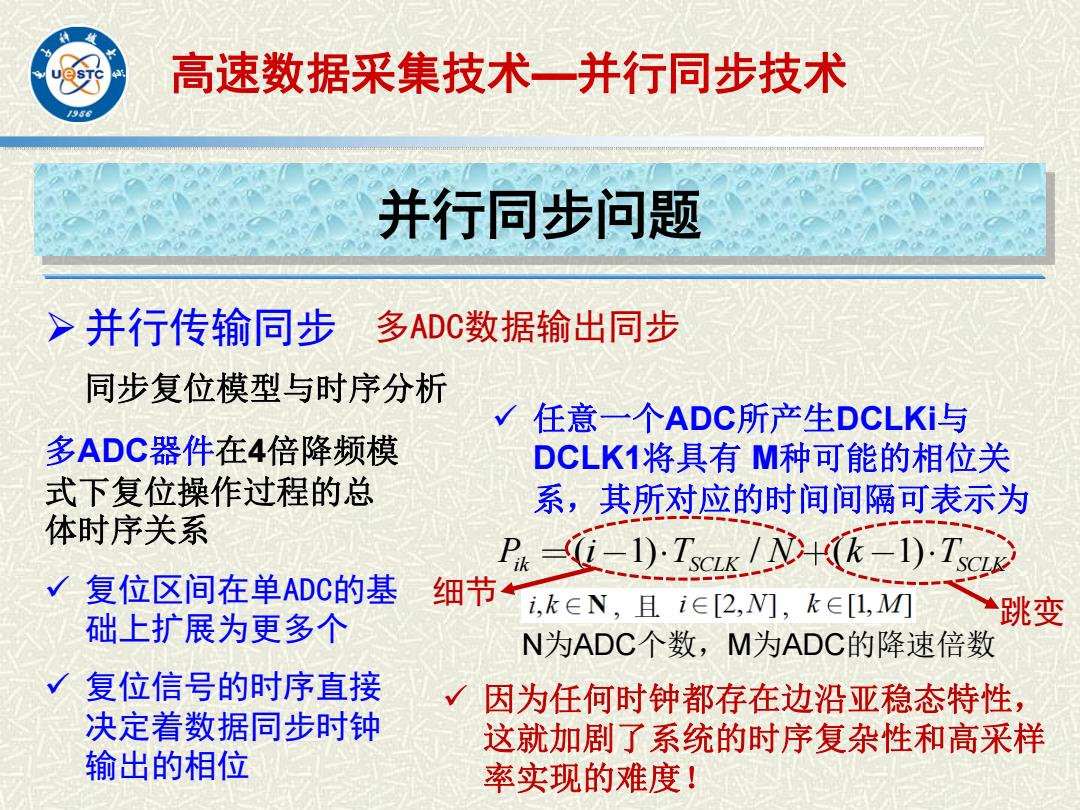

高速数据采集技术一并行同步技术 198 并行同步问题 >并行传输同步 多ADC数据输出同步 同步复位模型与时序分析 任意一个ADC所产生DCLKi与 多ADC器件在4倍降频模 DCLK1将具有M种可能的相位关 式下复位操作过程的总 系,其所对应的时间间隔可表示为 体时序关系 复位区间在单ADC的基 细节 i,k∈N,且i∈[2,W],k∈[1,M 础上扩展为更多个 跳变 N为ADC个数,M为ADC的降速倍数 复位信号的时序直接 因为任何时钟都存在边沿亚稳态特性, 决定着数据同步时钟 这就加剧了系统的时序复杂性和高采样 输出的相位 率实现的难度!

并行同步问题 高速数据采集技术—并行同步技术 并行传输同步 多ADC数据输出同步 同步复位模型与时序分析 多ADC器件在4倍降频模 式下复位操作过程的总 体时序关系 复位区间在单ADC的基 础上扩展为更多个 复位信号的时序直接 决定着数据同步时钟 输出的相位 任意一个ADC所产生DCLKi与 DCLK1将具有 M种可能的相位关 系,其所对应的时间间隔可表示为 ( 1) / ( 1) P i T N k T ik SCLK SCLK N为ADC个数,M为ADC的降速倍数 因为任何时钟都存在边沿亚稳态特性, 这就加剧了系统的时序复杂性和高采样 率实现的难度! 细节 跳变