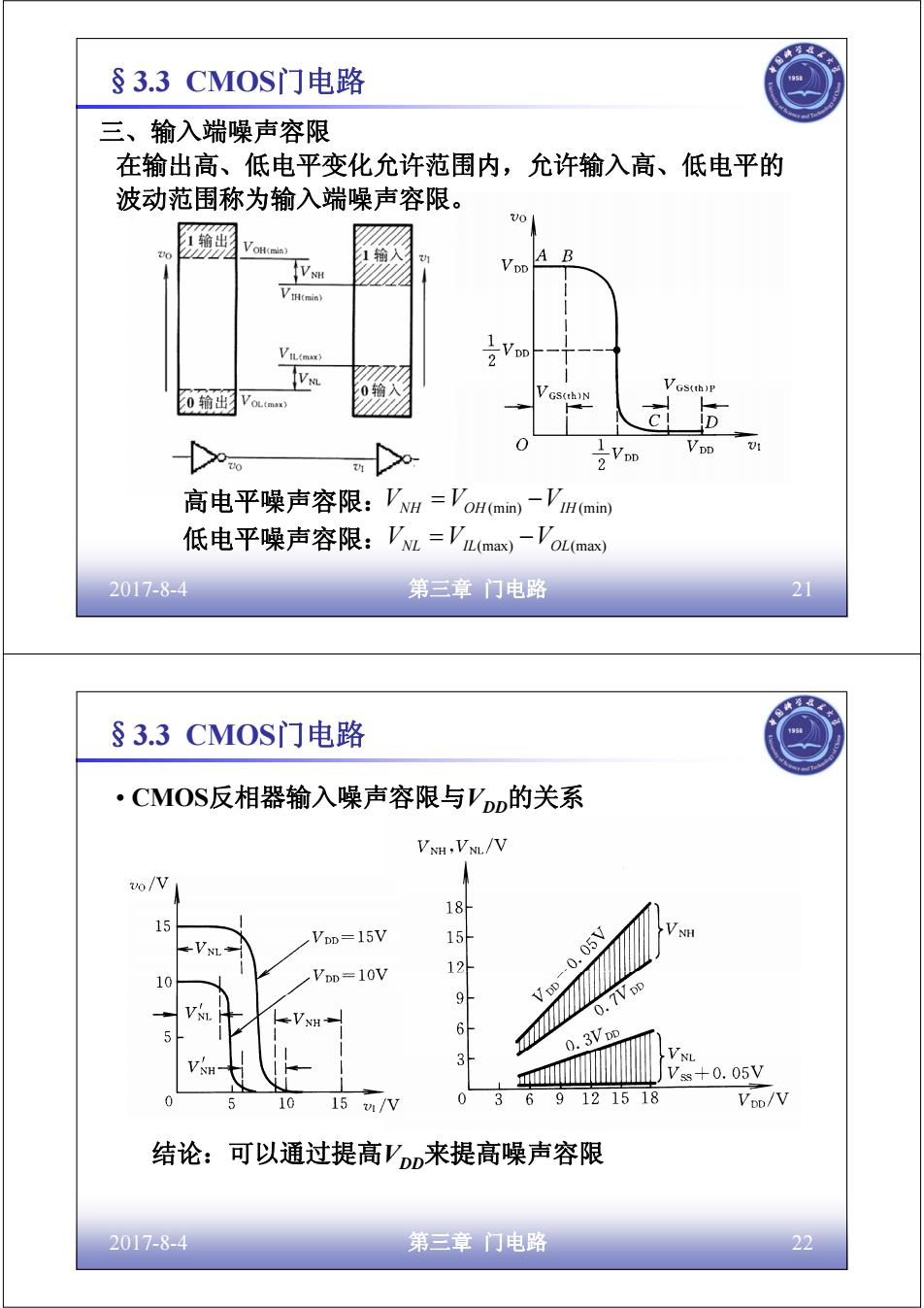

§3.3CMOS门电路 三、输入端噪声容限 在输出高、低电平变化允许范围内,允许输入高、低电平的 波动范围称为输入端噪声容限。 1输出 OH(min) 1输入 VoD VIL(mae) 0输出 0输入 VGs(th)N Vostth)P VoL(max) VDD 2 高电平噪声容限:V=(min-VHmm 低电平噪声容限:'z='umax-Vom 2017-8-4 第三章门电路 21 §3.3 CMOS门电路 ·CMOS反相器输入噪声容限与VoD的关系 VNH,VNL/V vo/V 18 15 VNL VDD=15V 15 10 Vpp=10V 12 9 Vm-0.05V 0.7VpD VNH- 6 0.3V pD 3 VNL Vss+0.05V 10 15/V 0 3 6 9 121518 VoD/V 结论:可以通过提高VoD来提高噪声容限 2017-8-4 第三章门电路 22

2017-8-4 第三章 门电路 21 三、输入端噪声容限 VNH =VOH (min) −VIH (min) §3.3 CMOS门电路 在输出高、低电平变化允许范围内,允许输入高、低电平的 波动范围称为输入端噪声容限。 VNL =VIL(max) −VOL(max) 高电平噪声容限: 低电平噪声容限: 2017-8-4 第三章 门电路 22 结论:可以通过提高VDD来提高噪声容限 §3.3 CMOS门电路 • CMOS反相器输入噪声容限与VDD的关系

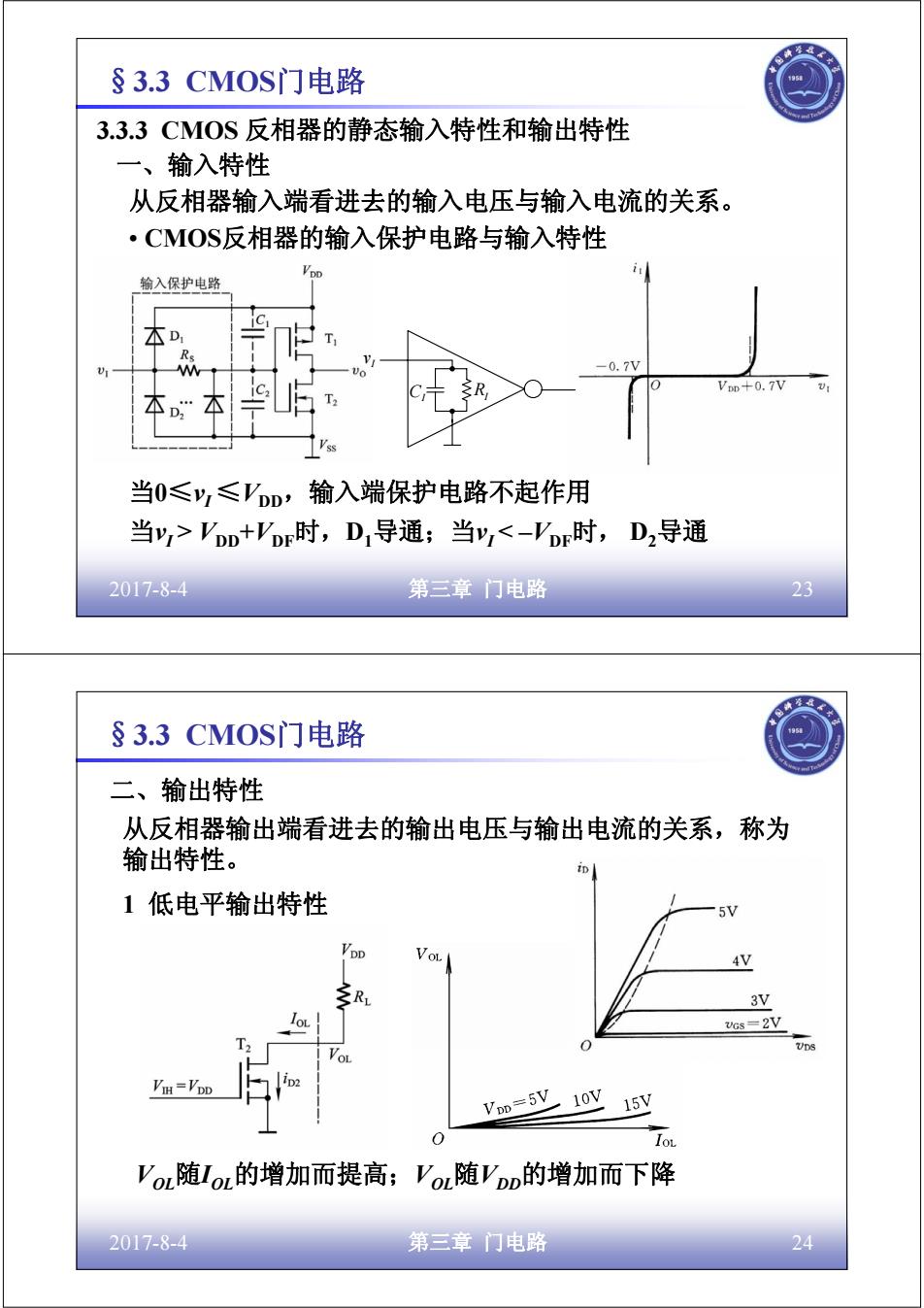

§3.3 CMOS门电路 3.3.3CMOS反相器的静态输入特性和输出特性 一、输入特性 从反相器输入端看进去的输入电压与输入电流的关系。 ·CMOS反相器的输入保护电路与输入特性 输入保护电路 -0.7V VDD+0.7V 当0≤y,≤VD,输入端保护电路不起作用 当y,>VoD+Vor时,D导通;当y<-Vor时,D2导通 2017-8-4 第三章门电路 23 §3.3 CMOS门电路 二、输出特性 从反相器输出端看进去的输出电压与输出电流的关系,称为 输出特性。 D 1低电平输出特性 VoD 4V 乏R 3V vGs=2V VIH=VDD VpD=5V 10V 15V VoL随IoL的增加而提高;Vo随VoD的增加而下降 2017-8-4 第三章门电路 24

2017-8-4 第三章 门电路 23 3.3.3 CMOS 反相器的静态输入特性和输出特性 §3.3 CMOS门电路 一、输入特性 • CMOS反相器的输入保护电路与输入特性 当0≤vI ≤VDD,输入端保护电路不起作用 从反相器输入端看进去的输入电压与输入电流的关系。 CI RI I v 当vI > VDD+VDF时,D1导通;当vI < –VDF时, D2导通 2017-8-4 第三章 门电路 24 §3.3 CMOS门电路 二、输出特性 1 低电平输出特性 从反相器输出端看进去的输出电压与输出电流的关系,称为 输出特性。 VOL随IOL的增加而提高;VOL随VDD的增加而下降

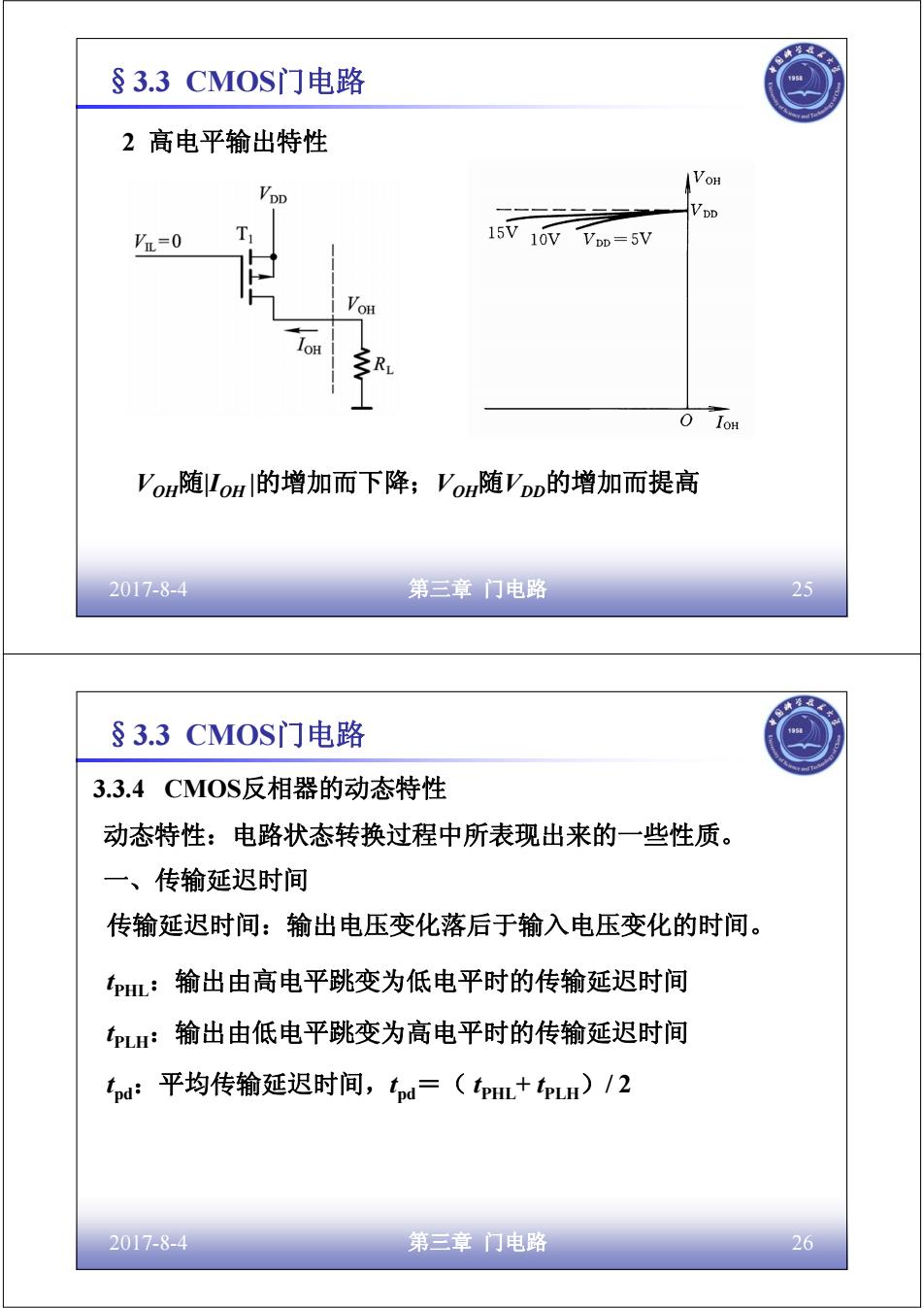

§3.3CMOS门电路 2高电平输出特性 VpD VoH 'm=0 T 15V10V VDD=5V VoH IoH Voa随oH的增加而下降;VoH随VoD的增加而提高 2017-8-4 第三章门电路 25 §3.3CMOS门电路 3.3.4CM0S反相器的动态特性 动态特性:电路状态转换过程中所表现出来的一些性质。 一、传输延迟时间 传输延迟时间:输出电压变化落后于输入电压变化的时间。 :输出由高电平跳变为低电平时的传输延迟时间 H:输出由低电平跳变为高电平时的传输延迟时间 tpd:平均传输延迟时间,tpa=(p+pLH)/2 2017-8-4 第三章门电路 26

2017-8-4 第三章 门电路 25 §3.3 CMOS门电路 2 高电平输出特性 VOH随|IOH |的增加而下降;VOH随VDD的增加而提高 2017-8-4 第三章 门电路 26 §3.3 CMOS门电路 3.3.4 CMOS反相器的动态特性 一、传输延迟时间 动态特性:电路状态转换过程中所表现出来的一些性质。 传输延迟时间:输出电压变化落后于输入电压变化的时间。 tPHL:输出由高电平跳变为低电平时的传输延迟时间 tPLH:输出由低电平跳变为高电平时的传输延迟时间 tpd:平均传输延迟时间,tpd=( tPHL+ tPLH)/ 2

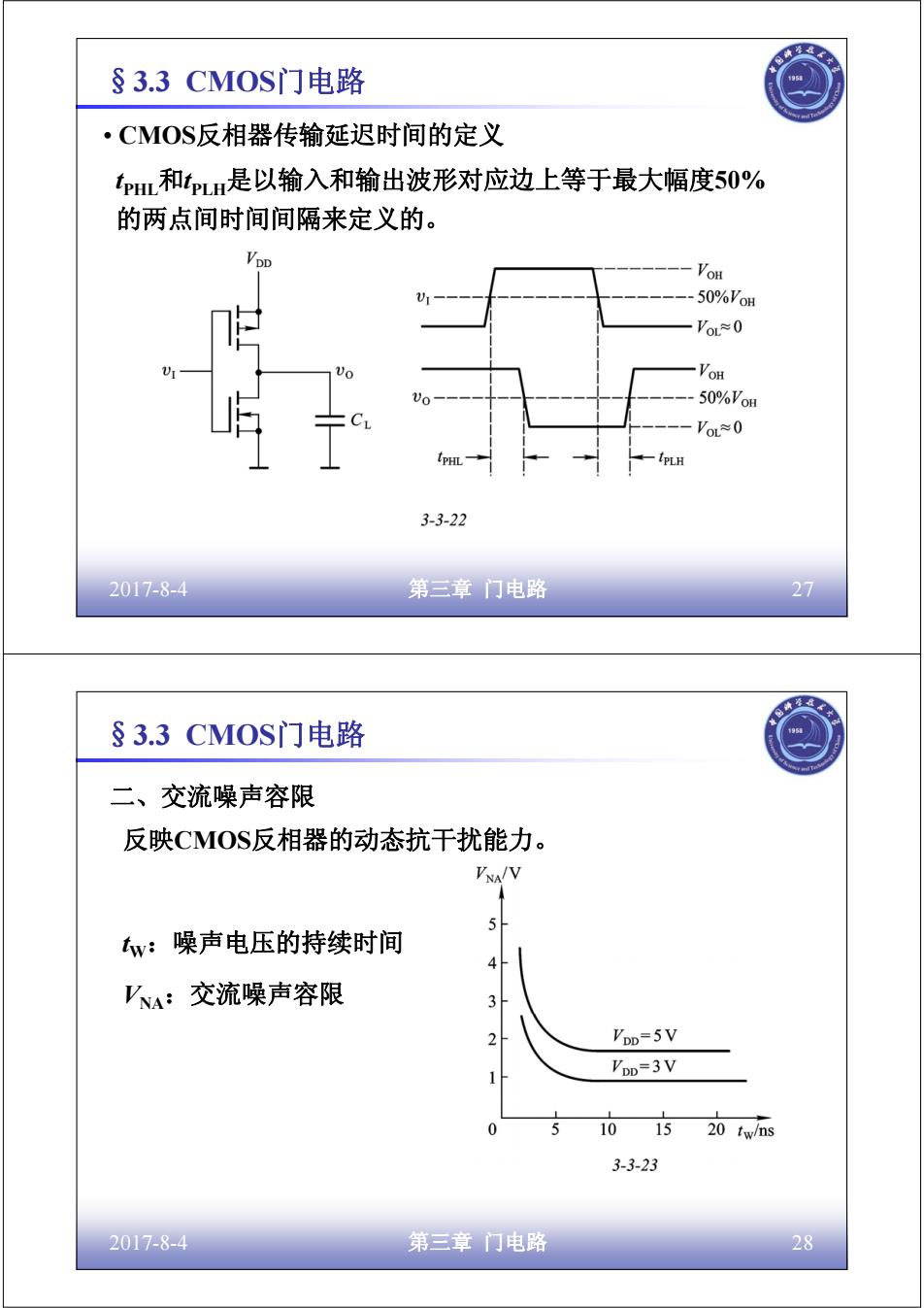

§3.3 CMOS门电路 ·CMOS反相器传输延迟时间的定义 和H是以输入和输出波形对应边上等于最大幅度50% 的两点间时间间隔来定义的。 VoH 50%VoH Vo≈0 -VOH 50%'o细 'o≈0 PHL PLH 3-3-22 2017-8-4 第三章门电路 27 §3.3 CMOS门电路 二、交流噪声容限 反映CMOS反相器的动态抗干扰能力。 VNA/V 5 w:噪声电压的持续时间 4 VA:交流噪声容限 3 2 VDD=5V VDD=3V 101520twns 3-3-23 2017-8-4 第三章门电路 28

2017-8-4 第三章 门电路 27 §3.3 CMOS门电路 • CMOS反相器传输延迟时间的定义 tPHL和tPLH是以输入和输出波形对应边上等于最大幅度50% 的两点间时间间隔来定义的。 2017-8-4 第三章 门电路 28 §3.3 CMOS门电路 二、交流噪声容限 反映CMOS反相器的动态抗干扰能力。 tW:噪声电压的持续时间 VNA:交流噪声容限

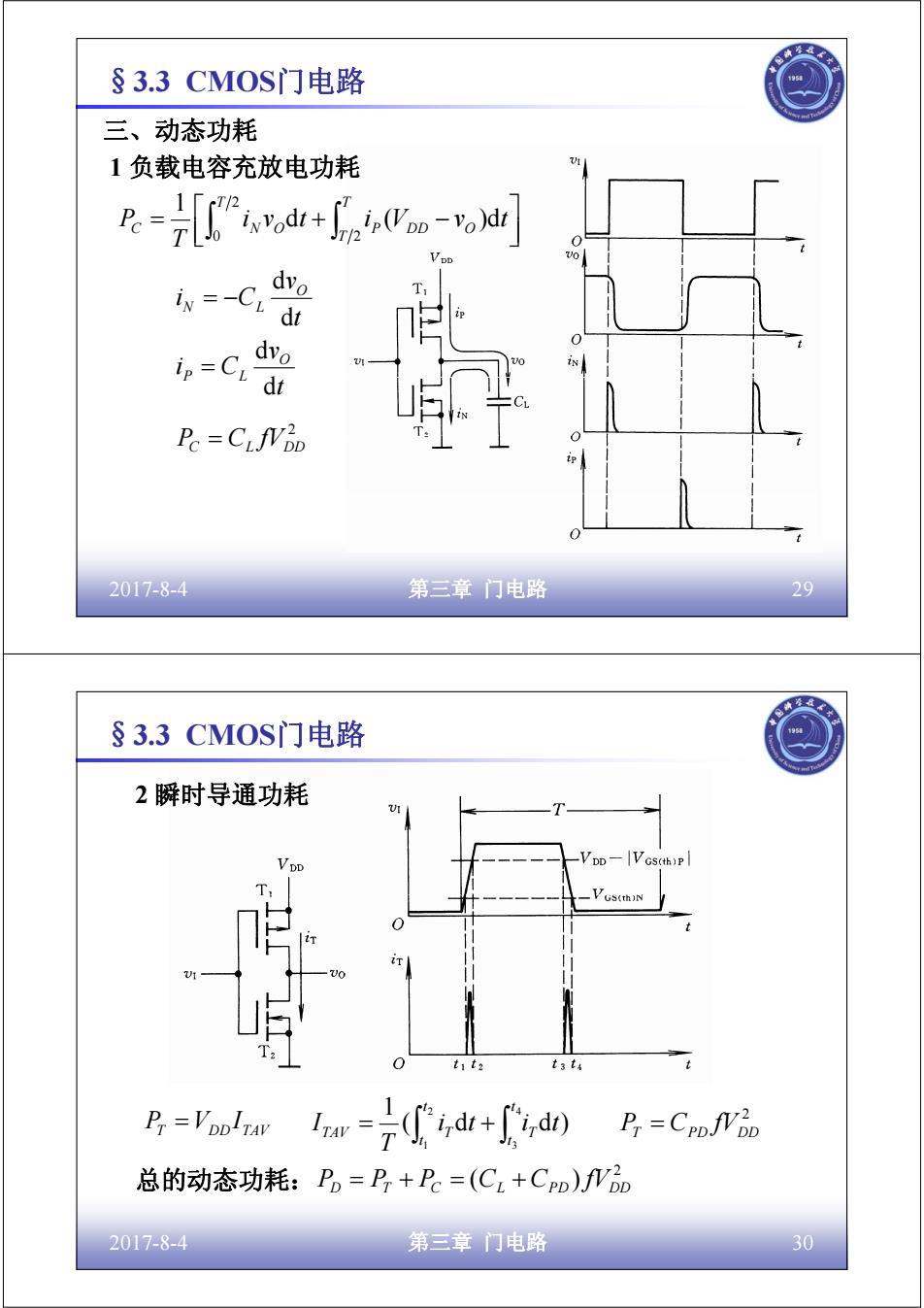

§3.3CMOS门电路 三、动态功耗 1负载电容充放电功耗 Pdodt dvo ix =-C dr T dvo ip=CL dt Pe=CL.fVbD 2017-8-4 第三章门电路 29 §3.3CMOS门电路 2瞬时导通功耗 -VDD-VGscth)Pl t3 ta t P =VDDlTAv 1w=7d+,d0)1 P:=Cpp.fVip 总的动态功耗:P。=P+P=(CL+Cpp)fo 2017-8-4 第三章门电路 30

2017-8-4 第三章 门电路 29 §3.3 CMOS门电路 三、动态功耗 1 负载电容充放电功耗 ⎥⎦ ⎤ ⎢⎣ ⎡ = + − ∫ ∫ 2 0 2 d ( )d 1 T T T C N O P DD O i v t i V v t T P t v i C t v i C O P L O N L d d d d = = − 2 C L DD P = C fV 2017-8-4 第三章 门电路 30 T DD TAV P =V I §3.3 CMOS门电路 2 瞬时导通功耗 ( d d ) 1 2 1 4 3 ∫ ∫ = + t t t t TAV T T i t i t T I 2 T PD DD P = C fV 2 ( ) D T C L PD DD 总的动态功耗:P = P + P = C +C fV