中国绅学我术大学 University of Science and Technology of China 第五章半导体存储电路 本章目录 >5.1概述 >5.2SR锁存器 >5.3触发器 >5.4寄存器 >5.5存储器 2017-9-3 第五章半导体存储电路 §5.1概述 © 1存储电路 •存储单元:只能存储一位数据的电路: •寄存器:存储一组数据的存储电路; •存储器:存储大量数据的存储电路。 2存储单元分类 一静态存储单元 由门电路连接而成,包括各种结构的锁存器和触发器, 利用正反馈原理存储数据。 动态存储单元 利用电容的电荷存储效应存储数据。 2017-9-3 第五章半导体存储电路 2

2017-9-3 第五章 半导体存储电路 1 第五章 半导体存储电路 第五章 半导体存储电路 本章目录 ¾5.1 概述 ¾5.2 SR锁存器 ¾5.3 触发器 ¾5.4 寄存器 ¾5.5 存储器 2017-9-3 第五章 半导体存储电路 2 §5.1 概述 •存储单元:只能存储一位数据的电路; •寄存器:存储一组数据的存储电路; •存储器:存储大量数据的存储电路。 2 存储单元分类 ——静态存储单元 由门电路连接而成,包括各种结构的锁存器和触发器, 利用正反馈原理存储数据。 ——动态存储单元 利用电容的电荷存储效应存储数据。 1 存储电路

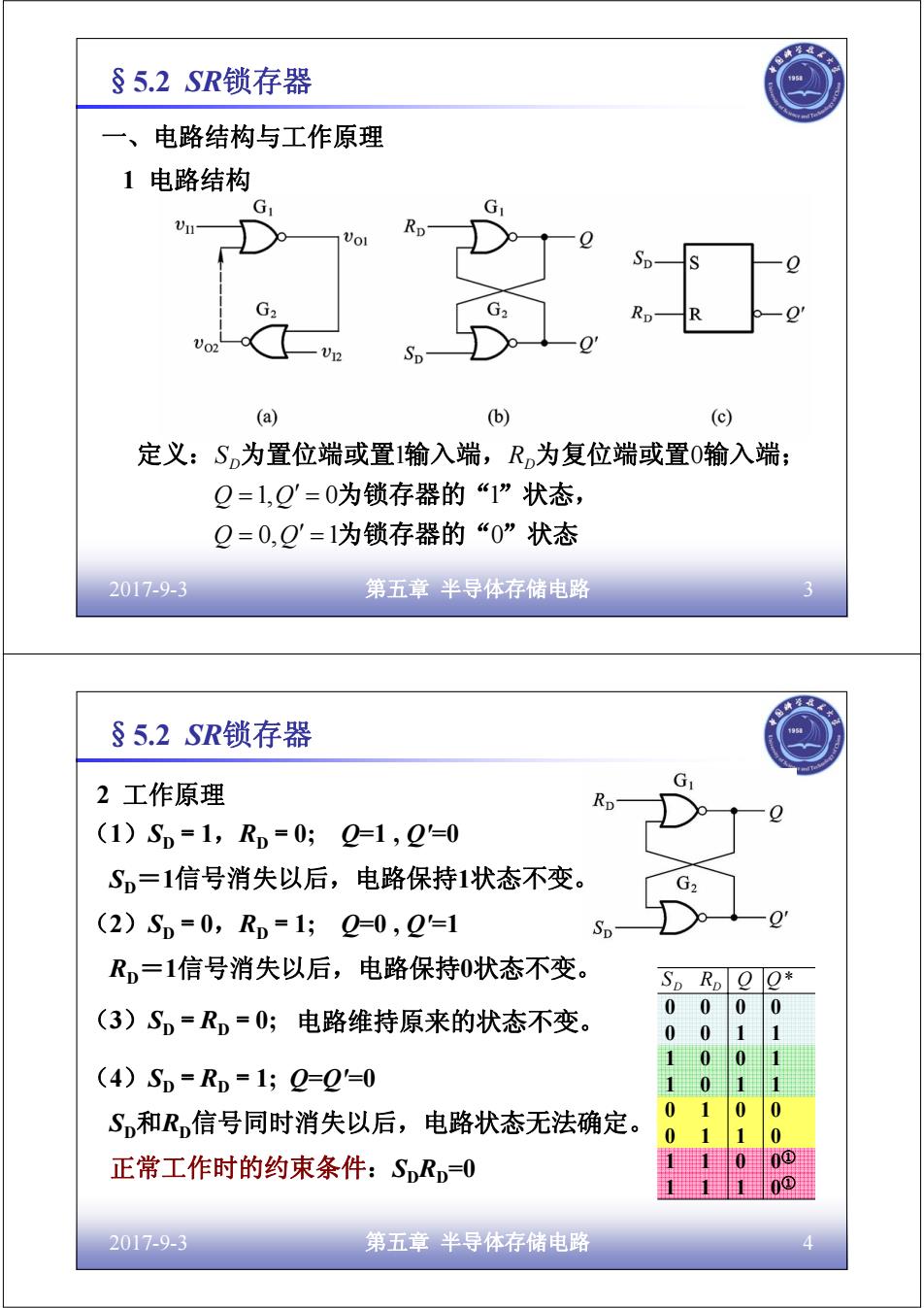

§5.2SR锁存器 一、电路结构与工作原理 1电路结构 G vu- Rp G2 G2 Rp U12 (a) (b) (c) 定义:S,为置位端或置1输入端,R,为复位端或置0输入端; Q=1,Q'=0为锁存器的“1”状态, Q=0,Q'=1为锁存器的“0”状态 2017-9-3 第五章半导体存储电路 §5.2SR锁存器 2工作原理 G Rp (1)SD=1,RD=0;Q=1,2'=0 S,=1信号消失以后,电路保持1状态不变。 (2)SD=0,RD=1;Q=0,2=1 Sp R,=1信号消失以后,电路保持0状态不变。 Sp 000 0 (3)SD=RD=0;电路维持原来的状态不变。 00 0 (4)S=Rn=1;Q=2'=0 10 S和R,信号同时消失以后,电路状态无法确定。 0 0 0 正常工作时的约束条件:SDRD=0 2017-9-3 第五章半导体存储电路

2017-9-3 第五章 半导体存储电路 3 §5.2 SR锁存器 一、电路结构与工作原理 1 电路结构 为锁存器的“ ”状态 为锁存器的“ ”状态, 定义: 为置位端或置 输入端, 为复位端或置 输入端; 0, 1 0 1, 0 1 1 0 = ′ = = ′ = Q Q Q Q SD RD 2017-9-3 第五章 半导体存储电路 4 §5.2 SR锁存器 2 工作原理 (1)SD=1,RD=0; Q=1 , Q'=0 SD=1信号消失以后,电路保持1状态不变。 (2)SD=0,RD=1; Q=0 , Q'=1 RD=1信号消失以后,电路保持0状态不变。 (3)SD=RD=0; 电路维持原来的状态不变。 (4)SD=RD=1; Q=Q'=0 SD和RD信号同时消失以后,电路状态无法确定。 正常工作时的约束条件:SDRD=0 0 0 1 1 1 1 1 0① 1 1 0 0① 0 1 1 0 0 1 0 0 1 0 1 1 1 0 0 1 0 0 0 0 SD RD Q Q*

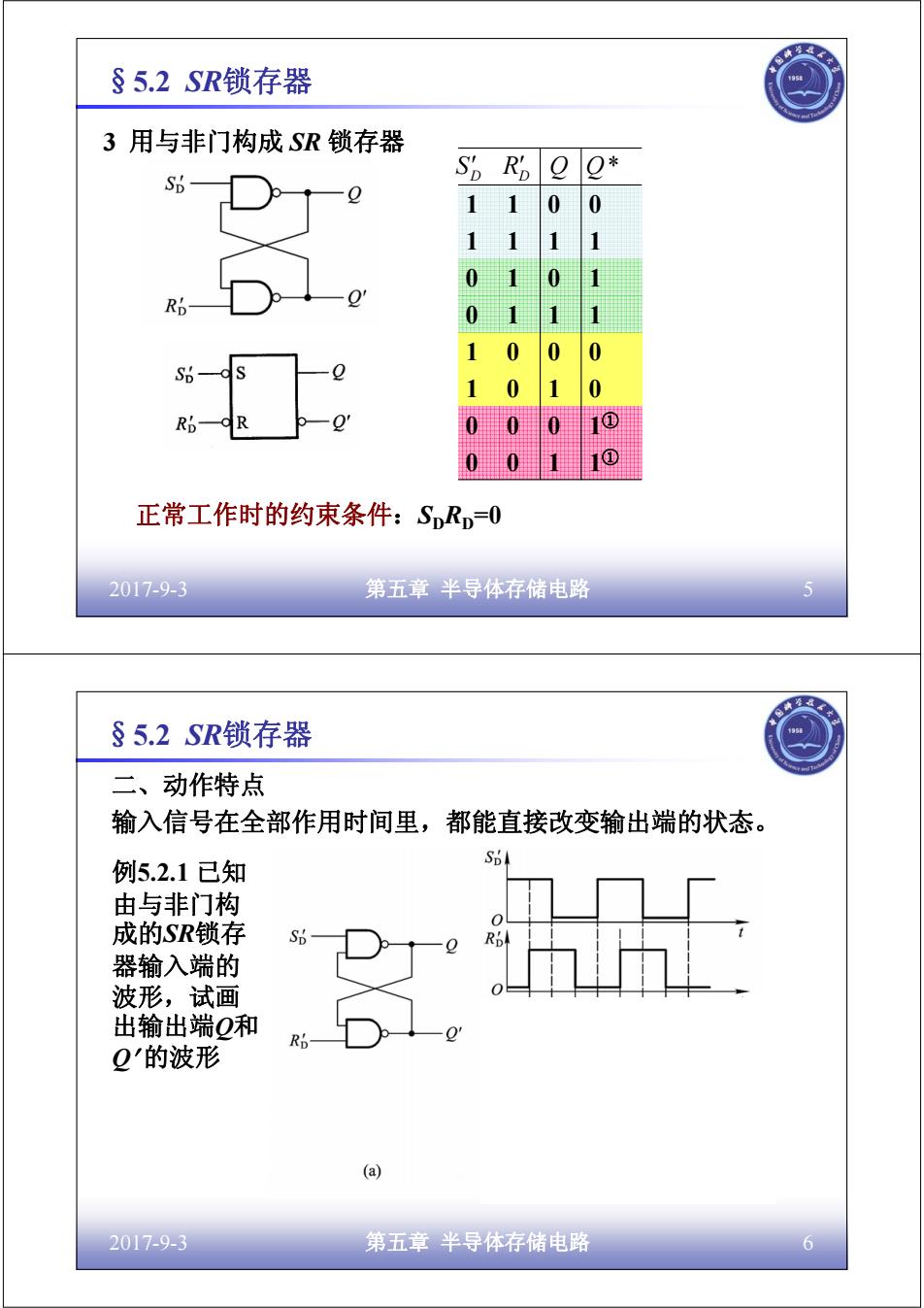

§5.2SR锁存器 3用与非门构成SR锁存器 Sp Rp Q O* 1 1 0 0 1 1 0 0 1 0 0 0 正常工作时的约束条件:SDRD=0 2017-9-3 第五章半导体存储电路 §5.2SR锁存器 二、动作特点 输入信号在全部作用时间里,都能直接改变输出端的状态。 例5.2.1已知 SB 由与非门构 成的SR锁存 Sp 器输入端的 波形,试画 出输出端Q和 Q'的波形 (a) 2017-9-3 第五章半导体存储电路

2017-9-3 第五章 半导体存储电路 5 §5.2 SR锁存器 3 用与非门构成 SR 锁存器 1 1 1 1 0 0 1 1① 0 0 0 1① 1 0 1 0 1 0 0 0 0 1 1 1 0 1 0 1 1 1 0 0 S R Q Q* D D ′ ′ 正常工作时的约束条件:SDRD=0 2017-9-3 第五章 半导体存储电路 6 二、动作特点 输入信号在全部作用时间里,都能直接改变输出端的状态。 例5.2.1 已知 由与非门构 成的SR锁存 器输入端的 波形,试画 出输出端Q和 Q′ 的波形 0 §5.2 SR锁存器

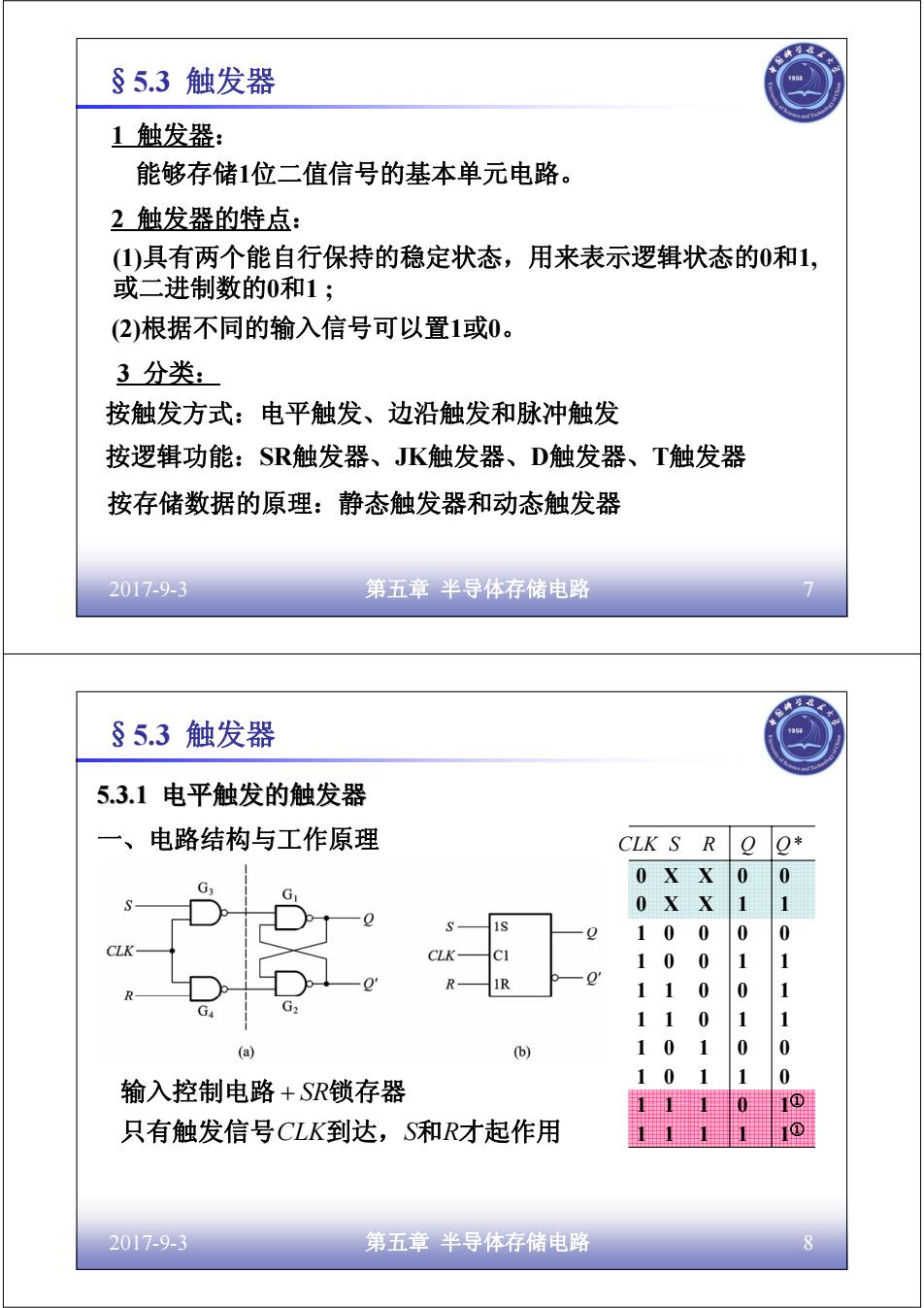

§5.3 触发器 1触发器: 能够存储1位二值信号的基本单元电路。 2触发器的特点: (1)具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1, 或二进制数的0和1; (2)根据不同的输入信号可以置1或0。 3分类: 按触发方式:电平触发、边沿触发和脉冲触发 按逻辑功能:S触发器、JK触发器、D触发器、T触发器 按存储数据的原理:静态触发器和动态触发器 2017-9-3 第五章半导体存储电路 §5.3 触发器 5.3.1电平触发的触发器 一、电路结构与工作原理 CLK S R Q O* 0 XX 0 0 0XX 1■ 1 10 0 0 0 CLK CLK- CI 10 0 1 1 R 1R 11 0 0 1 0 1 (a) (b) 1 0 1 0 0 0 0 输入控制电路+SR锁存器 1 只有触发信号CLK到达,S和R才起作用 2017-9-3 第五章半导体存储电路 8

2017-9-3 第五章 半导体存储电路 7 能够存储1位二值信号的基本单元电路。 (2)根据不同的输入信号可以置1或0。 3 分类: 2 触发器的特点: 1 触发器: (1)具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1, 或二进制数的0和1 ; 按触发方式:电平触发、边沿触发和脉冲触发 按逻辑功能:SR触发器、JK触发器、D触发器、T触发器 按存储数据的原理:静态触发器和动态触发器 §5.3 触发器 2017-9-3 第五章 半导体存储电路 8 一、电路结构与工作原理 0 X X 0 0 0 X X 1 1 1 1 0 0 1 1 0 0 1 0 1 1 1 1 1 1① 1 1 0 1① 1 1 1 0 1 1 0 0 1 0 1 1 1 0 0 1 1 0 0 0 CLK S R Q Q* 只有触发信号 到达, 和 才起作用 输入控制电路 锁存器 CLK S R + SR §5.3 触发器 5.3.1 电平触发的触发器

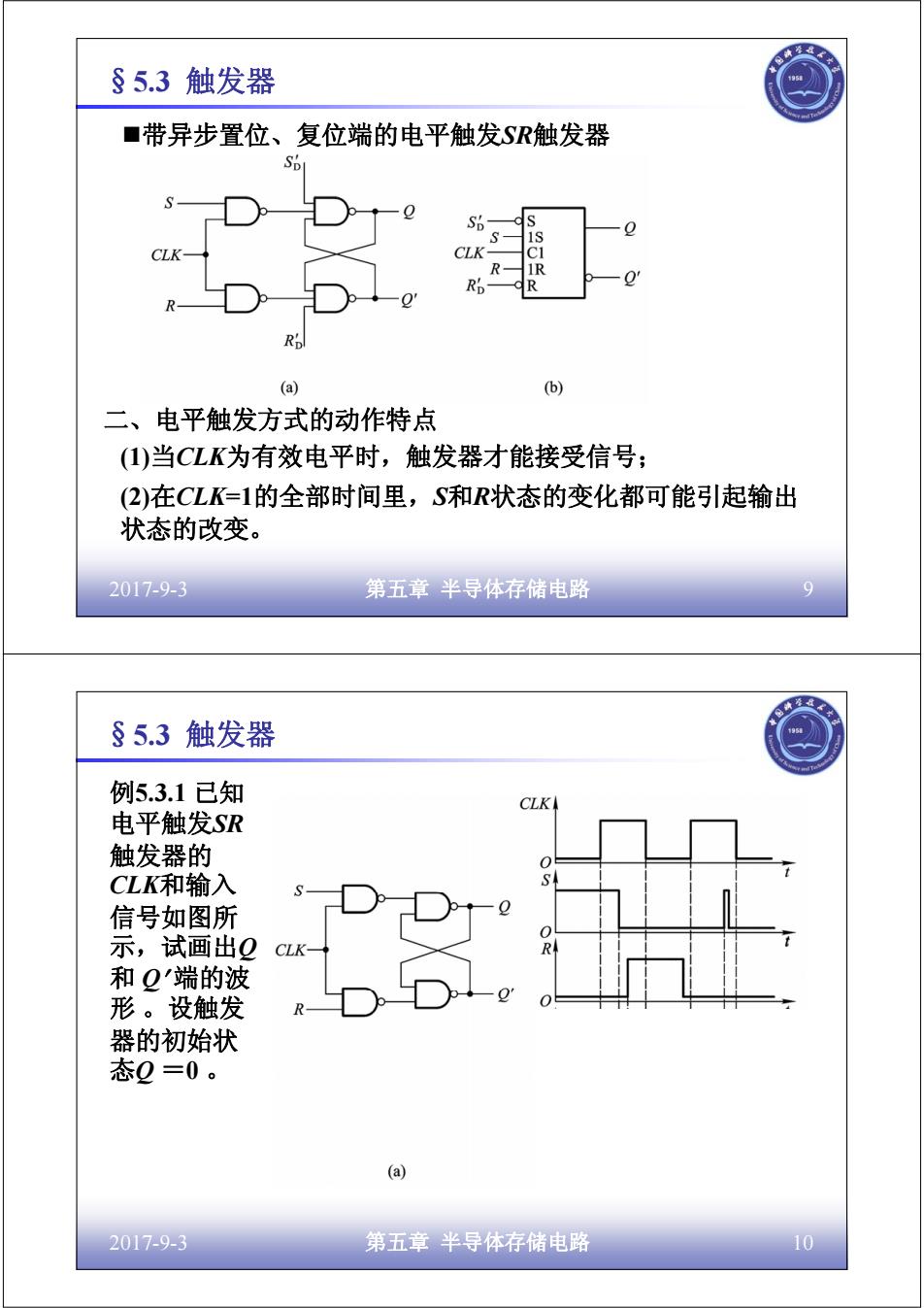

§5.3 触发器 ■带异步置位、复位端的电平触发SR触发器 So Sp S 1S LK CLK- R R (a) (b) 二、电平触发方式的动作特点 (1)当CLK为有效电平时,触发器才能接受信号; (2)在CLK=1的全部时间里,S和R状态的变化都可能引起输出 状态的改变。 2017-9-3 第五章半导体存储电路 §5.3 触发器 例5.3.1已知 CLK 电平触发SR 触发器的 CLK和输入 信号如图所 示,试画出2 CLK 和Q'端的波 形。设触发 器的初始状 态Q=0。 (a) 2017-9-3 第五章半导体存储电路 10

2017-9-3 第五章 半导体存储电路 9 带异步置位、复位端的电平触发SR触发器 二、电平触发方式的动作特点 (1)当CLK为有效电平时,触发器才能接受信号; (2)在CLK=1的全部时间里,S和R状态的变化都可能引起输出 状态的改变。 §5.3 触发器 2017-9-3 第五章 半导体存储电路 10 例5.3.1 已知 电平触发SR 触发器的 CLK和输入 信号如图所 示,试画出Q 和 Q′ 端的波 形 。设触发 器的初始状 态Q =0 。 0 §5.3 触发器