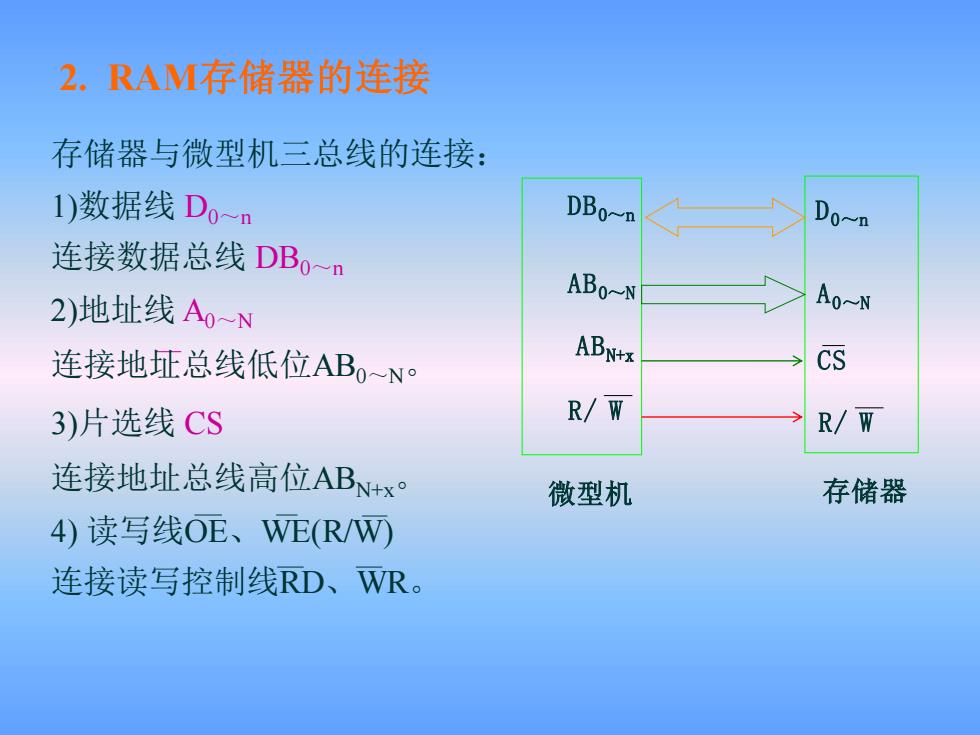

2.RAM存储器的连接 存储器与微型机三总线的连接: 1)数据线Don DBo-n Do-n 连接数据总线DBo~n 2)地址线A~N ABo-N A0一N 连接地址总线低位AB,~N。 ABN+x CS 3)片选线CS R/W R/W 连接地址总线高位ABN+X。 微型机 存储器 4)读写线OE、WE(R/W 连接读写控制线RD、WR

2. RAM存储器的连接 DB 0 ~ n AB 0 ~ N D 0 ~ n A 0 ~ N ABN+x CS R/ W R/ W 微型机 存储器 存储器与微型机三总线的连接: 1)数据线 D 0 ~ n 连接数据总线 DB 0 ~ n 2)地址线 A0 ~ N 连接地址总线低位AB 0 ~ N 。 3)片选线 CS 连接地址总线高位ABN+x 。 4) 读写线OE 、WE(R/W) 连接读写控制线RD 、WR

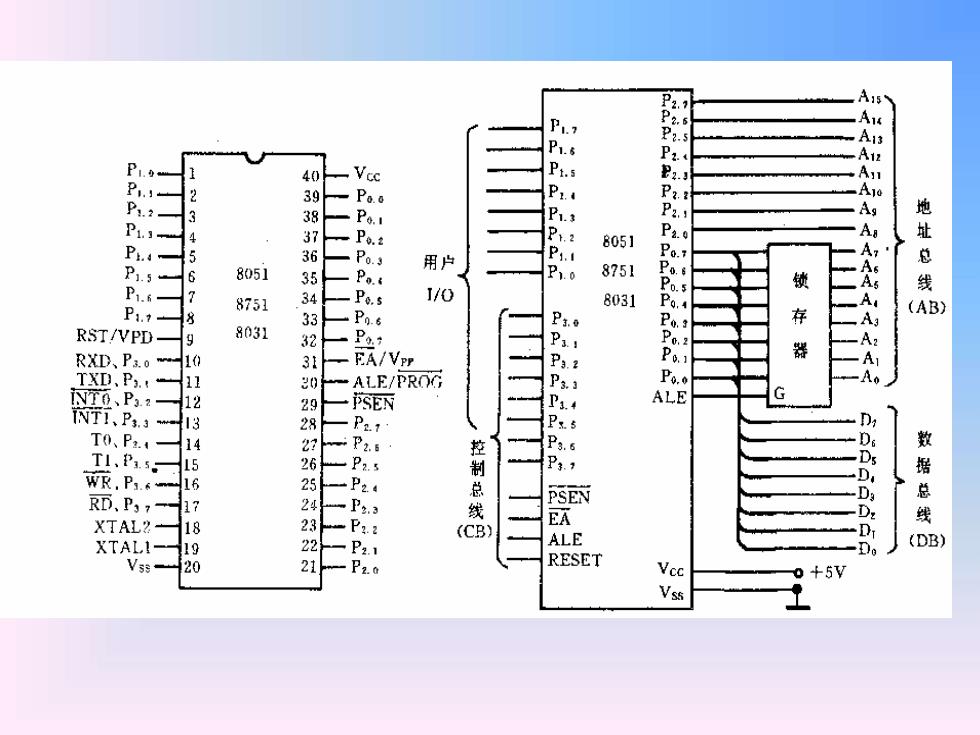

A15 P 40 N 23 3938 地 4 7 Po.e .2 8051 Po.3 用户 Po.7 总 8051 35 Po.d 8751 P1.6 56789 I/0 锁 线 8751 8031 A .6 存 (AB) 3 Po.3 RST/VPD 8031 P A2 RXD、Ps.o 3 A/Vpr 器 A TXD、P. 应、P2 ALE/PROG í、P. 12 SE丽 P.+ ALE G 9 P2.1 P D T0、P3.4 14 P2.8 数 T1.P55 w求.P. P2.5 Ds 16 2 控制总 RD、P3, ) PSEN D0 据总线 XTAL2 Pa.2 XTALI- 9 2322 P2.1 ALE 00 (DB) Vs:- 1 P2.a RESET Vcc 0 +5V

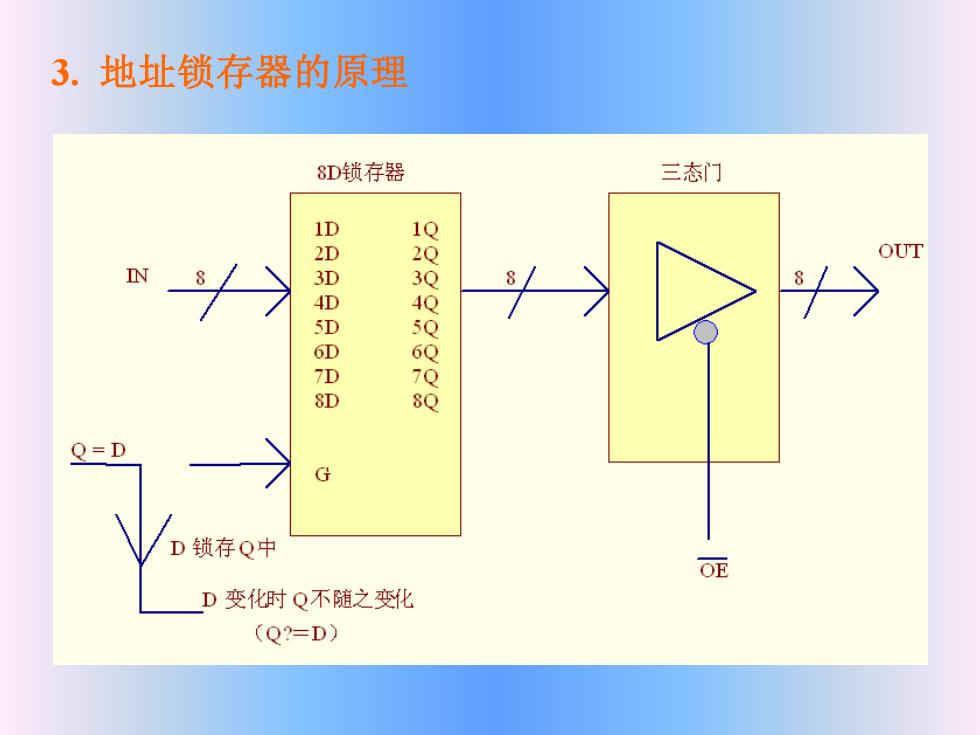

3.地址锁存器的原理 8D锁存器 三态门 1D OUT D 8 4D 0000 99900000 Q=D G 0 锁存Q中 OE D变化时Q不随之变化 (Q?=D)

3. 地址锁存器的原理

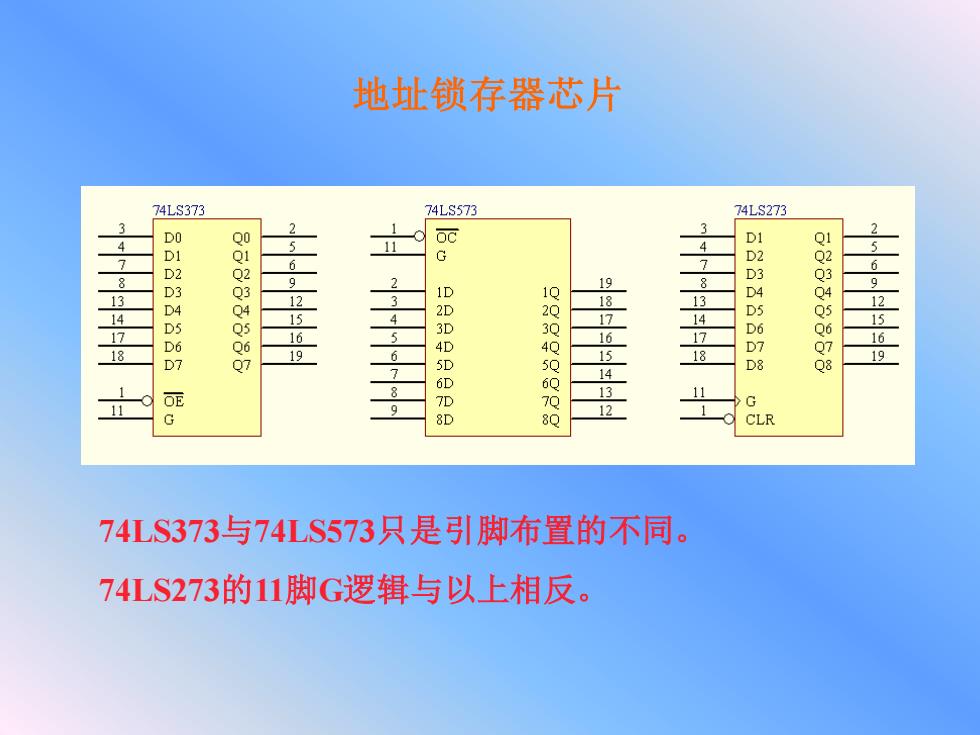

地址锁存器芯片 74LS373 74LS573 74LS273 oc 3 6 4 19 3 90060 18 88988 12 14 4 17 14 15 16 16 18 Q7 8 D05040000 品 15 14 Ds Qs 19 13 11 11 70 G 9 8Q 2 G CLR 74LS373与74LS573只是引脚布置的不同。 74LS273的11脚G逻辑与以上相反

地址锁存器芯片 74LS373与74LS573只是引脚布置的不同。 74LS273的11脚G逻辑与以上相反

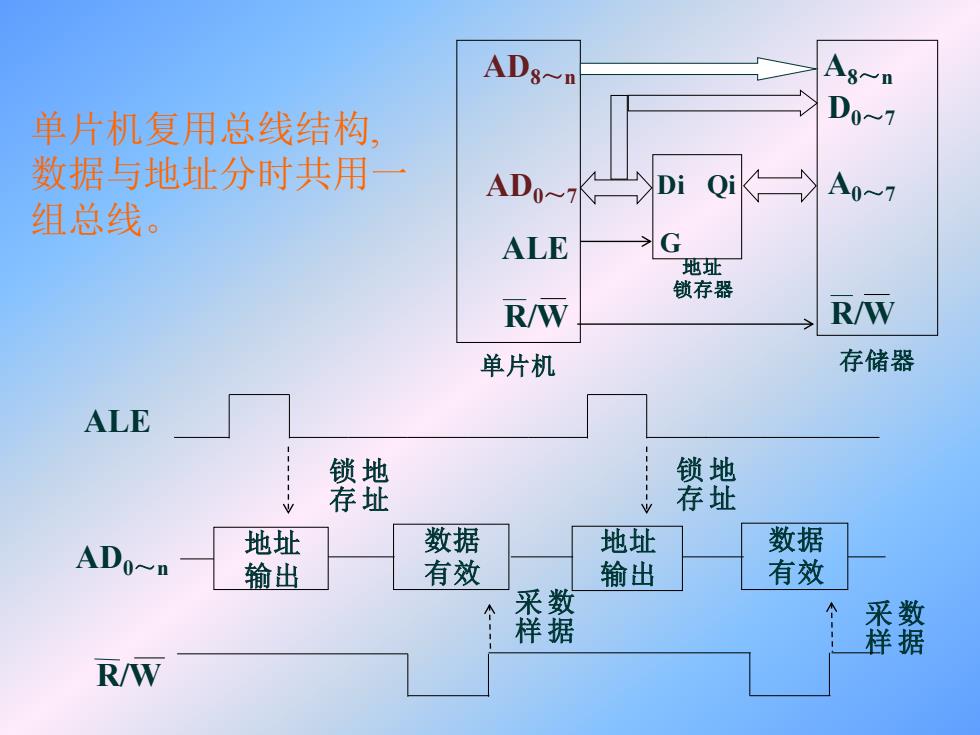

AD8~n A8-n 单片机复用总线结构: D0-7 数据与地址分时共用 AD7水Di Qi〉 A07 组总线。 ALE G 地址 锁存器 R/W R/W 单片机 存储器 ALE 锁地 锁地 存址 ↓存址 ADg≈n 地址 数据 地址 数据 输出 有效 输出 有效 释路 希% R/W

单片机复用总线结构, 数据与地址分时共用一 组总线。 ALE 地 址 锁 存 地 址 锁 存 地址 输出 数据 有效 地址 输出 数据 有效 AD0~n 数 据 采 样 数 据 采 样 R/W 单片机 AD0~7 ALE R/W D0~7 A0~7 R/W 存储器 Di Qi G 地址 锁存器 AD8~n A8~n