总线性能指标 STC 信号线数:即地址总线、数据总线和控制总线三 种总线的根数总和。 总线宽度:是指数据总线的根数,用bit(位)表 示,如8位、16位、32位、64位(也即8根、16根、 32根、64根数据线)。 最大传输率(总线带宽):总线本身所能达到的最 高传输速率,用MB/s(每秒多少兆字节)表示。 例:总线工作频率33.3Mz,总线宽度32位,则最大 传输率=33.3×32/8=132MB/s。 ●】 时钟同步/异步:总线上的数据与时钟同步工作的 总线称为同步总线,与时钟不同步工作的总线称 为异步总线。 负载能力:通常用可连接扩增电路板数来反映总 线的负载能力

总线性能指标 • 信号线数:即地址总线、数据总线和控制总线三 种总线的根数总和。 • 总线宽度:是指数据总线的根数,用bit(位)表 示,如8位、16位、32位、64位(也即8根、16根、 32根、64根数据线)。 • 最大传输率 (总线带宽):总线本身所能达到的最 高传输速率,用MB/s(每秒多少兆字节)表示。 • 例:总线工作频率33.3MHz,总线宽度32位,则最大 传输率= 33.3×32/8=132MB/s。 • 时钟同步/异步:总线上的数据与时钟同步工作的 总线称为同步总线,与时钟不同步工作的总线称 为异步总线。 • 负载能力:通常用可连接扩增电路板数来反映总 线的负载能力

例1 USTC ·题目:某总线在一个总线周期中并行传送4个字节 的数据,假设一个总线周期等于一个总线时钟周 期,总线时钟频率为33Mz,则总线带宽是多少? 加果一企总线周期中并任估送64位数掘总线肚 提示:此题主要是考查对总线带宽的理解。 总线带宽=一次传输的字节数/总线周期 =(总线宽度/8)*总线时钟频率 解:设总线带宽用Dr表示,总线时钟周期用T=1/f 表示,一个总线周期传送的数据量用D表示, (1)根据定义可得Dr=D/T=D×1/T=D×f =4B×33×1000000/s=132MB/s (2)64位=8B,Dr=D×f =8B×66×1000000/s=528MB/s

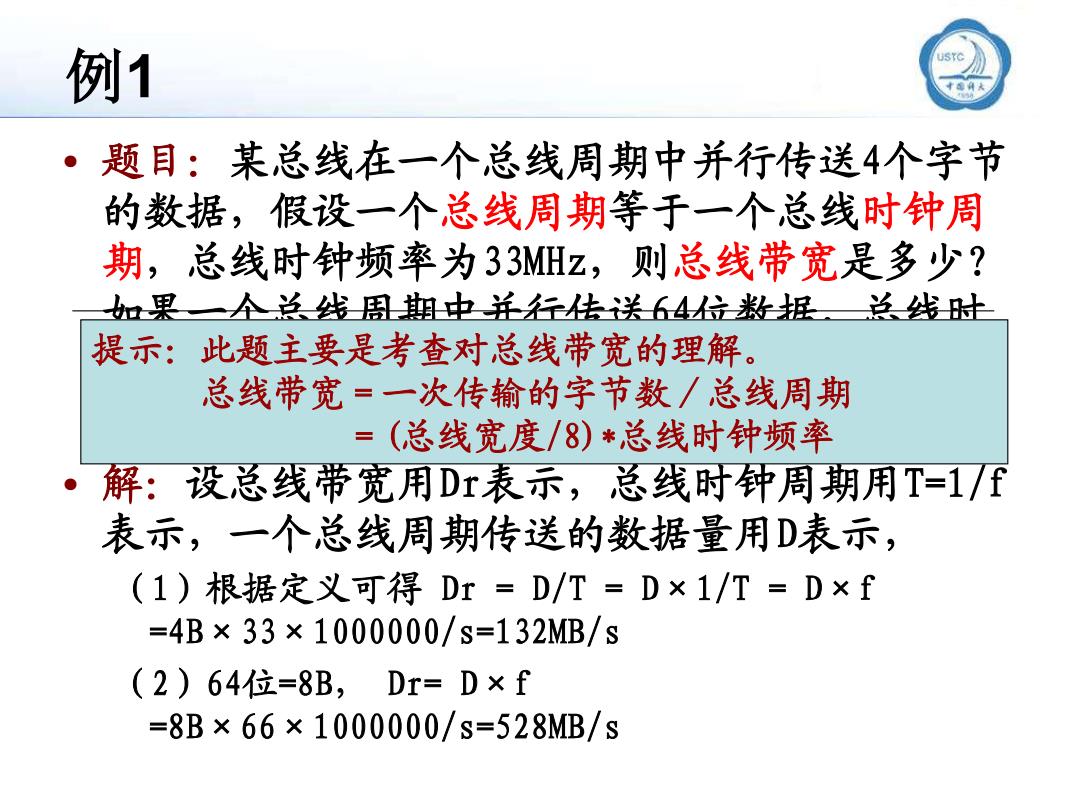

例1 • 题目:某总线在一个总线周期中并行传送4个字节 的数据,假设一个总线周期等于一个总线时钟周 期,总线时钟频率为33MHz,则总线带宽是多少? 如果一个总线周期中并行传送64位数据,总线时 钟频率升为66MHz,则总线带宽是多少? • 解:设总线带宽用Dr表示,总线时钟周期用T=1/f 表示,一个总线周期传送的数据量用D表示, (1)根据定义可得 Dr = D/T = D×1/T = D×f =4B×33×1000000/s=132MB/s (2)64位=8B, Dr= D×f =8B×66×1000000/s=528MB/s 提示:此题主要是考查对总线带宽的理解。 总线带宽=一次传输的字节数/总线周期 =(总线宽度/8)*总线时钟频率

通信速度 ·平均速率=56bits/1000ns=56Mb/s avgrate ·最大速率=8bits/100ns=80Mb/S 一peakrate:包长/发送时间 通道C发送的 =8位 数据位数 100ns 1000ns 时间(ns)

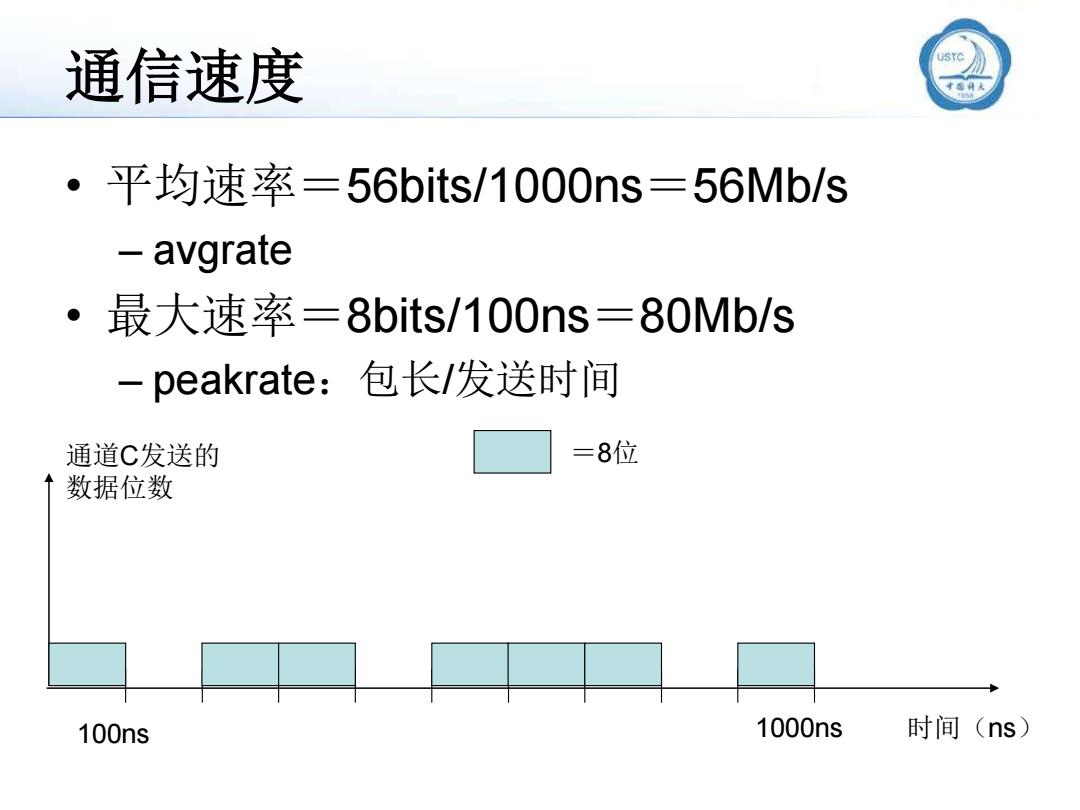

通信速度 • 平均速率=56bits/1000ns=56Mb/s – avgrate • 最大速率=8bits/100ns=80Mb/s – peakrate:包长/发送时间 通道C发送的 数据位数 =8位 100ns 1000ns 时间(ns)

目前流行的总线标准 》 RS232 ISA Accelerated Graphics Port ● EISA 4 PCI Slots 能卡年1果国 0情特0 ·STD PCI Programmable 特丰样转间 2Mbit Flash ROM 0神转ttt0+号+韩转针t针+#n转i0tae程行t1+铺 转0+4材相 AGP SCSI USB 3 ISA Slots

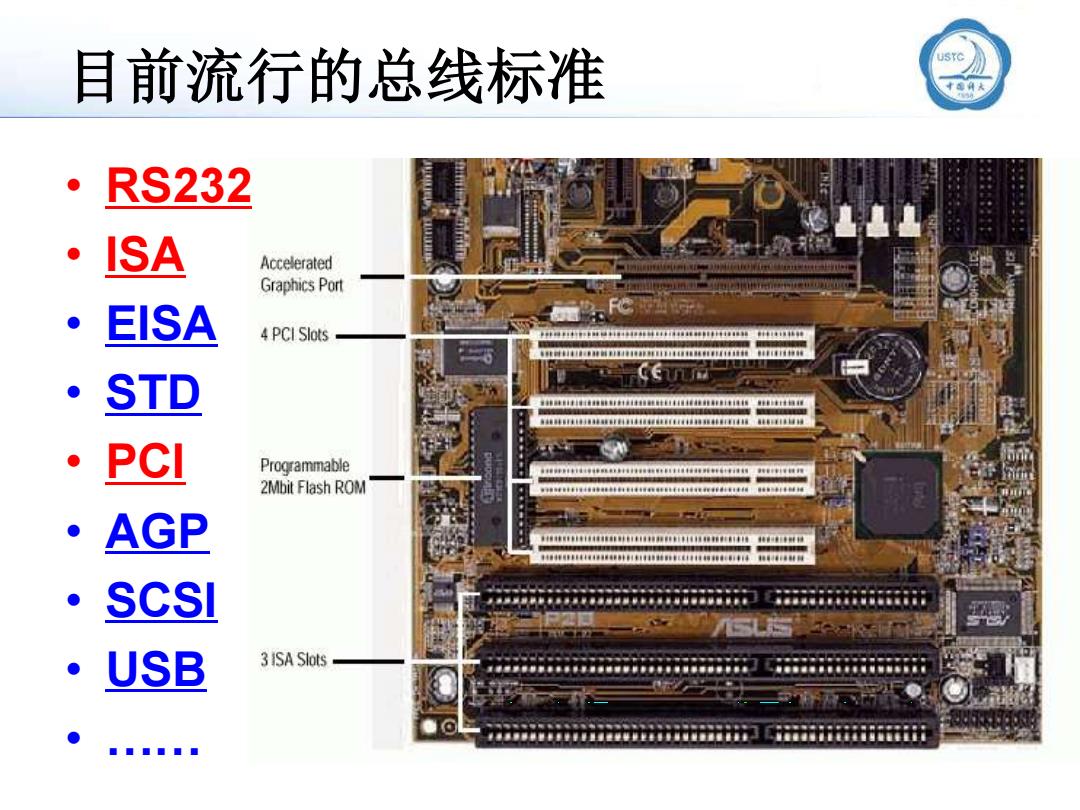

目前流行的总线标准 • RS232 • ISA • EISA • STD • PCI • AGP • SCSI • USB • ……

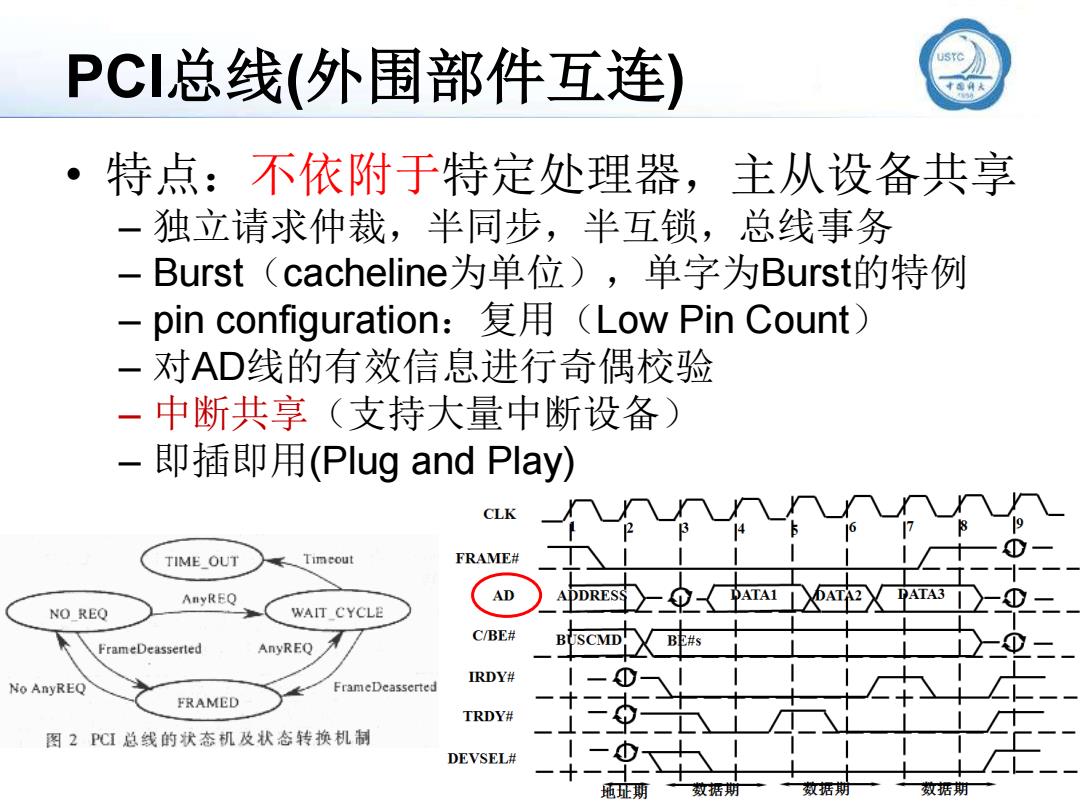

PC总线(外围部件互连) 特点:不依附于特定处理器,主从设备共享 一独立请求仲裁,半同步,半互锁,总线事务 - Burst(cacheline为单位),单字为Burst的特例 - pin configuration:复用(Low Pin Count) 对AD线的有效信息进行奇偶校验 中断共享(支持大量中断设备) - 即插即用(Plug and Play) CLK TIME OUT Timeout FRAME# AnyREQ AD DDRESS NO_REQ WAIT CYCLE C/BE# FrameDeasserted AnyREQ SCMD B#s IRDY# No AnyREQ FrameDeasserted FRAMED TRDY# 图2PCI总线的状态机及状态转换机制 DEVSEL# 地址期 数话期 效活明

PCI总线(外围部件互连) • 特点:不依附于特定处理器,主从设备共享 – 独立请求仲裁,半同步,半互锁,总线事务 – Burst(cacheline为单位),单字为Burst的特例 – pin configuration:复用(Low Pin Count) – 对AD线的有效信息进行奇偶校验 – 中断共享(支持大量中断设备) – 即插即用(Plug and Play)