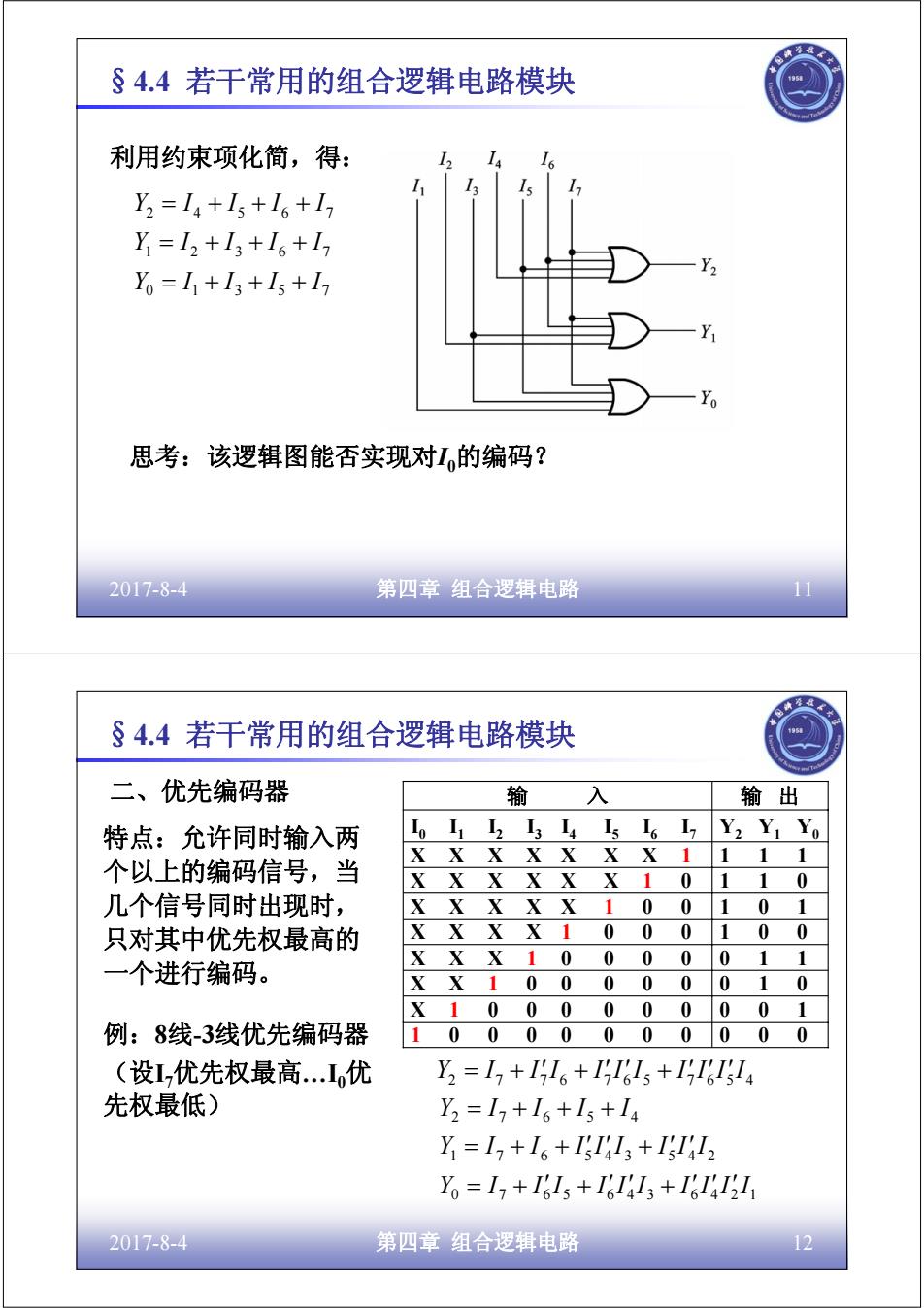

§4.4若干常用的组合逻辑电路模块 利用约束项化简,得: Y2=I4+I+I6+ Y=12+13+16+17 Y=I1+I3+I5+17 思考:该逻辑图能否实现对Ⅱ的编码? 2017-8-4 第四章组合逻辑电路 §4.4若干常用的组合逻辑电路模块 二、优先编码器 输 入 输出 特点:允许同时输入两 I123L456,Y2Y1Y。 个以上的编码信号,当 XX X XXXX 11 11 XXXXX X 1 01 1 0 几个信号同时出现时, XX X XX 1 001 0 1 只对其中优先权最高的 XXXX1000100 一个进行编码。 XXX10000011 X X100000010 1000000001 例:8线-3线优先编码器 1 0000000000 (设1,优先权最高.L优 Y2=1,+1516+II615+15I6I514 先权最低) Y2=I,+I6+I5+I4 Y=12+16+I5I413+I5I412 Y=1+613+I6I413+I6I4I2I 2017-8-4 第四章组合逻辑电路 12

2017-8-4 第四章 组合逻辑电路 11 利用约束项化简,得: 0 1 3 5 7 1 2 3 6 7 2 4 5 6 7 Y I I I I Y I I I I Y I I I I = + + + = + + + = + + + 思考:该逻辑图能否实现对I0的编码? §4.4 若干常用的组合逻辑电路模块 2017-8-4 第四章 组合逻辑电路 12 二、优先编码器 1 0 0 0 0 0 0 0 0 0 0 X 1 0 0 0 0 0 0 0 0 1 X X 1 0 0 0 0 0 0 1 0 X X X 1 0 0 0 0 0 1 1 X X X X 1 0 0 0 1 0 0 X X X X X 1 0 0 1 0 1 X X X X X X 1 0 1 1 0 X X X X X X X 1 1 1 1 Y2 Y1 Y0 I7 I6 I5 I4 I3 I2 I1 I0 输 入 输 出 2 7 7 6 7 6 5 7 6 5 4 Y = I + I′I + I′I′I + I′I′I′I 2 7 6 5 4 Y = I + I + I + I 特点:允许同时输入两 个以上的编码信号,当 几个信号同时出现时, 只对其中优先权最高的 一个进行编码。 例:8线-3线优先编码器 (设I7优先权最高…I0优 先权最低) 0 7 6 5 6 4 3 6 4 2 1 1 7 6 5 4 3 5 4 2 Y I I I I I I I I I I Y I I I I I I I I = + ′ + ′ ′ + ′ ′ ′ = + + ′ ′ + ′ ′ §4.4 若干常用的组合逻辑电路模块

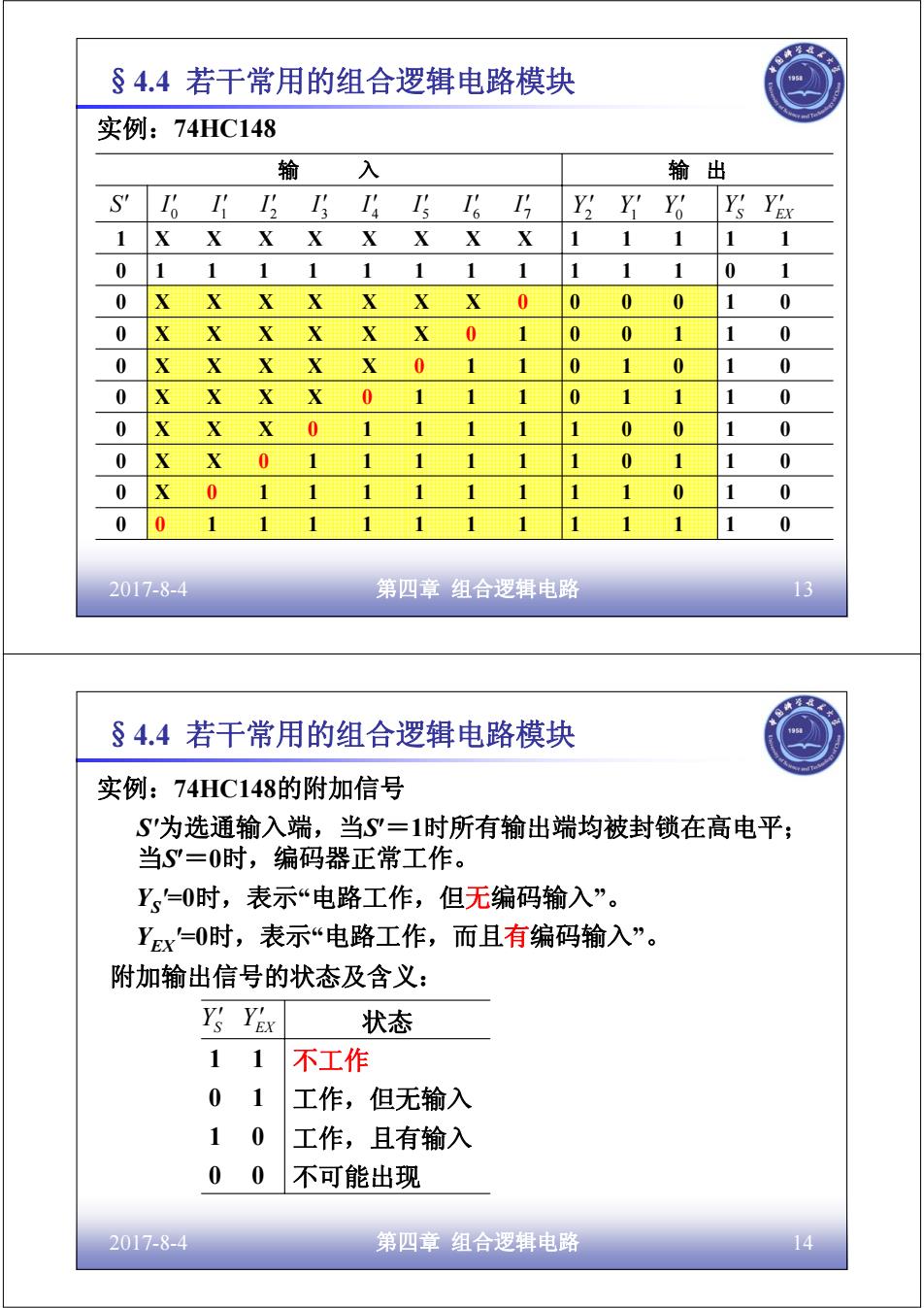

§4.4若干常用的组合逻辑电路模块 实例:74HC148 输 入 输出 S Io I 1II Ig I巧 YY 6 Ys YEx 1 XXXX X X 1 1 1 1 1 0 11 1 1 1 1 1 1 0 1 、0 XXXX X X X 0 0 0 0 1 0 0 XX XX X X 0 1 0 0 1 1 0 0X XX X X 0 1 1 0 0 0 0X XXX 0 1 1 0 1 1 0 0X X X 0 1 0 0 0 0X X 0 0 0 0 X 0 0 0 0 0 0 2017-8-4 第四章组合逻辑电路 13 §4.4若干常用的组合逻辑电路模块 实例:74HC148的附加信号 S'为选通输入端,当S=1时所有输出端均被封锁在高电平; 当S=0时,编码器正常工作。 Y=0时,表示“电路工作,但无编码输入”。 Yx'=0时,表示“电路工作,而且有编码输入”。 附加输出信号的状态及含义: Ys YEx 状态 1 1 不工作 01 工作,但无输入 10 工作,且有输入 00 不可能出现 2017-8-4 第四章组合逻辑电路 14

2017-8-4 第四章 组合逻辑电路 13 0 X X X X X X X 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 X X X X X X X 0 0 1 1 1 1 1 1 1 1 0 0 X 0 1 1 1 1 1 1 0 1 0 X X 0 1 1 1 1 1 0 0 0 X X X 0 1 1 1 0 1 1 0 X X X X 0 1 1 0 1 0 0 X X X X X 0 1 0 0 1 1 X X X X X X X 1 1 1 输 入 输 出 0 1 2 3 4 5 6 7 S′ I′ I′ I′ I′ I′ I′ I′ I′ 2 1 0 Y′ Y′ Y′ YS YEX ′ ′ 实例:74HC148 §4.4 若干常用的组合逻辑电路模块 2017-8-4 第四章 组合逻辑电路 14 S'为选通输入端,当S′=1时所有输出端均被封锁在高电平; 当S′=0时,编码器正常工作。 YS '=0时,表示“电路工作,但无编码输入”。 YEX '=0时,表示“电路工作,而且有编码输入”。 实例:74HC148的附加信号 0 0 不可能出现 1 0 工作,且有输入 0 1 工作,但无输入 1 1 不工作 YS ′ YEX ′ 状态 附加输出信号的状态及含义: §4.4 若干常用的组合逻辑电路模块

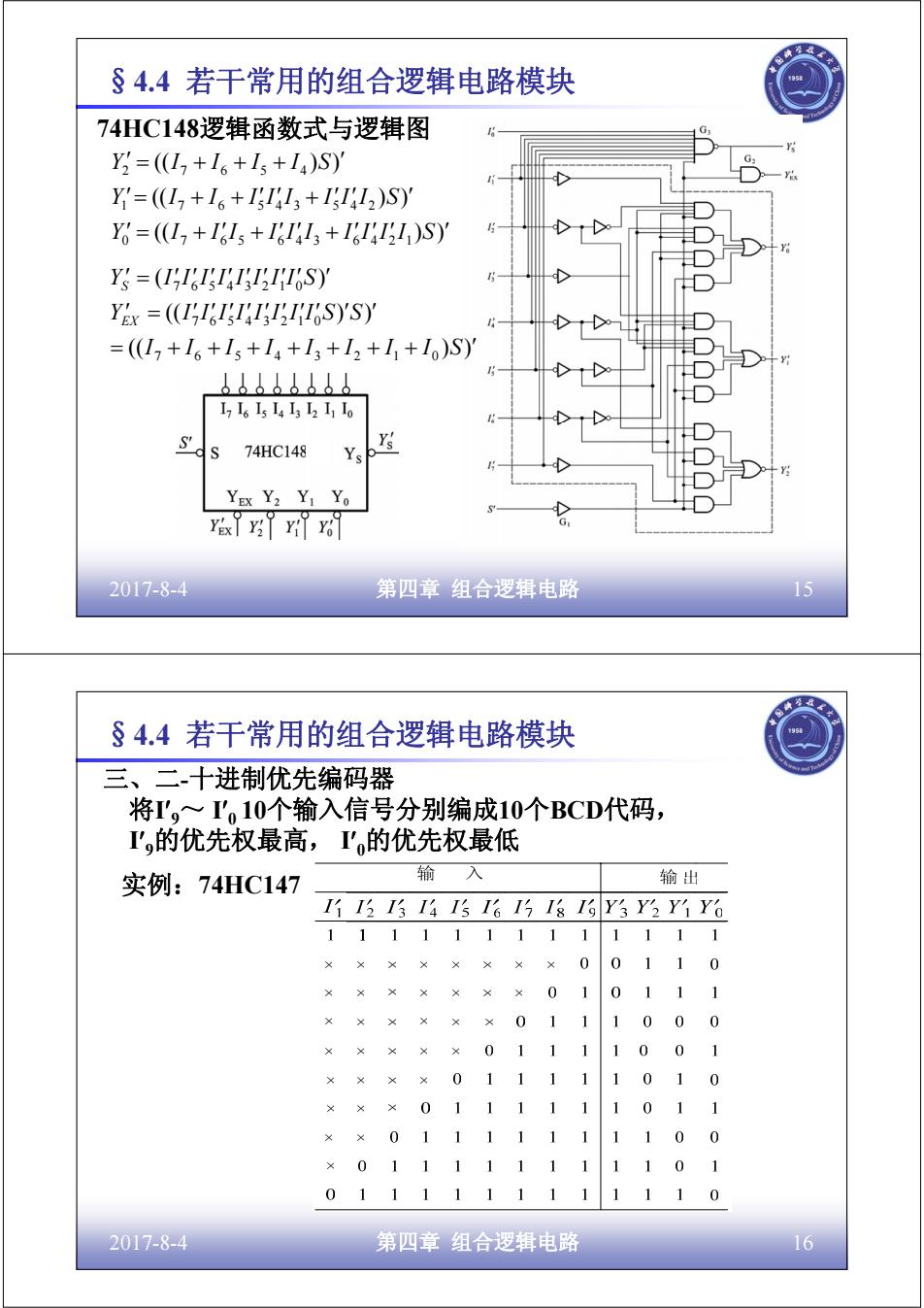

§4.4若干常用的组合逻辑电路模块 74HC148逻辑函数式与逻辑图 Y=(I,+I6+I+I4)S)' Y'=(L,+16+I5I4L3+I5I412)S) Y%=(L,+I6L+I6I4L3+I6I4I51)S) Ys=(IHIoS) YEx =((I1I1HIS)'S)' =(I,+16+I5+I4+13+12+11+1o)S)y ↓b6b↓b↓& I26134321o 74HC148 YEX Y2 Y1 Yo a 2017-8-4 第四章组合逻辑电路 15 §4.4若干常用的组合逻辑电路模块 三、二十进制优先编码器 将,~I'o10个输入信号分别编成10个BCD代码, '的优先权最高,'的优先权最低 实例:74HC147 输入 输出 I 12 I5 14 I5 16 19 I8 IY3 Y2Y Yo 111111111 1111 0 01 1 0 0 011 × 1 1 1 00 0 1 0 0 1 1 01 0 1 0 1 1 1 0 0 1 0 1 01 1 0 2017-8-4 第四章组合逻辑电路 16

2017-8-4 第四章 组合逻辑电路 15 (( ) ) (( ) ) (( ) ) 0 7 6 5 6 4 3 6 4 2 1 1 7 6 5 4 3 5 4 2 2 7 6 5 4 ′ = + ′ + ′ ′ + ′ ′ ′ ′ ′= + + ′ ′ + ′ ′ ′ ′ = + + + ′ Y I I I I I I I I I I S Y I I I I I I I I S Y I I I I S (( ) ) (( ) ) ( ) 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 = + + + + + + + ′ ′ = ′ ′ ′ ′ ′ ′ ′ ′ ′ ′ ′ = ′ ′ ′ ′ ′ ′ ′ ′ ′ I I I I I I I I S Y I I I I I I I I S S Y I I I I I I I I S EX S 74HC148逻辑函数式与逻辑图 §4.4 若干常用的组合逻辑电路模块 2017-8-4 第四章 组合逻辑电路 16 三、二-十进制优先编码器 将I′ 9~ I′ 0 10个输入信号分别编成10个BCD代码, I′ 9的优先权最高, I′ 0的优先权最低 实例:74HC147 §4.4 若干常用的组合逻辑电路模块

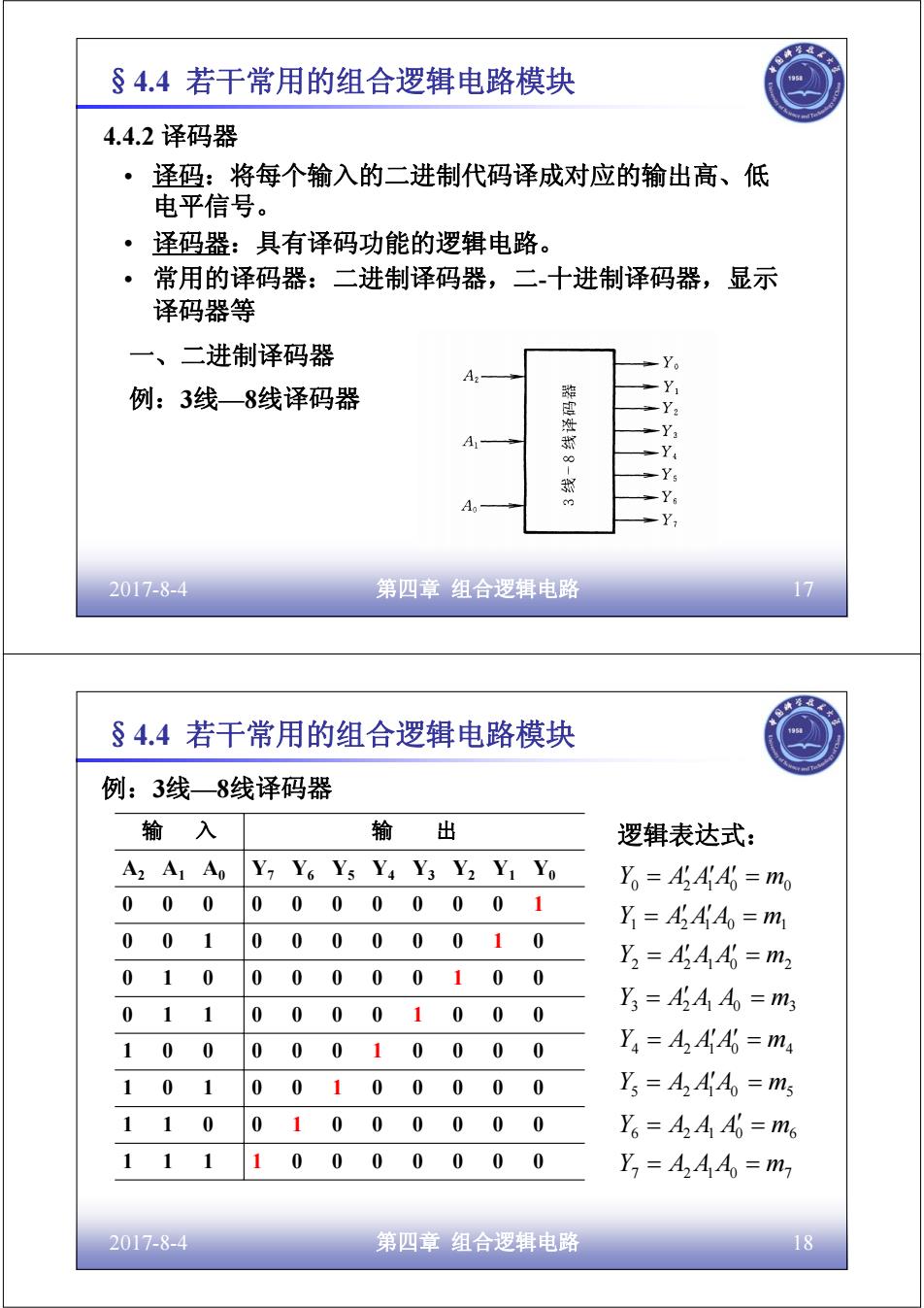

§4.4若干常用的组合逻辑电路模块 4.4.2译码器 。 译码:将每个输入的二进制代码译成对应的输出高、低 电平信号。 译码器:具有译码功能的逻辑电路。 常用的译码器:二进制译码器,二十进制译码器,显示 译码器等 一、二进制译码器 Y。 例:3线—8线译码器 Y: Y Y 2017-8-4 第四章组合逻辑电路 §4.4若干常用的组合逻辑电路模块 例:3线一—8线译码器 输入 输 出 逻辑表达式: A2 A1 Ao Y7 Y6 Y5 Y4 Y3 Y2 YI Yo Y。=AAA=m0 000 00 0 00001 Y=AAAo m 00 1 00 0 00010 Y,=AA Ao m2 0 10 0 0 0 0 01 0 0 Y3=A2A Ao ms 0 11 0 0 0 10 00 100 00 0 00 00 Y=A AAo=m 10 1 0 0 0 00 00 Ys =AAAo=ms 1 1 0 0 1 0 0 00 00 Yo=AA Ao=m 111 1 0 0 000 00 Y=AA Ao=m 2017-8-4 第四章组合逻辑电路 18

2017-8-4 第四章 组合逻辑电路 17 4.4.2 译码器 • 译码:将每个输入的二进制代码译成对应的输出高、低 电平信号。 • 译码器:具有译码功能的逻辑电路。 • 常用的译码器:二进制译码器,二-十进制译码器,显示 译码器等 一、二进制译码器 例:3线—8线译码器 §4.4 若干常用的组合逻辑电路模块 2017-8-4 第四章 组合逻辑电路 18 例:3线—8线译码器 1 1 1 1 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 输 入 输 出 7 2 1 0 7 6 2 1 0 6 5 2 1 0 5 4 2 1 0 4 3 2 1 0 3 2 2 1 0 2 1 2 1 0 1 0 2 1 0 0 Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m = = = ′ = = ′ = = ′ ′ = = ′ = = ′ ′ = = ′ ′ = = ′ ′ ′ = 逻辑表达式: §4.4 若干常用的组合逻辑电路模块

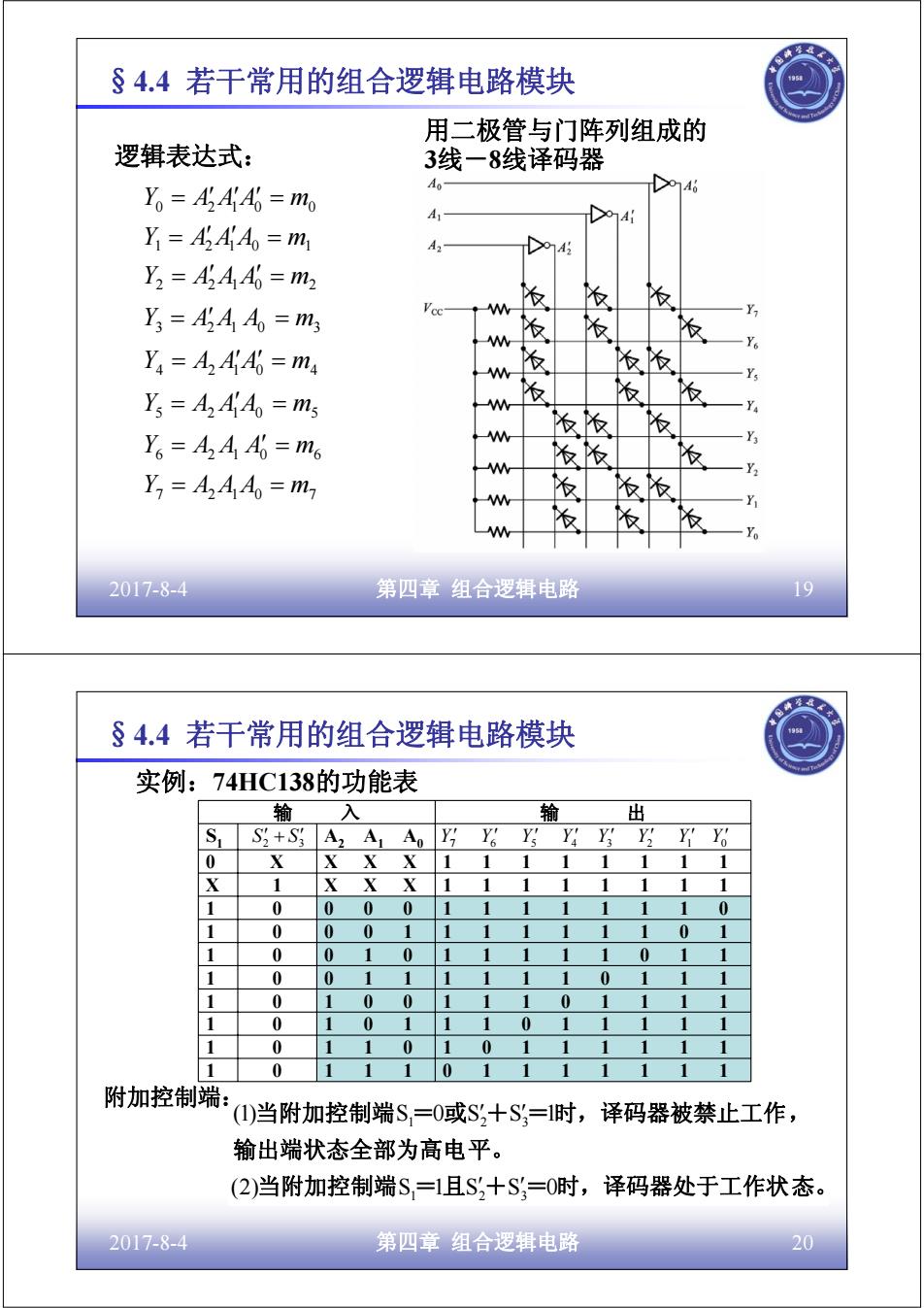

§4.4若干常用的组合逻辑电路模块 用二极管与门阵列组成的 逻辑表达式: 3线一8线译码器 Ao 0A6 Y。=AAA6=mo A Y=A2AAo =m Y2=AA Ao=mz Y3=AA Ao =m3 Y Yo Ya=A AAo ma Y Ys =A2 AAo =ms W Y Y。=A,A1A=m。 Y=AA Ao=m Yo 2017-8-4 第四章组合逻辑电路 19 §4.4若干常用的组合逻辑电路模块 实例:74HC138的功能表 输 入 输 出 S S2+ A2 A Ao 0 X XXX 1 1 1 1 1 1 1 X 1 XXX 1 1 1 1 1 1 0 0 00 1 1 1 0 1 0 001 1 1 1 1 0 1 1 0 010 1 1 0 1 0 0 11 1 0 1 1 1 0 00 1 1 0 1 0 0 1 0 0 0 1 0 0 附加控制端: (①)当附加控制端S,=0或S,十S,=1时,译码器被禁止工作, 输出端状态全部为高电平。 (2)当附加控制端S,=1且S,十S,=0时,译码器处于工作状态。 2017-8-4 第四章组合逻辑电路 20

2017-8-4 第四章 组合逻辑电路 19 §4.4 若干常用的组合逻辑电路模块 逻辑表达式: 用二极管与门阵列组成的 3线-8线译码器 7 2 1 0 7 6 2 1 0 6 5 2 1 0 5 4 2 1 0 4 3 2 1 0 3 2 2 1 0 2 1 2 1 0 1 0 2 1 0 0 Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m Y A A A m = = = ′ = = ′ = = ′ ′ = = ′ = = ′ ′ = = ′ ′ = = ′ ′ ′ = 2017-8-4 第四章 组合逻辑电路 20 输出端状态全部为高电平。 (1)当附加控制端S1 =0或S′ 2 +S′ 3 =1时,译码器被禁止工作, 实例:74HC138的功能表 1 1 1 1 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 0 1 0 1 1 1 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 1 1 1 0 0 1 0 1 1 1 1 1 0 1 1 0 0 0 1 1 1 1 1 1 1 0 1 0 0 0 0 1 1 1 1 1 1 1 X 1 X X X 1 1 1 1 1 1 1 0 X X X X 1 1 1 1 1 1 1 A2 A1 A0 S1 输 入 输 出 S2 S3 ′ + ′ 7 6 5 4 3 2 1 0 Y′ Y′ Y′ Y′ Y′ Y′ Y′ Y′ 附加控制端: (2)当附加控制端S1 =1且S′ 2 +S′ 3 =0时,译码器处于工作状态。 §4.4 若干常用的组合逻辑电路模块