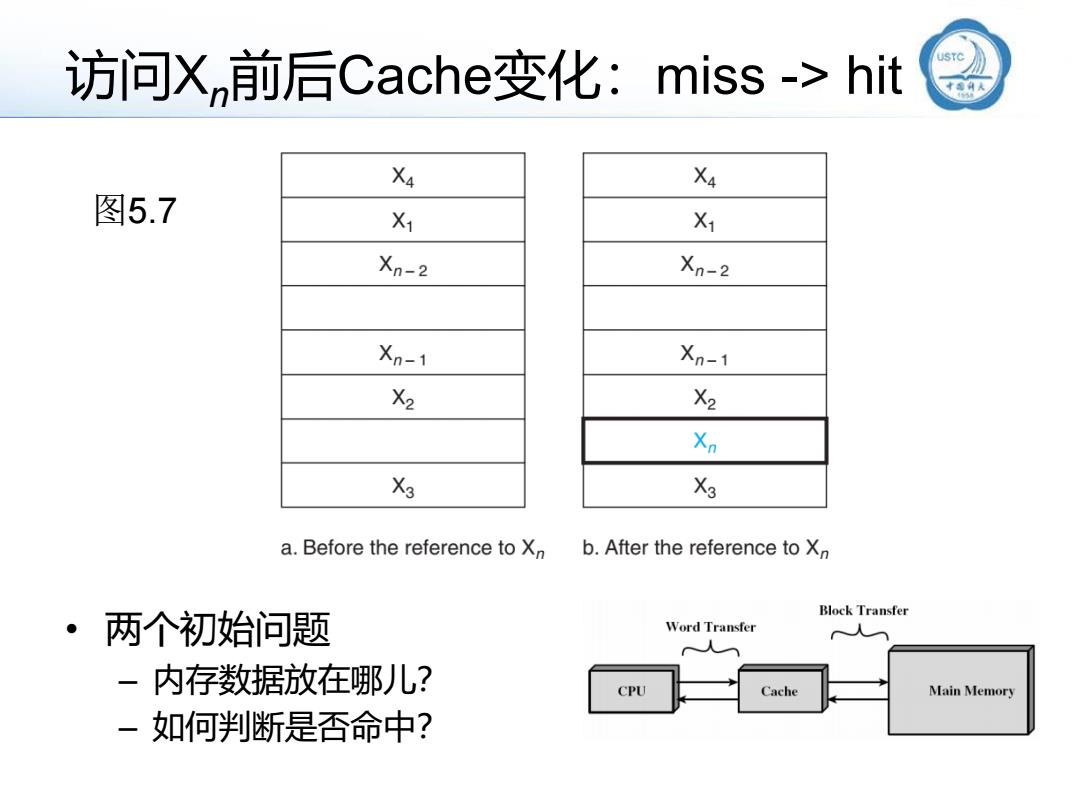

访问X,前后Cache变化:miss->hit s》 X4 X4 图5.7 X1 X1 Xn-2 Xn-2 Xn-1 Xn-1 X2 X2 Xn X3 X3 a.Before the reference to Xn b.After the reference to Xn Block Transfer ·两个初始问题 Word Transfer 人 人 一内存数据放在哪儿? CPU Cache Main Memory - 如何判断是否命中?

访问Xn前后Cache变化:miss -> hit • 两个初始问题 – 内存数据放在哪儿? – 如何判断是否命中? 图5.7

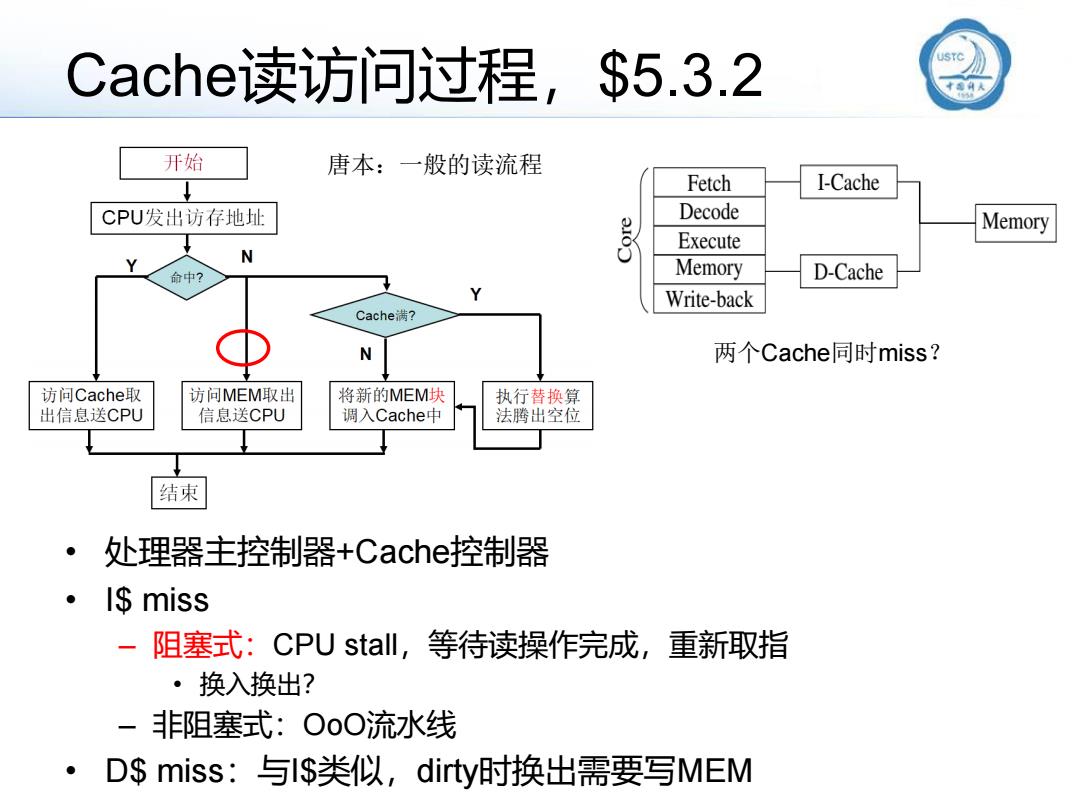

Cache读访问过程,$5.3.2 USTC 开始 唐本:一般的读流程 Fetch I-Cache CPU发出访存地址 Decode Memory Execute N 命中? Memory D-Cache Write-back Cache满? N 两个Cache同时miss? 访问Cache.取 访问MEM取出 将新的MEM块 执行替换算 出信息送CPU 信息送CPU 调入Cache中 法腾出空位 结束 处理器主控制器+Cache控制器 I$miss -阻塞式:CPU stall,等待读操作完成,重新取指 ·换入换出? -非阻塞式:OoO流水线 D$miss:与l$类似,dity时换出需要写MEM

Cache读访问过程,$5.3.2 • 处理器主控制器+Cache控制器 • I$ miss – 阻塞式:CPU stall,等待读操作完成,重新取指 • 换入换出? – 非阻塞式:OoO流水线 • D$ miss:与I$类似,dirty时换出需要写MEM 唐本:一般的读流程 两个Cache同时miss?

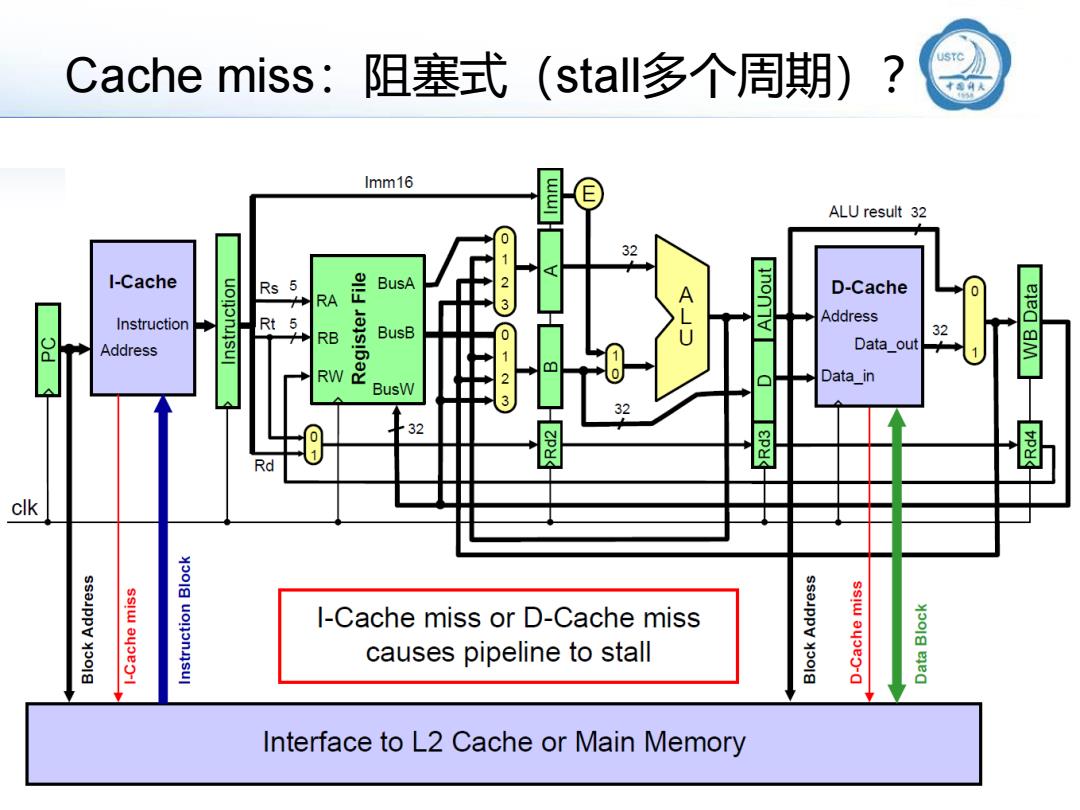

Cache miss:阻塞式(stall多个周期) Imm16 E ALU result 32 32 I-Cache Rs BusA 0123 D-Cache RA Instruction Rt 5 inon7 Address RB BusB 32 Address Data_out RW Data_in BusW 23 32 32 01 Rd 圜 clk I-Cache miss or D-Cache miss causes pipeline to stall Interface to L2 Cache or Main Memory

Cache miss:阻塞式(stall多个周期)?

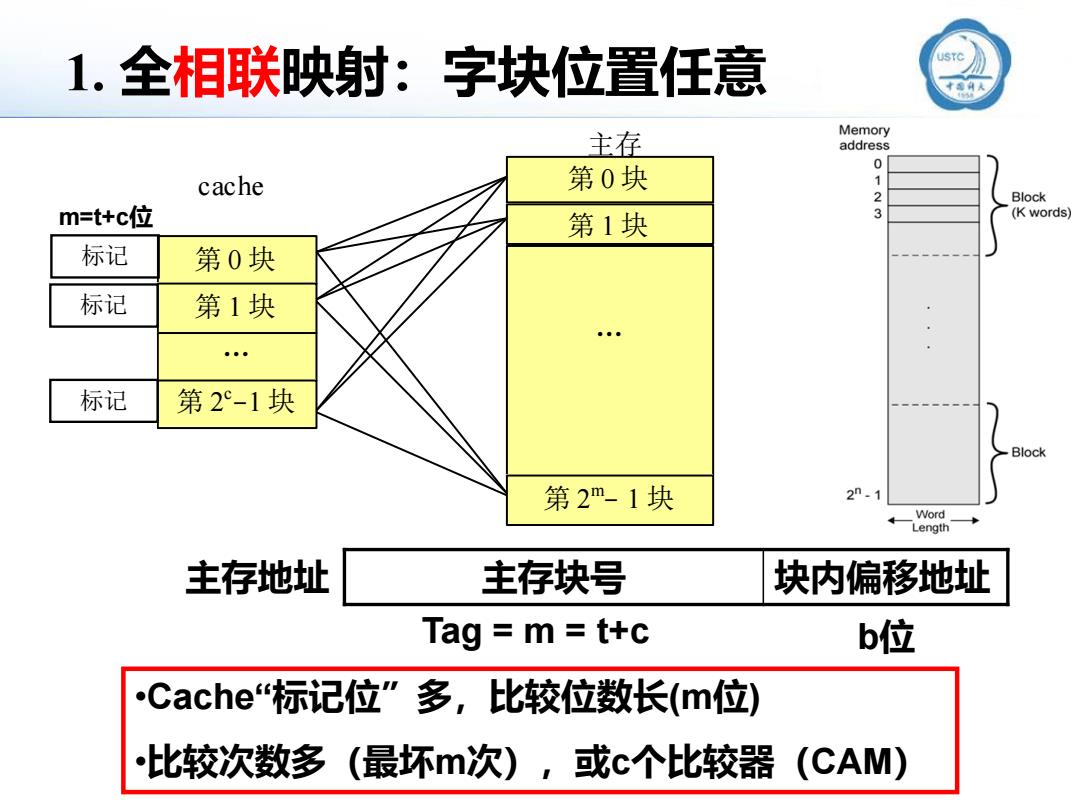

1.全相联映射:字块位置任意 e》 主存 Memory address cache 第0块 0 Block m=ttc位 第1块 3 (K words) 标记 第0块 标记 第1块 标记 第2-1块 Block 第2m-1块 2n.1 Word 主存地址 主存块号 块内偏移地址 Tag m=t+c b位 Cache“标记位”多,比较位数长m位) 比较次数多 (最坏m次),或c个比较器 (CAM)

1. 全相联映射:字块位置任意 主存 cache 第 0 块 第 1 块 第 0 块 … 第 1 块 … 第 2 c -1 块 第 2 m - 1 块 标记 标记 标记 主存地址 主存块号 块内偏移地址 Tag = m = t+c b位 m=t+c位 •Cache“标记位”多,比较位数长(m位) •比较次数多(最坏m次),或c个比较器(CAM)

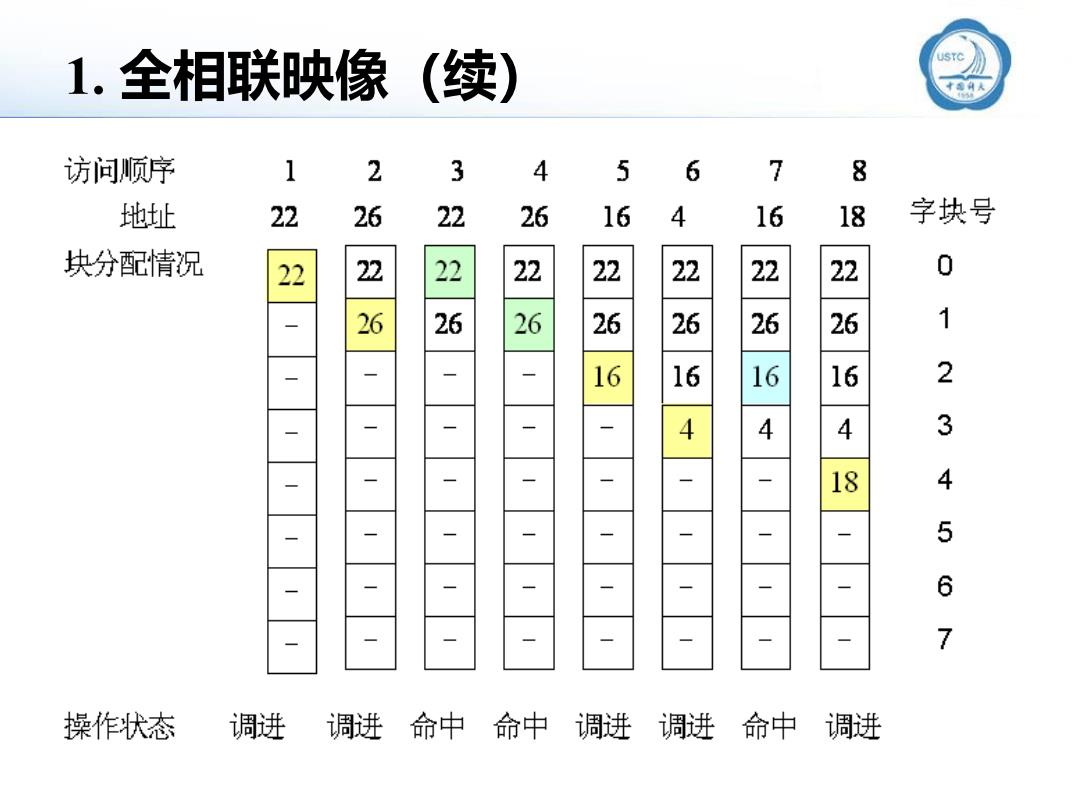

1.全相联映像(续) 》 访问顺序 1 2 3 4 5 6 7 8 地址 22 26 22 26 16 4 16 18 字块号 块分配情况 22 22 22 22 22 22 22 22 0 26 26 26 26 26 26 26 1 16 16 16 16 2 4 4 3 18 4 5 6 7 操作状态 调进 调进命中命中调进 调进命中 调进

1. 全相联映像(续)