命中、不命中、命中率 USTC Cache命中(hit) Block Transfer Word Transfer 人 人A 一欲访问的数据在缓存中 CPU Cache Main Memory -命中时间 ● Cache?不命中(miss,缺失) -CPU欲访问的数据不在Cache内,或数据无效 ·需将数据所在主存块(block)一次性调入 。 CPU可阻塞(blocking,stall) 或非阻塞 (non-blocking) 失效损失(penalty):时间=mem->cache->cpu 命中率(Hit rate) -CPU要访问的信息已在Cache内的比率。 ·通常用命中率来衡量Cache的效率。 ·不命中率(Miss rate)

命中、不命中、命中率 • Cache命中(hit) – 欲访问的数据在缓存中 – 命中时间 • Cache不命中(miss, 缺失) – CPU欲访问的数据不在Cache内,或数据无效 • 需将数据所在主存块(block)一次性调入 • CPU可阻塞(blocking,stall)或非阻塞(non-blocking) – 失效损失(penalty):时间 = mem->cache->cpu • 命中率(Hit rate) – CPU要访问的信息已在Cache内的比率。 • 通常用命中率来衡量Cache的效率。 • 不命中率(Miss rate)

例:Cache基本结构参数 》 块(行)大小 1 32字 命中时间 1一2时钟周期(常规为1) 失配时间 8一100时钟周期 (访问时间) (6一60时钟周期) (传送时间) (2一40时钟周期) 失配率 0.5%—10% Cache:容量 1KB—1MB Block Transfer Word Transfer 人 .Cache-line size match the width of 人 the DRAM simplified the design. CPU Cache Main Memory

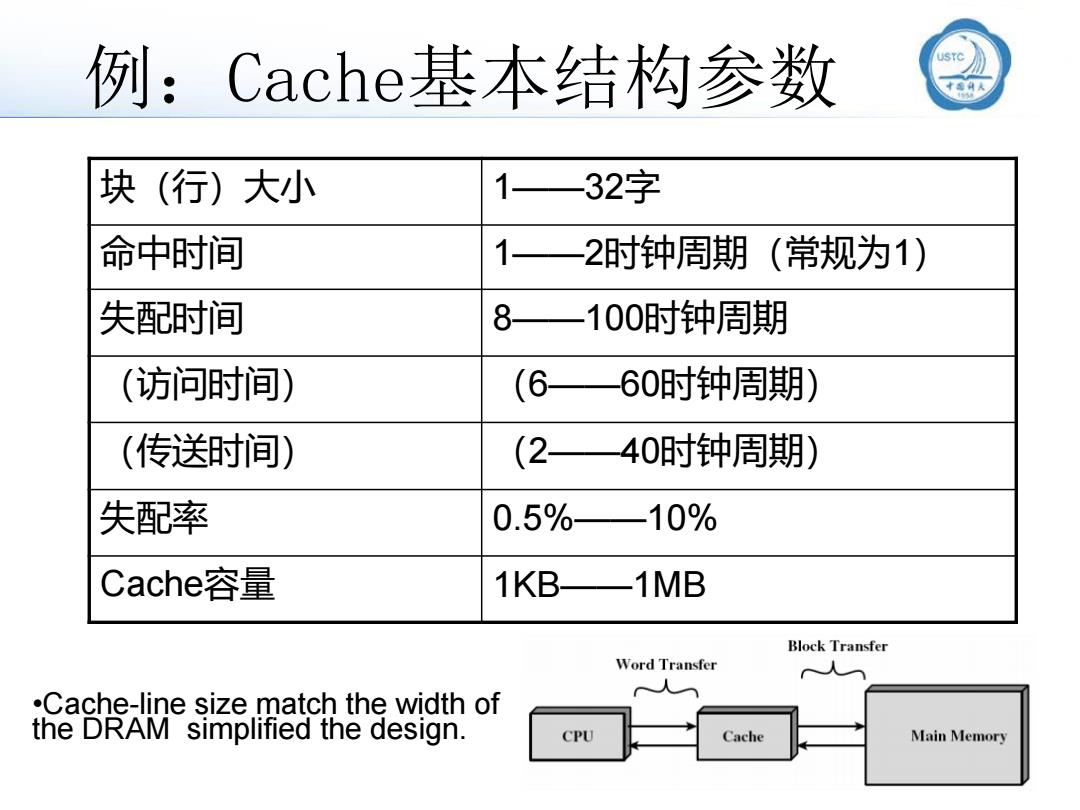

例:Cache基本结构参数 块(行)大小 1——32字 命中时间 1——2时钟周期(常规为1) 失配时间 8——100时钟周期 (访问时间) (6——60时钟周期) (传送时间) (2——40时钟周期) 失配率 0.5%——10% Cache容量 1KB——1MB •Cache-line size match the width of the DRAM simplified the design

内存分块(bock,字块),一块多字 Memory address Data Block identification 00000000000000000000 a29a28 a27.a4a3!a2a1a0 00000000000000000001 Block 0 00000000000000000010 00000000000000000011 4个data Bits identifying block Bits identifying 00000000000000000100 offset 00000000000000000101 00000000000000000110 Block 1 10100101011010010110 00000000000000000111 00000000000000001000 B1 oek ID=169.38110 Offset of 2 into block 00000000000000001001 Block 2 00000000000000001010 00000000000000001011 Each gray block (one data) represents an addressable 一个Cache block(4个data) memory location containing a word 11111111111111111100 11111111111111111101 Bl0ck220-2-1=262,143 11111111111111111110 11111111111111111111 字地址 块大小多少合适?

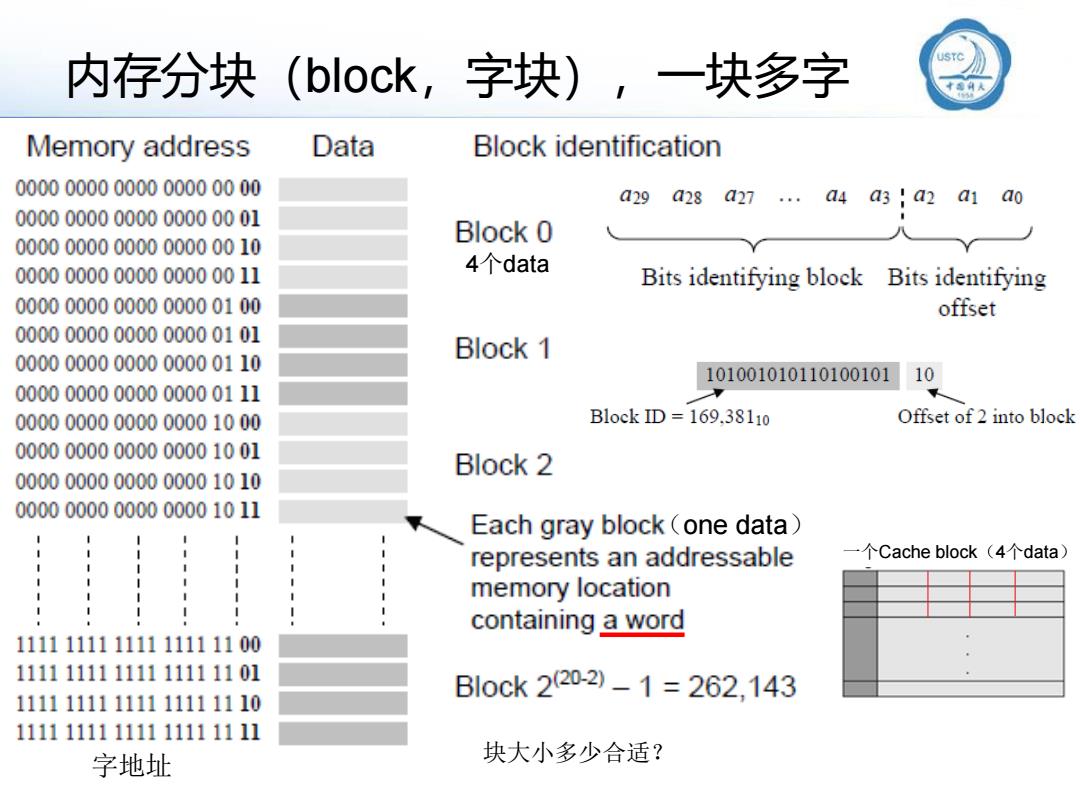

内存分块(block,字块),一块多字 块大小多少合适? 一个Cache block(4个data) 4个data (one data) 字地址

Cache/Main Memory Structure:行/字块 Line Memory Number Tag Block address 0 字地址0 1 1 字块 2 2 Block 3 (K words) C-1 Block Length (K Words) (a)Cache 内存分块(字块),Cache分行,一行一块(字块) Cache line (Cache Block)size Mem Block size Main memory 2n words 2n/K blocks Block Cache has C lines of K words each Tag-to identifies line 2n.1 Word Line way Length (b)Main memory

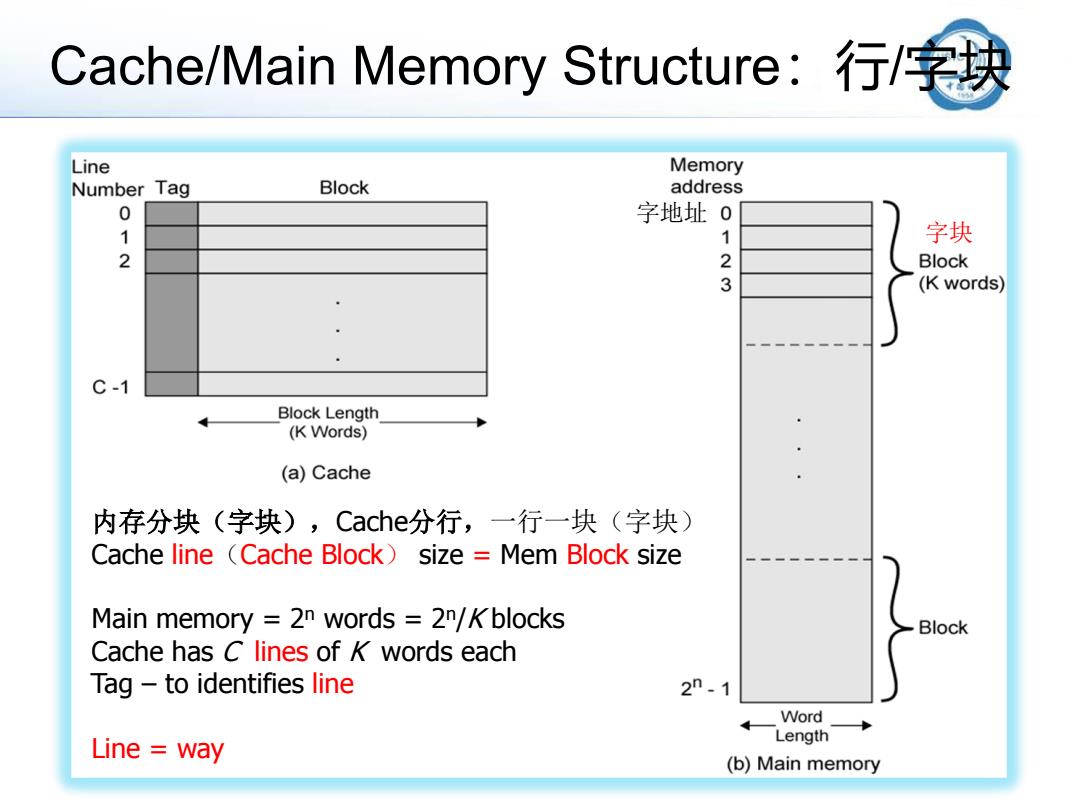

Cache/Main Memory Structure:行/字块 内存分块(字块),Cache分行,一行一块(字块) Cache line(Cache Block) size = Mem Block size Main memory = 2n words = 2n /K blocks Cache has C lines of K words each Tag – to identifies line Line = way 字地址 字块

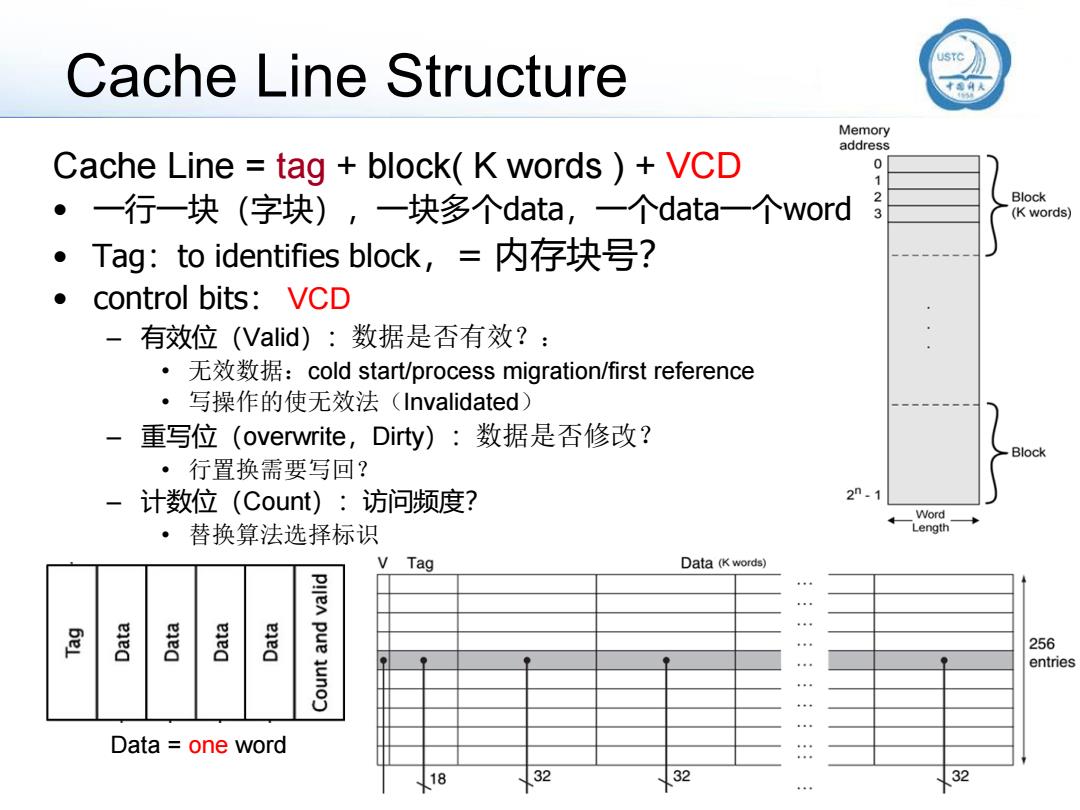

Cache Line Structure USTC Memory address Cache Line tag block(K words )VCD 0 1 ·一行一块(字块),一块多个data,一个data一个word 23 Block (K words) ● Tag:to identifies block,=内存块号? control bits:VCD - 有效位(Valid):数据是否有效?: ·无效数据:cold start/process migration/,first reference ·写操作的使无效法(Invalidated) - 重写位(overwrite,Dirty):数据是否修改? Block ·行置换需要写回? -计数位(Count):访问频度? 2n.1 Word 4 ·替换算法选择标识 Length Tag Data (K words) 是 256 entries Data one word X18

Cache Line Structure Cache Line = tag + block( K words ) + VCD • 一行一块(字块),一块多个data,一个data一个word • Tag:to identifies block,= 内存块号? • control bits: VCD – 有效位(Valid):数据是否有效?: • 无效数据:cold start/process migration/first reference • 写操作的使无效法(Invalidated) – 重写位(overwrite,Dirty):数据是否修改? • 行置换需要写回? – 计数位(Count):访问频度? • 替换算法选择标识 Data = one word